基于FPGA 的电子画图板设计

路红娟,蒋伟

(无锡工艺职业技术学院,江苏 宜兴 214206)

0 引言

随着科技的发展以及环保的需求,现在各行各业逐渐向无纸化时代进军,如办公无纸化,无纸实训室等等。所以现在美术专业的学生,小孩子的涂鸦学画画等,都转向了无纸环保的电子画图板。现在市场上电子画图板都是在电脑上安装画图软件来实现的,而电脑一来昂贵,二来笨重不易携带。为此,本文设计了一种基于FPGA 的电子画图板,可弥补电脑画图板的上述不足,特点是便携易带,成本低廉。由于是纯硬件设计,所以响应快,稳定性高。使用时只要接上鼠标和带VGA 的显示器就可以工作。

1 系统说明

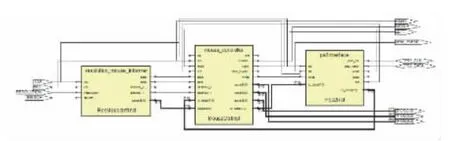

如图1 所示,本作品的硬件结构分为三大部分:基于FPGA 的Spartan 3E-100[1-3]硬件电路板,带有VGA 接口的显示器以及Ps/2 口的鼠标。

图1 结构框图

FPGA 的内部硬件VHDL 语言编程分为4 个部分:1)鼠标驱动模块,FPGA 来检测鼠标的位置以及左中右键的按键信息。2)显示屏的VGA 显示模块,此模块接收显示颜色的位置和信息,并通过VGA 硬件接口显示。3)存储模块,分为ROM 和双口RAM 两个部分。ROM 用于显示初始界面的“无锡工艺学院”六个字;双口RAM 用于实时记录画图的数据信息,并将其颜色信息传送给VGA 接口显示模块。4)控制和算法模块:此模块既可协调各个逻辑程序的运行,又通过巧妙的算法对读写存储地址的运算,解决了FPGA Spartan 3E-100 的资源不足,基本满足了对整个屏幕的画画或写字操作要求。

2 原理说明

原理如图2 所示,DispCtrl 是显示模块,用于接受鼠标的位置信号,并且从RAM 和ROM 读出数据,通过RGB 端口在显示屏上正确的显示;MouseRefComp 是鼠标控制模块,作用是将鼠标的位置信息,左中右键的按键信息接收过来,并且形成事件触发,传到显示模块以及整体模块。而在DispCtrl 显示模块中,disprom_core 是rom 模块,里面存储的内容是用于在初始界面上显示“无锡工艺学院”六个大字。print_core 是双口RAM 模块:当工作在写字板模式时,即鼠标的左键按下时,便将鼠标的位置翻译成RAM_A 的地址,并将对应的颜色数据实时写进RAM 中。显示模块实时读出RAM 中的颜色数据,在屏幕上显示出来。对于显示控制器来说,将存储器中的数据读出来在CRT显示器上显示。将图像控制模块分为这样几部分:二分频电路、VGA 时序控制模块、存储器读出模块。其中二分频把50 Hz 时钟频率分成25 Hz 并提供给其他模块作为时钟;VGA 时序控制模块用于产生640 ×480 显示范围,并控制显示范围和消隐范围以及产生水平同步时序信号hs和垂直同步时序信号vs 的值;存储器读出模块提供给ROM 或双口RAM 地址,并按地址读出1 位数据(颜色标识),然后得到R,G,B 的值,并把R,G,B 的值通过VGA接口传到CRT 显示器。

图2 原理框图

本系统的设计硬件分为2 个部分:鼠标和显示器的硬件及驱动,分别介绍如下。

2.1 鼠标原理

标准的PS/2 鼠标,支持的输入x(左右)位移、y(上下)位移、左键、中键和右键鼠标以一个固定的频率读取这些输入,并更新不同的计数器,然后标记出反映的移动和按键状态。标准的鼠标有两个计数器,保持位移的跟踪,x 位移计数器和y 位移计数器。可存放9 位的2 进制补码,并且每个计数器都有相关的溢出标志,它们的内容连同三个鼠标按钮的状态一起以三字节移动数据包的形式发送给主机。位移计数器表示从最后一次位移数据包被送往主机后,有位移量发生。

当鼠标读取它的输入时,则记录按键的当前状态,然后检查位移,如果位移发生它就增加(对正位移)或减少(对负位移)x 或y 位移计数器的值。如果有一个计数器溢出了就设置相应的溢出标志。

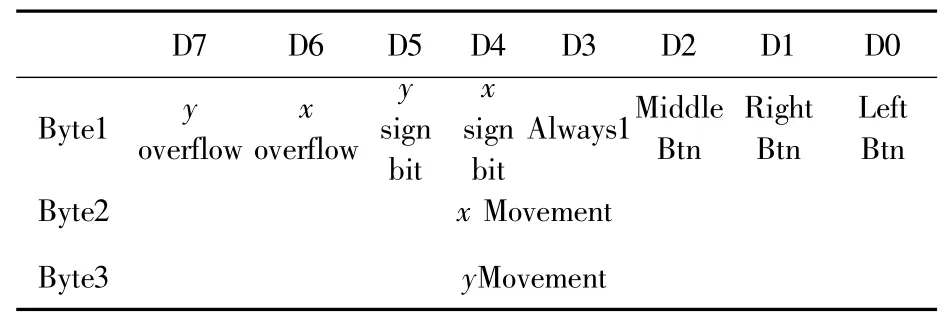

标准的PS/2 鼠标,发送位移和按键信息给主机采用如表1 的3 字节数据包格式(表1)。

表1 3 字节数据包格式

根据鼠标工作的模式来处理的数据报告有4 种标准的工作模式。

1)Reset——鼠标在通电或收到“Reset”(0xFF)命令后进入Reset 模式。

2)Stream——这是缺省模式在Reset 执行完成后,也是多数软件使用鼠标的模式。如果主机先前把鼠标设置到了Remote 模式,那它可以发送Set Stream Mode(0xEA)命令给鼠标,让鼠标重新进入Stream 模式。

3)Remote——在某些情况下Remote 模式很有用,可以通过发送Set Remote Mode(0xF0)命令进入。

4)Wrap——除了为测试鼠标和它的主机之间的连接外,这个模式不是特别有用。

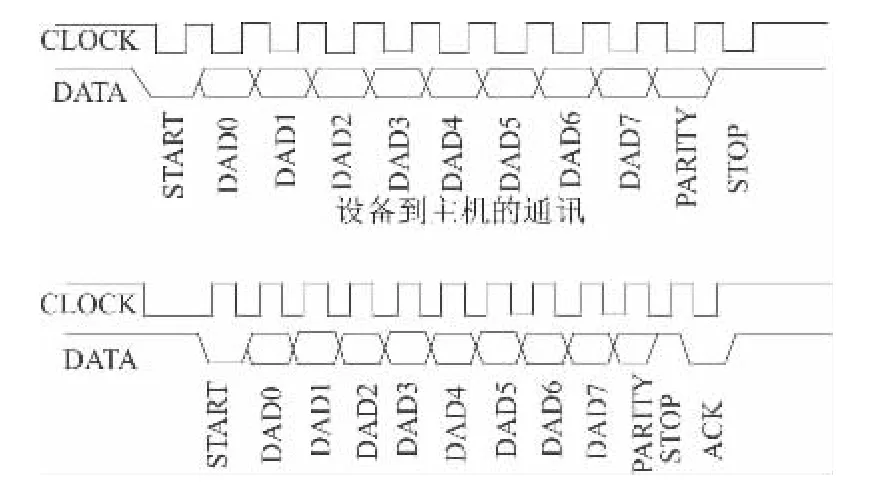

PS2 通讯协议是一种双向同步串行通讯协议。通讯的两端通过Clock(时钟脚)同步,并通过Data(数据脚)交换数据。任何一方如果想抑制另外一方通讯时,只需要把Clock(时钟脚)拉到低电平。如果是PC 机和PS2 键盘间的通讯,则PC 机必须做主机,也就是说,PC 机可以抑制PS2 键盘发送数据,而PS2 键盘则不会抑制PC 机发送数据,即主机总是在总线上有优先权。一般两设备间传输数据的最大时钟频率是33 kHz,大多数PS2 设备工作在10 kHz~20 kHz。每一数据帧包含11~12 个位,具体含义如表2 所列。

表2 PS/2 通讯数据帧格式

表中,如果数据位中1 的个数为偶数,校验位就为1;如果数据位中1 的个数为奇数,校验位就为0;总之,数据位中1 的个数加上校验位中1 的个数总为奇数,因此总进行奇校验。设备到主机的通讯和主机到设备的通讯的时序如图3。

图3 主机到设备的通讯

2.2 VGA 显示接口原理

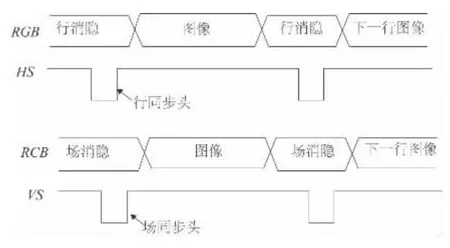

常见的彩色显示器,一般由CRT(阴极射线管)构成。彩色是有R,G,B(红:RED,绿:GREEN,蓝:BLUE)三基色组成。显示是用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有银光粉的荧光屏幕上,产生R,G,B 三基色,合成一个彩色像素。扫描从屏幕的左上方开始,从左到右,从上到下,进行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步,扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

行场扫描时序如图4 所示。以正极性为例,说明CRT的工作过程:R,G,B 为正极性信号,即高电平有效。当VS=0,HS=0 时,CRT 显示的内容为亮的过程,即正向扫描过程约为26 us。当一行扫描完毕,行同步HS=1,约需6 us,期间,CRT 扫描产生消隐,电子束回到CRT 的左边下一行的起始位置(x=0,y=1);当扫描完480 行后,CRT的场同步VS=1,产生场同步是扫描线回到CRT 的第一行第一列(C=0,y=0 处,约为两个行周期)。HS 和VS 的时序图。T1 为行同步消隐(约为6 us);T2 为行显示时间。

图4 行场扫描时序示意图

2.3 算法部分

如果要单色显示整个屏幕的话,需要640 ×480=307 200的储存位数,而basys2 上的spartan 3-100 的FPGA 是不够的。为了在整个屏幕上都可以画画,解决方案是,通过算法,将相邻的4 个点作为1 个点来进行读和写:首先将鼠标发出的位置信息转化为坐标(Xpos,Ypos),然后将两个信号定义为整型,利用整型信号做除法运算之后,只有整数没有小数的特性,将(Xpos,Ypos)都除以2,这样屏幕上的上下左右4 个点的坐标都变为了同一个值,然后再转化为地址去写双口RAM,这样就节省了4 倍的存储空间,大大地节约了FPGA 的资源。

3 结语

本文介绍了一种基于FPGA 的电子画图板,由于系统内部都是由硬件搭建而成,使得整个系统响应速度很快。并且采用了较巧妙的控制算法大大节约了FPGA 资源,降低了成本。经过测试,性能稳定,加上体积较小,后期可以根据不同需要进行相关IO 设计和控制算法设计,以满足市场需求。

[1]田耘,徐文波.Xinlinx FPGA 开发实用教程[M].北京:清华大学出版社,2008:5-7.

[2]褚振勇.FPGA 设计及应用[M].西安:西安电子科技大学出版社,2004:90-94.

[3]廖日坤.CPLD/FPGA 嵌入式应用开发技术白金手册[M].北京:中国电力出版社,2005.18-46.