基于TSI578的Rapid IO互连技术

冼友伦,纪小明,王显跃

(西南电子设备研究所,成都 610036)

基于TSI578的Rapid IO互连技术

冼友伦,纪小明,王显跃

(西南电子设备研究所,成都 610036)

针对传统总线数据传输存在的问题,提出基于Rapid IO在高速信号处理的应用,介绍Rapid IO的体系结构及其性能优势,根据Rapid IO协议,给出了基于TSI578的Rapid IO互连方案,并在实际系统上进行验证与实现。实验结果表明,该方案是有效的。

高速总线;Rapid IO;互联技术;FPGA;TSI578

1 引言

在高速实时信号处理领域,为了达到高处理速度和好的实时性能,在运算同时I/O也在实时传输数据,且处理器的运算能力和I/O能力应该是匹配的。运算能力和I/O能力相匹配的含义是:I/O所花费的时间不应超过运算所花费的时间。随着处理器内核速度迅速提高和I/O速度相对滞后,过去的一些运算密集型算法已经转变为I/O密集型算法。因此提高数据的传输速率,对提高整个信号处理系统的实时性有着重要意义。

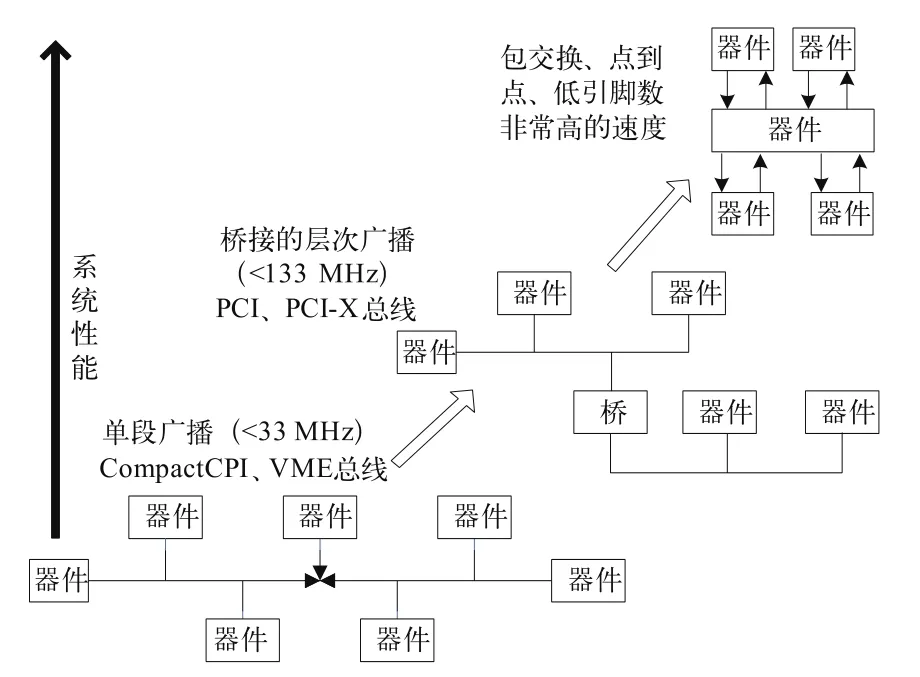

在过去30年中,总线技术飞速发展,从最初的8 bit PC/XT、16 bit ISA总线、32 bit EISA和MCA、VL总线,到现在流行的PCI总线,总线性能大致每3年提升一倍,其总线技术发展变化如图1所示。然而总线频率的发展仍落后于处理器频率的增长,主流PCI总线显得越来越力不从心,并暴露出越来越多的缺点和不足。随着RAID阵列、千兆以太网等一些高带宽设备在消费级系统上的出现,系统对PCI总线频率提出了更高要求,为满足这些要求,每段总线所能支持的设备数只能减少,而为了连接同等数量的设备,就需要更多的总线段、更高的总线性能、更多的器件扇出能力和更大的器件分隔。尽管PCI-PCI桥接设备可以解决这一问题,但是它只能应用在树形体系结构中,而且系统延时也会因此而增加,并且需要的PCI器件也更多,系统成本也相应增加。

Rapid IO作为新一代总线,其目标应用就是高性能嵌入式系统间的互连通信。Rapid IO的诞生弥补了其他总线在性能上的不足。可行的应用包括连接多处理器、存储器、网络设备中的存储器映射I/O器件、存储子系统和通用计算机平台。这一互连技术主要为系统内部互连,支持芯片到芯片和板到板的高速通信,可以实现1 Gbps~60 Gbps的性能水平。其基于Rapid IO的处理系统架构如图2所示。

图1 总线技术发展状况

图2 基于Rapid IO的通用处理架构

从图2中可以看到,在实际系统中要实现高效率大规模的Rapid IO通信,必须采用基于交换的Rapid IO系统集成。本文将结合具体项目讨论基于交换的Rapid IO互连技术实现。

2 Rapid IO技术

Rapid IO协议是一种高速通信协议,能够满足芯片间、板间Gbyte/s量级的通信需求,其实现具有高性能、低延迟、低引脚数和低功耗等特点,是高速AD采集、数字波束合成(DBF)、板间大数据量传输等应用中数传接口的一个理想选择。

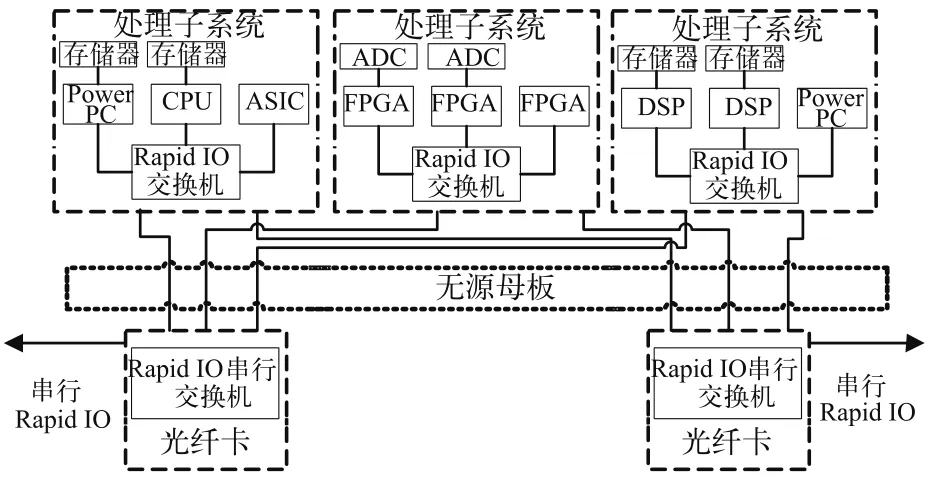

为满足灵活性和可扩展性要求,Rapid IO协议分为3层:逻辑层、传输层和物理层(图3)。逻辑层定义了操作协议;传输层定义了包交换、路由和寻址机制;物理层定义了电气特性、链路控制和纠错重传等。在Rapid IO中有串行1位模式和4位模式两种。

逻辑层定义了操作协议和相应的包格式。Rapid IO支持的逻辑层业务主要是直接IO/DMA和消息传递。直接IO/DMA模式是最简单实用的传输方式,其前提是主设备知道被访问端的存储器映射。在这种模式下,主设备可以直接读写从设备的存储器。直接IO/DMA在被访问端的功能往往完全由硬件实现,所以被访问的器件不会有任何软件负担。从功能上讲,这一特点和TIDSP的传统主机接口(HPI)类似。但和HPI口相比,SRIO带宽大、引脚少,传输方式更灵活。消息传递模式则类似于以太网的传输方式,它不要求主设备知道被访问设备的存储器状况。数据在被访问设备中的位置则由邮箱号(类似于以太网协议中的端口号)确定。从设备根据接收到的包的邮箱号把数据保存到对应的缓冲区,这一过程往往无法完全由硬件实现,而需要软件协助,所以会带来一些软件负担。

图3 Rapid IO协议分层结构

Rapid IO是基于包交换的互连技术,传输层定义了包交换的路由和寻址机制。Rapid IO网络主要由终端器件和交换器件组成。终端器件是数据包的源或目的地,不同的终端器件以器件ID来区分。Rapid IO支持8位或16位器件ID,因此一个Rapid IO网络最多可容纳256或65 536个终端器件。与以太网类似,Rapid IO也支持广播或组播,每个终端器件除了独有的器件ID外,还可配置广播或组播ID。交换器件根据包的目地器件ID进行包的转发,交换器件本身没有器件ID。Rapid IO的互连拓扑结构非常灵活,除了通过交换器件外,两个终端器件也可直接互连。

Rapid IO 1.x协议定义了以下两种物理层接口标准:8/16并行LVDS协议和1×/4×串行协议(SRIO)。并行Rapid IO由于信号线较多(40~76)难以得到广泛的应用,而1×/4×串行Rapid IO仅4或16个信号线,逐渐成为主流。串行Rapid IO基于现在已广泛用于背板互连的SerDes技术,它采用差分交流耦合信号。差分交流耦合信号具有抗干扰强、速率高、传输距离较远等优点。差分交流耦合信号的质量不是由传统的时序参数来衡量,而是通过眼图来衡量,眼图中的“眼睛”张得越开则信号质量越好。

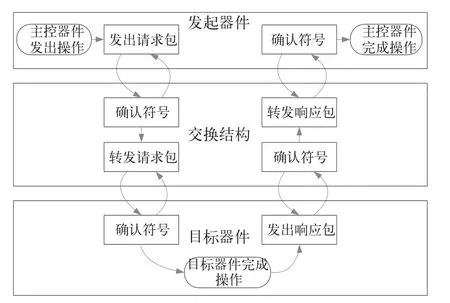

Rapid IO操作是基于请求和响应事务的,通常主控器件产生一个请求事务(比如读请求),该事务被发送至目标器件。目标器件于是产生一个响应事务(读响应)返回至发起器件完成该次操作。Rapid IO事务被封装在包中,包含了确保将事务可靠传送至目标端点的所有必须的字段。通常不会将Rapid IO端点直接互连在一起,而是通过介于其间的交换结构连接。控制符号用于管理Rapid IO物理层互连的事务流,也用于包确认、流量控制和维护功能。图4给出了Rapid IO操作的基本流程,该操作流程包括完整的请求响应事务对。

图4 Rapid IO操作的基本流程

Rapid IO协议包作为端点器件间的基本通信单元,由代表3级规范体系结构的多个字段组成,包括源地址、目的地址、事务类型、事务ID、器件偏移地址、有效数据载荷等,其中有些字段依赖于具体的上下文,并不会在所有的包中出现。图5给出了一个写请求包格式,其中浅灰色字段代表物理层信息,灰色字段代表传输层信息,白色字段代表逻辑层信息,值得注意的是Rapid IO传输中有效载荷数据的最大长度是256 Byte。

图5 串行Rapid IO包格式

Rapid IO协议根据物理层实现的不同可分为并行Rapid IO和串行Rapid IO,相比并行技术,串行技术具有以下优势:

(1)串行I/O技术利用嵌入式时钟方案通过同一条信号线传输时钟和数据信号,由接收端从信号中恢复时钟,从而避免了与时钟失真相关的问题。

(2)由于使用的引脚数目少,PCB板的可布线性也得到进一步提高。我们知道,PCB板上的引脚越多,控制信号间的抖动、畸变以及信号占空比变形等问题的难度就越大,稍有差错就可能导致系统设计的失败。

目前,支持Rapid IO协议的主要芯片有FPGA、 PowerPC、DSP、交换芯片、桥接芯片、存储器等。其中Xilinix的FPGA支持Rapid IO协议的有Virtex-4FX、Viretx5LXT/SXT/FXT、Virtex6LXT/SXT/FXT等系列产品。

3 TSI578的交换处理

交换机在基于Rapid IO的系统互连中是必不可少的,虽然可以在两个器件之间用Rapid IO技术进行点到点的连接,但是使用交换机可以降低总的系统成本,改善系统性能。Rapid IO互连架构假设交换机在系统设计中将会是一种重要的组件。在该设计中交换机是用TSI578来实现的。

TSI578是Tundra的第三代串行Rapid IO交换机,支持高达80 GB的聚合带宽。每片TSI578可以配置为8个4×mode端口或16个1×mode端口,每个端口支持的速度可以配置为每秒1.25 GB、2.5 GB和3.125 GB。最多支持64 000个端点的数据包路由表。其中TSI578的组件示意图如图6所示。

图6 TSI578组件示意图

TSI578的操作十分简单,可以灵活修改其中的寄存器来改变TSI578的工作模式。在具体应用中可以通过JTAG、I2C和Rapid IO修改TSI578的寄存器。JTAG主要是用于在线调试、硬件调试阶段使用,通过JTAG可在线读写TSI578中的控制寄存器和状态寄存器,同时可以控制I2C接口读写EPROM,通过JTAG口可以对单个寄存器进行操作,也可以通过脚本文件批量修改寄存器,这样就可以大大提高效率。

I2C主要是外接EPROM来固化最终TSI578的工作模式,上电后TSI578自动通过I2C引导EPROM中的值来初始化TSI578,也可以把I2C接到控制芯片上,如FPGA、单片机等。控制芯片通过I2C可在线实时监测和控制TSI578。

同时TSI578的每个端口可以判断所接收的包是数据包还是控制包,如果收到的是控制包,可以通过端口来修改TSI578的控制寄存器,实现在线修改配置寄存器,使TSI578工作在各种模式,满足多种不同需求。

在应用中对TSI578的模式寄存器、状态寄存器和路由表寄存器进行操作。

模式寄存器主要控制每个端口的工作模式。我们常用的控制主要包括每个端口工作在4×mode还是1×mode,这里值得注意的是TSI578工作在1×mode时是MAC的A和B,而FPGA是MAC的A和C,在硬件设计时应该注意,如图7所示。可以配置每个端口的传输速度每秒1.25 GB、2.5 GB和3.125 GB。可以使每个端口工作在Power PC Down模式下,从而降低功耗;每个端口可以工作在自回环模式,这样就能十分方便地测试每个端口的硬件性能,如图7所示。工作在4×mode时可通过寄存器来交换MAC的端口顺序,以适应不同的硬件连接。TSI578为了适应不同芯片在不同电器标准之间的数据交换,可以通过寄存器来修改Vpp的值;为了满足高性能的要求,可以对每个端口设置中断、优先级和错误检查机制等。

图7 TSI578 MAC结构

状态寄存器主要是检查TSI578的工作状态,主要包括每个端口的状态信息、接收数据是否出错和当前路由表信息等。

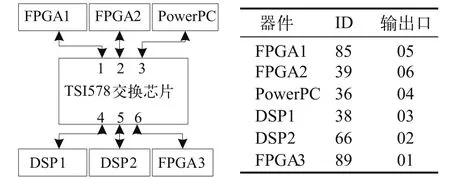

路由表的配置是TSI578进行交换的关键一步,在一个系统中我们必须为每个端口分配一个唯一的ID,该ID必须与Rapid IO数据包的Destination ID一致,当接收端口收到数据包后解析包的Destination ID,只有接收包的Destination ID与端口的ID一致后才发生交换。同时每个端口还需要配置输出端口的号,通过优先级可将多个端口输出到一个端口,在广播方式中一个端口可以输出到多个端口。其端口路由表配置如图8所示,最多可以构成64 000个不同的ID,输出端口号只能是TSI578的对应输出端口。

图8 TSI578路由表

4 Rapid IO系统验证

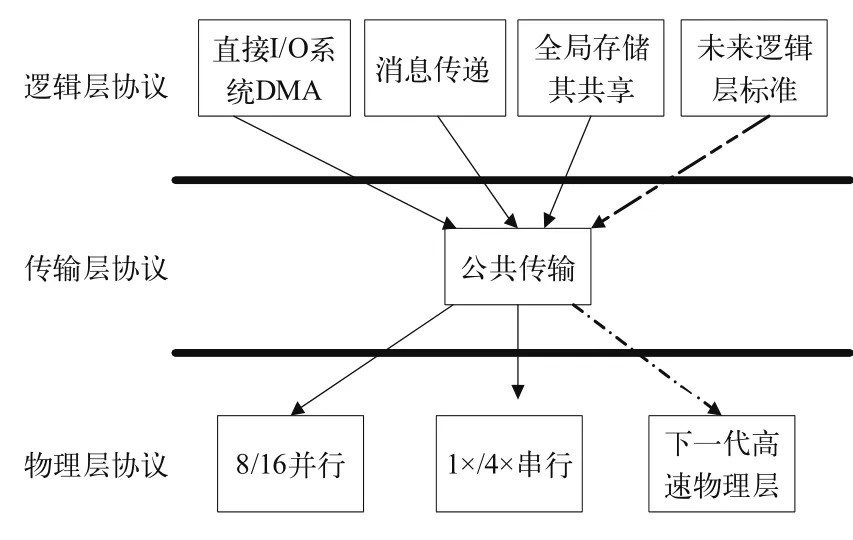

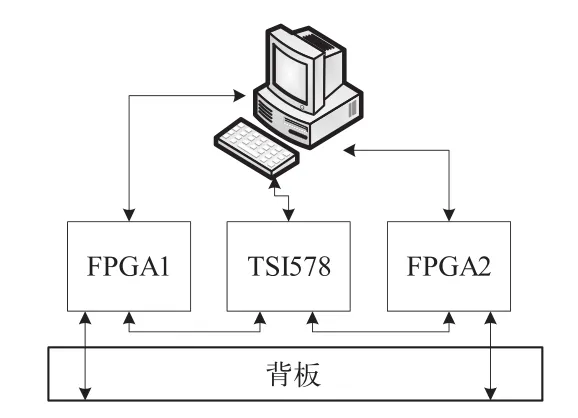

该Rapid IO验证系统由两块FPGA板、一块交换板和一块母板构成,FPGA板的FPGA选用Xilinix的Viretx5SX95T实现Rapid IO的收发数据,交换板通过TSI578实现。其系统构成如图9所示。

图9 Rapid IO验证平台

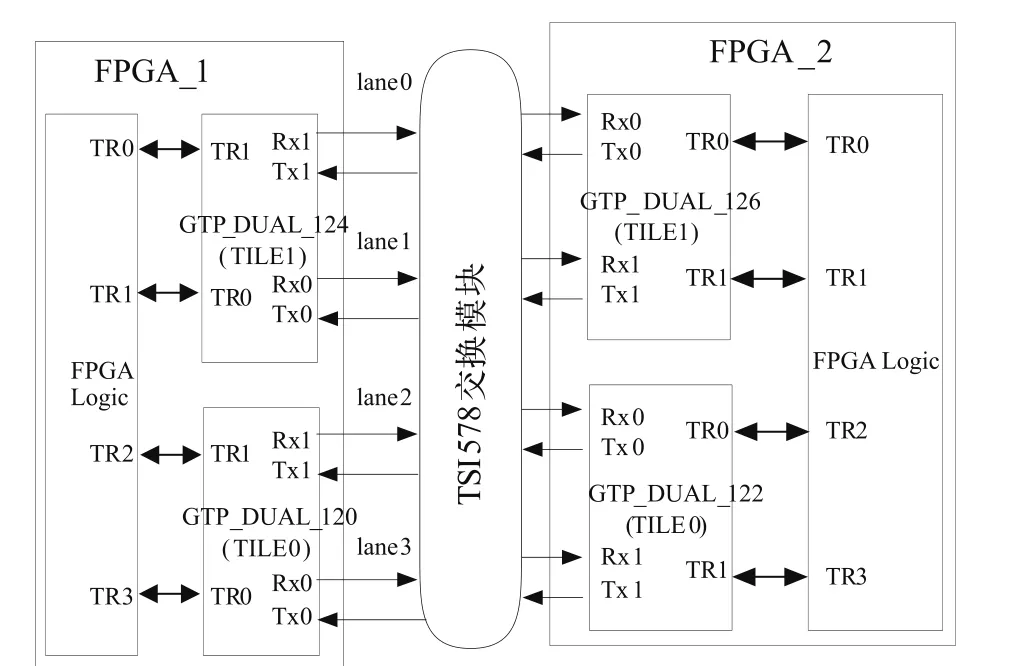

在硬件实现上,Rapid IO参考时钟由外部晶振提供,频率156 MHz。其物理实现组成框图如图10所示。图中,FPGA逻辑资源实现了用户应用、Rapid IO逻辑层、传输层和部分物理层功能,物理层核心功能由GTP核实现,每个GTP核包括两个收发器,对于4×串行Rapid IO设计,其需要使用两个GTP核,共4个收发器。

FPGA1接到交换板TSI578的port6,FPGA2接到交换板TSI578的port8。FPGA1发送Rapid IO数据包的Destination ID为25,FPGA2发送Rapid IO数据包的Destination ID为54。在TSI578配置时Port6的ID为25,输出端口为8,Port6的ID为54,输出端口为6。

图10 物理实现组成框图

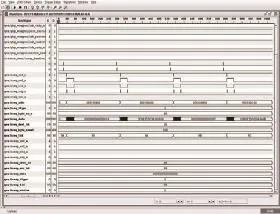

FPGA1通过Rapid IO发送数据给交换板,同时接收交换板发送的数据,FPGA2的工作模式与之类似。系统单通道工作在3.125 Gbit/s波特率下(总波特率为12.5 Gbits/s),采用Chip Scope对实际数据进行采样。TSI578配置成功后FPGA1发送端看到信号波形如图11所示。

图11 Rapd IO发送时序图

由图11可知,各信号含义为:

ireq_sof_n_i、ireq_eof_n_i分别表示发送请求帧的起始和结尾,低电平有效;ireq_vld_n_i表示数据载荷有效,ireq_rdy_n_o表示IP core准备就绪,可以在这个时钟周期接收包头和输入数据;ireq_dest_id表示目标端的ID号;ireq_byte_count表示数据包中有效数据的个数,以byte为单位;ireq_ftype表示主控端发送的请求事务的类型,5代表写请求,2代表读请求;ireq_tid表示请求事务包的编号,该编号顺序增加;ireq_addr表示目标端内存偏移地址,是读写该帧数据的首地址;ireq_data在写请求时表示有效数据载荷,读请求时没有意义;iresp_sof_n、iresp_ eof_n分别表示接收响应帧的起始和结尾,低电平有效;iresp_vld_n表示IP core输出数据有效,iresp_ rdy_n表示用户准备就绪,可以在这个时钟周期接收包头和输出数据;iresp_src_id_o表示目标端的ID,iresp_dest_id_o表示主控端的ID;iresp_ftype表示目标端发送的响应包的事务类型;iresp_tid表示对应于读请求的事务编号;iresp_data表示目标端返回的读请求要求的有效数据载荷,数据和事务编号具有一一对应关系。

由图11可知,Initiator(主控端)的ID是0x0F,Target(目标端)的ID是0x25,Initiator向Target发送写请求,事务编号0x99,向Target首地址为0x00100900处写入256 Bytes(32×64)的有效数据,完成上面的操作,事务号依次增加,0x9A,0x9B,……

5 结论

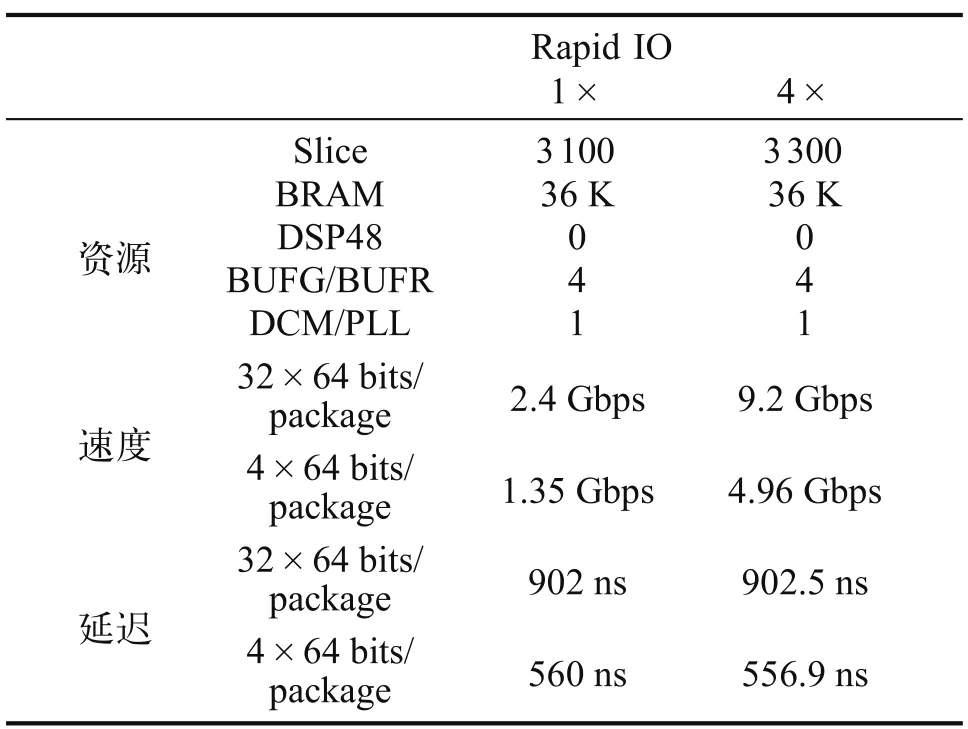

通过试验Rapid IO可以实现灵活、高速地通信。基于交换的架构可以实现大规模的系统集成。其在FPGA(95T)中实现Rapid IO通信的资源占用情况、传输速度、传输延时如表1所示。

表1 Rapid IO在95T下的效率

Rapid IO技术主要面向高性能嵌入式系统的互连通信,它采用高性能的LVDS技术,可以在4对差分线上实现10 Gbps的有效传输速率,而且具有比万兆以太网、PCIexpress更高的传输效率。由于Rapid IO在路由、交换、容错纠错、使用方便性上有较完善的考虑,可以实现基于硬件的高性能可靠数据传输,所以在嵌入式、3G和3G之后的Beyond 3G/4G移动通信、高性能数字信号处理系统中得到广泛应用。

[1] Tundra Semiconductor Corporation. Tsi578 Serial Rapid IO Switch User Manual [Z], 2008.

[2] Xilinx. Serial Rapid IO v5.3 Getting Started Guide 2009 [Z].

[3] Rapid IO Trade Association. Rapid IO Interconnect Specif i cation [Z], 2009.

[4] 王勇,等. Rapid IO嵌入式系统互连[M]. 北京:电子工业出版社.

Rapid IO Interconnected Technology Based on TSI578

XIAN Youlun, JI Xiaoming, WANG Xianyue

(Southwest China Research Institute of Electronic Equipment,Chengdu610036,China)

Aiming at the problem existed in traditional bus, a scheme of serial Rapid IO used in the highspeed signal processing. The framework and advantage of Rapid IO are introduced. According to the protocol Rapid IO, Rapid IO interconnected project is given based on TSI578, which is inspected and implemented. Experimental results show the scheme is effective.

high speed bus; Rapid IO; interconnected technology; FPGA; TSI578

TN402

A

1681-1070(2014)11-0026-05

冼友伦(1983—),男,四川攀枝花人,工程师,目前在西南电子设备研究所主要从事高速电路设计工作。

2014-09-30