基于EDA技术的PS/2接口电路设计

王 勇 宋 潇 孙孟方

(1.河南科技大学电气工程学院,河南 洛阳 471023;

2.中国航空工业集团公司洛阳电光设备研究所,河南 洛阳 471009)

基于EDA技术的PS/2接口电路设计

王 勇1宋 潇1孙孟方2

(1.河南科技大学电气工程学院,河南 洛阳 471023;

2.中国航空工业集团公司洛阳电光设备研究所,河南 洛阳 471009)

基于EDA技术,使用FPGA芯片和VHDL语言,设计了一种PS/2设备接口电路。介绍了硬件连接、通信协议、设计过程及仿真结果。采用自顶向下的设计思路,充分发挥EDA技术的优势,大大缩短了设计周期。软件仿真及硬件调试表明,设计中的各个模块之间能够正确地传送数据,性能稳定,达到了预期目标。

PS/2接口;FPGA;VHDL;通信协议

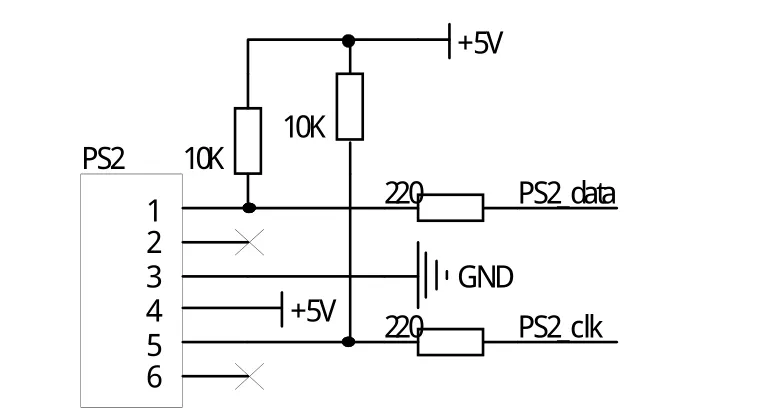

图1 PS/2接口外围硬件电路

1.引言

PS/2作为常用的人机接口,在嵌入式系统中有着广泛应用。例如PS/2键盘内含自动去抖功能,软硬件开发简便,价格便宜,通用性强[1]。基于FPGA的EDA技术在近些年发展迅速,正逐渐成为电子系统设计的主流,设计人员利用它可以设计出自定义功能的专用集成电路,缩短了开发周期,降低了开发成本。FPGA还具有静态可重复编程和动态在系统重构的特性,使得硬件功能可以像软件一样通过编程来修改。VHDL主要用于描述数字系统的结构、行为、功能和接口,除了含有具有硬件特征的语句外,其语言形式、描述风格与句法类似于一般的计算机高级语言。VHDL程序的结构特点是将一项工程设计分成外部接口部分和内部结构部分,一旦内部开发完成,其它的设计可以直接调用这个实体。因此采用VHDL硬件描述编程语言,在FPGA系统中嵌入PS/2设备接口电路,在产品开发中是可行和必要的。

2.PS/2接口及通信协议

2.1 PS/2接口

物理上的PS/2接口有两种连接类型,即5脚的DIN和6脚的MINI-DIN。实质上,这两种类型都只有4个脚有意义,它们分别是1脚数据(data)、3脚电源地(GND)、4脚电源(VCC)和5脚时钟(clk)。在PS/2设备与主机的物理连接上只要保证这四根线一一对应即可。PS/2设备靠主机提供+5V电源,另外两个脚clk和data都是集电极开路的,需要在外围硬件设计上进行上拉,相应电路如图1所示。

2.2 通信协议

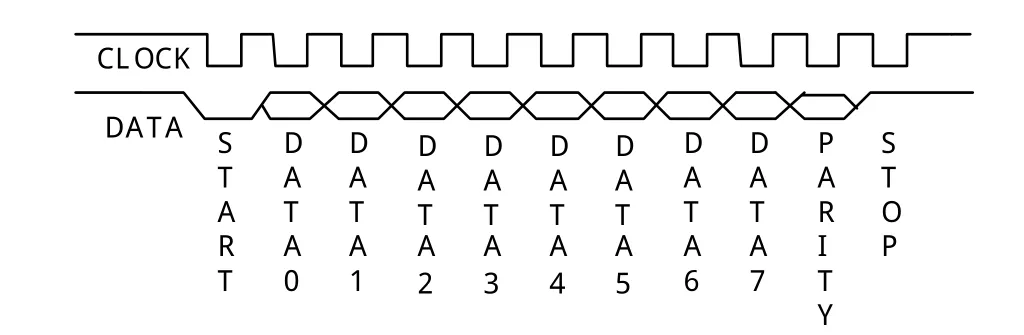

PS/2接口遵循一种双向同步串行通信协议。PS/2设备可以发送数据到主机,主机也可以发送数据到PS/2设备,主机在总线上有优先控制权,它可以在任何时候抑制来自于PS/2设备的通信。PS/2设备发送到主机的数据在时钟信号的下降沿被读取;主机发送到PS/2设备的数据在上升沿被读取。不管通信的方向怎样,PS/2设备总是产生时钟信号,最大的时钟频率是33KHz,一般设计为15KHz左右。通信数据安排在字节中,每个字节为一帧,包含了11或12位,如图2所示。其中第1位是起始位(低有效),紧跟8个数据位(低位在前),第10位为校验位(奇校验),第11位为停止位(高有效),第12位为应答位(仅用在主机对设备的通信中)。若数据中包含偶数个“1”,校验位置“1”;若数据中包含奇数个“1”,校验位置“0”。数据位中“1”的个数加上校验位为奇数,这可用来检测传输过程是否有错。当主机发送数据给PS/2设备时,设备回送一个信号来应答数据包,表示已经收到,该位不会出现在设备发送数据到主机的过程中。下面以设备到主机的数据传输过程为例阐述PS/2的通信过程[2]。

当PS/2设备等待发送数据时,它首先检查时钟以确认它是否为高电平,如果不是,则说明主机抑制了通信,设备必须缓冲任何要发送的数据直到重新获得总线的控制权;如果时钟此时为高电平,设备则可以传送数据。每位在时钟的下降沿被主机读入,通信时序如图2所示。当时钟为高时,数据线改变状态,在时钟信号下降沿,数据被锁存。从时钟脉冲的上升沿到一个数据传送的时间至少需要5μs。数据变化到时钟脉冲的下降沿的时间也至少需要5μs,这个定时应该严格遵循。在停止位发送后,设备在发送下一帧数据前至少应该等待50ms,这是因为主机在处理接收字节时抑制了发送。

图2 PS/2设备到主机通信时序

2.3 PS/2设备返回值介绍

PS/2设备(以键盘为例)的处理器如果发现有键被按下或释放将发送扫描码信息到主机。扫描码有两种不同的类型:通码和断码。当某键被按下则发送通码,当该键被释放则发送断码,每个按键被分配了唯一的通码和断码。这样主机通过查找扫描码就可以识别按键。一整套的通断码组成了扫描码集,目前常用的有三套标准的扫描码集,现代的PS/ 2键盘几乎均默认使用第二套扫描码。设计者不用总是通过查表来找出按键的断码,在通码和断码之间存在着必然的联系。多数第二套断码有两字节长,第一个字节是F0H,第二个字节是这个键的通码值。扩展按键的断码通常有三个字节,前两个字节是E0H、F0H,最后一个字节是这个按键通码值,每个按键具体的通断码值可查阅相关的码表,这里不再赘述。

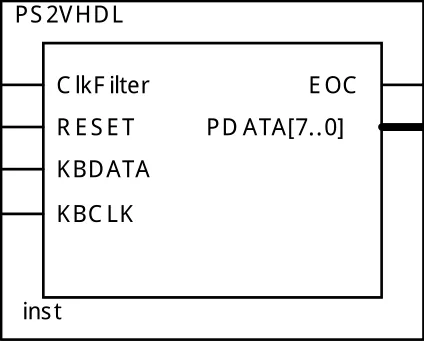

3.PS/2接口的VHDL硬件实现

设计的PS/2接口模块的主要功能是将输入的PS/2按键值转换成扫描码,并最终转换成ASCII码输出,同时要求能够响应PS/2键盘上的所有按键,包括基本按键和扩展按键,顶层实体如图3所示。模块内部用VHDL语言编写,用系统时钟扫描PS/2设备时钟线的变化,接收数据线上的数据,然后按照PS/2的通信协议进行解析,并暂存解析后的8位数据。另一方面需要对接收到的数据的判断,判断它是通码还是断码,最后将断码进行格式转换,对于字母和数字,程序将断码通过译码程序转换成ASCII码,以备后续使用。在进行PS/2接口模块设计时需要注意以下两点:

(1)PS/2的时钟线需要多次锁存

设计中发现,需要对PS/2的时钟线进行多次锁存,否则可能出现键值识别错误。在调试过程中将时钟进行两级锁存,发现按键识别时误码比较严重,时钟线在每次按键时都会随机地产生多余的干扰脉冲,使程序检测到的时钟数多出几个,造成无法连续识别。当将时钟进行十级锁存后,误码率显著降低,问题得到解决。

(2)兼容基本按键和扩展按键

PS/2键盘上的基本按键和扩展按键发送的键码格式不同,但是对键盘扫描的结果需要输出统一的格式,这就需要对数量较少的扩展按键做特殊处理。设计时发现,扩展按键断码的最后一个字节和基本按键的并没有冲突,简单的做法是忽略它的第二个字节E0H,将键码格式看成和基本按键的相同,当检测到通码F0H,则使能标志位,将其后的键码取出进行解析即可[3]。

图3PS/2模块

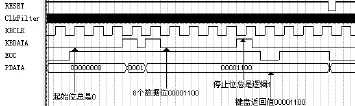

模块中KBCLK是时钟信号,KBDATA是按键的输入值,PDATA是输出扫描码,功能仿真结果如图4所示。由图4可以看出,当RESET为低电平时,执行清零操作;根据PS/2协议的数据帧格式,第1位起始位,并总是逻辑‘0’,接下来的8位是数据位,低位在前,接下来1位是停止位,总是逻辑‘1’,图中的键盘输入KBDATA值是0001100001,PS/2设备返回值PDATA是00001100,说明按键识别正确。

图4 时序仿真波形图

4.结束语

采用现场可编程门阵列FPGA设计了一种PS/2设备接口电路,该电路主要由分频模块、通信协议控制模块、译码模块等组成。PS/2设备的数据输入通过外围接口单元进入FPGA内部,经过控制与解析生成ASCII码输出,从而方便后续按键处理程序使用。程序采用VHDL语言编写,具有较强的功能可移植性。FPGA芯片选用Altera公司的成熟产品EP2C8Q208,充分利用了其高速、大容量、组合灵活等优点,并使用QuartusⅡ开发环境所提供的库资源,最大限度地发挥FPGA的优势,大大简化了系统设计,缩短了设计周期。软件仿真及硬件调试表明,设计中的各个模块能够正确地进行数据传送,工作性能稳定,达到了预期目标。

[1]魏军辉,王福源,周子昂等.基于FPGA的PS/2键盘接口的设计[J].微计算机信息,2008,24(26):138-140.

[2]李攀峰.基于SOPC技术的PS/2键盘接口电路设计[J].自动化与仪器仪表,2012,6:139-141.[3]刘昌华.数字逻辑EDA设计与实践[M].北京:国防工业出版社,2005.

Design of PS/2 Interface Circuit Based on EDATechnology

Wang Yong1Song Xiao1Sun Mengfang2

(1.Henan University of Science and Technology,Luoyang 471023,Henan;

2.Luoyang Research Institute of Electro-Optical Equipment ofAVIC,Luoyang 471009,Henan)

A PS/2 interface circuit is designed based on FPGA chip and VHDL language.Hardware connection,communication protocol,design process and simulation result are introduced.Using the top-down design ideas,giving full play to the advantage of EDA technology,the design greatly shortens the design cycle.Software simulation and hardware debugging demonstrate that data can be transmitted accurately between the modules in the design and the system runs normally.

王勇,男,河南淮滨人,硕士,讲师,研究方向:应用电子电路开发与设计。

河南省教育厅科学技术研究重点项目,项目编号:14A510003;河南省教育厅自然科学研究项目,项目编号:13A510263。

【 Keywords】 PS/2 interface;FPGA;VHDL;communication protocol