基于CPLD的自动售货机的设计与实现

刘明扬, 孙丹丹, 魏学军

(北京邮电大学 电子工程学院, 北京 100876)

0 引 言

随着人们生活的智能化,自动售货机可谓是应运而生。相对于传统的购物模式,自动售货机体现出方便等特点,极大地满足了人们快捷购物的需求。然而,目前市场上一些自动售货机对于货币的处理及购物的提示有着不同程度的缺陷。本设计通过使用EDA技术对各种功能进行优化,运用VHDL语言,简化系统,提高性能,使顾客在购物过程中更加方便[1-2]。

1 设计思想

1.1 整体分析

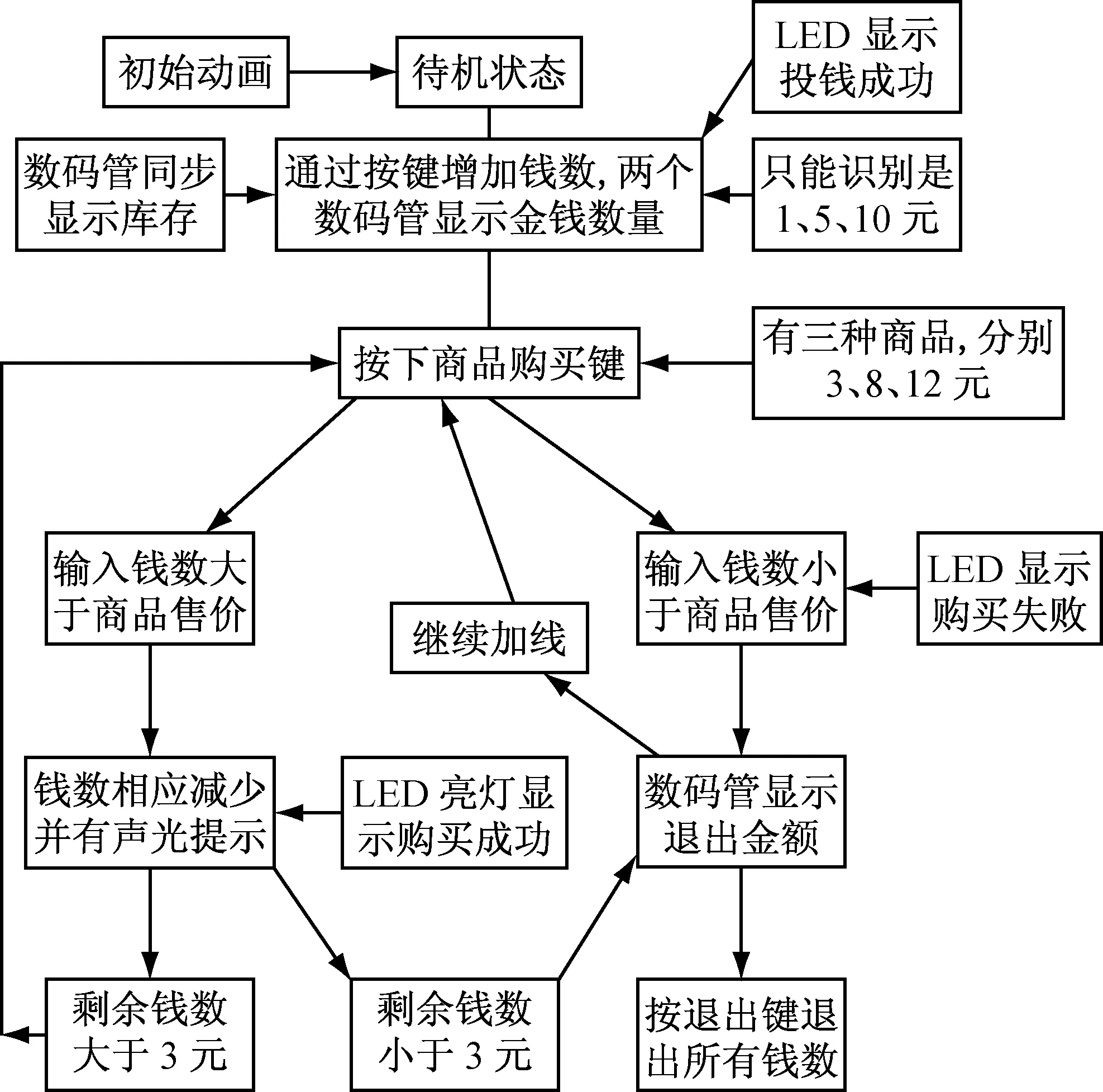

首先从实际使用出发,分析售货机的功能。从两方面来考虑:① 顾客有投币,选择物品,追加投币,退钱等操作;② 对于顾客的操作,机器有相应的反应,并有图像显示等功能。于是根据实际情况我们提出以下的设想。[3]

(1) 顾客使用售货机前有待机动画,表示售货机正常运行。以后的任何操作都有相应的图像对应。

(2) 假设有三种商品,售货机只接受三种面值的货币。当顾客投入1元、5元或10元时,点阵开始循环显示甲、乙、丙三种商品,对应的数码管同步显示三种商品的数量,且若投币成功,有LED提示投钱成功。

(3) 顾客购买物品时,若购买成功则有LED提示,且数码管显示剩余的钱数,整个过程可以随时加钱(即重复过程(2))[4]。

(4) 整个过程中可以随时按下退出键,系统将退出投入的钱数,整个系统将回到初始状态。

1.2 总体框图

2 整体设计

本设计采用Altera公司的MAXII为开发器件,主频50 MHz,以QuartusII作为开发软件,整体支持器件设计,原理图,VHDL,波形仿真,时间分析,编程下载。以上功能为设计提供了技术支持[5]。

2.1 模块划分

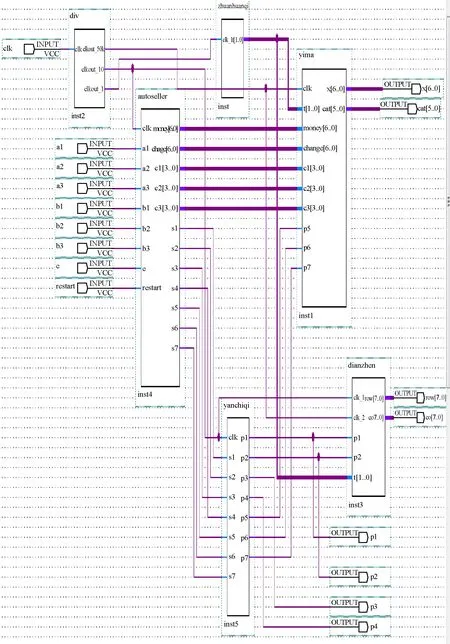

整体分为6个模块,分别为售货机主程序、分频器、转换器、延迟器、数码管和点阵[7]。售货机主程序处理投钱的金额及相应物品的出纳。分频器采用串行分频,将主频50 MHz分为三种频率供其他模块使用。转换器用以循环显示商品数量,并将点阵和数码管显示同步[8]。延迟器用于将主程序输出的信号适当延时,便于LED显示[9]。数码管用来显示钱数及商品库存、投钱总数、退钱总数等[10]。点阵在顾客操作时会呈现相应的动画图像,并提示顾客以后操作[11]。

2.2 核心代码

本设计以QuartusII作为编程软件,其具有数字逻辑设计的全部特性,可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件。此次选取VHDL作为编程语言是因为其较强的行为描述能力,为系统的设计提供了极大的便利,而丰富的仿真语句和库函数也为设计奠定了坚实的基础。[12]

图2 自动售货机的顶层文件

本次设计的关键在于对状态机的运用,使得顾客和机器能达到比较理想的交互状态[13]。信息处理上主要依靠主程序对于钱数和商品的快速处理和数码管中对于数字显示的处理,由于整体设计上点阵和数码管有多处同步,分频器的串行分频也显得十分重要。

(1) 设计中在信息的显示方面采用了状态机的编程思想,集中体现在数码管和点阵显示的控制时钟当中,下面定义了三个状态(d0,d1,d2), 三个状态分别用于在一个数码管上显示三种商品的库存量:

Typestate_type is(d0,d1,d2);

Signalstate:state_type;

case state is

when d0=>t<="00";state<=d1;

when d1=>t<="01";state<=d2;

when d2=>t<="10";state<=d0

(2) 钱数处理(以投入5元为例)。

If (a1true=’0’ and a2 true=’1’ and a3ture=’0’) then

m:=m+5+n;n:=0;s1<='1';s2<='0';s3<='0';s5<='0';s6<='0';s7<='0';

购买3元的商品:

if(m>5)then m:=m-3;x:=x-1;s1<='0';s2<='1';s3<='0';s4<='0';s5<='1';s6<='0';s7<='0';

(3) 数码管对数据的处理中将个位和十位分开,用求余的方法进行计算:

x1<=change mod 10;

x2<=(change-(change mod 10))/10;

x1,x2分别为钱数的个位和十位

(4) 延迟器运用状态机定义了六个状态使得LED显示时间足够长,例如将主程序中输出的“s1=1”这个信号延长6倍时间:

Typestate_typeis(a0,a1,a2,a3,a4,a5,a6)

signalstate1:state_type1;

if (clk'event and clk='1')then

case state1 is

When a0=>if(s1='1') then

state1<=a1;p1<='1';end if;

when a1=>state1<=a2;p1<='1';

when a2=>state1<=a3;p1<='1';

when a3=>state1<=a4;p1<='1';

when a4=>state1<=a5;p1<='1';

when a5=>state1<=a6;p1<='1';

when a6=>state1<=a0;p1<='0';

end case;

3 实验结果

3.1 仿真波形及波形分析

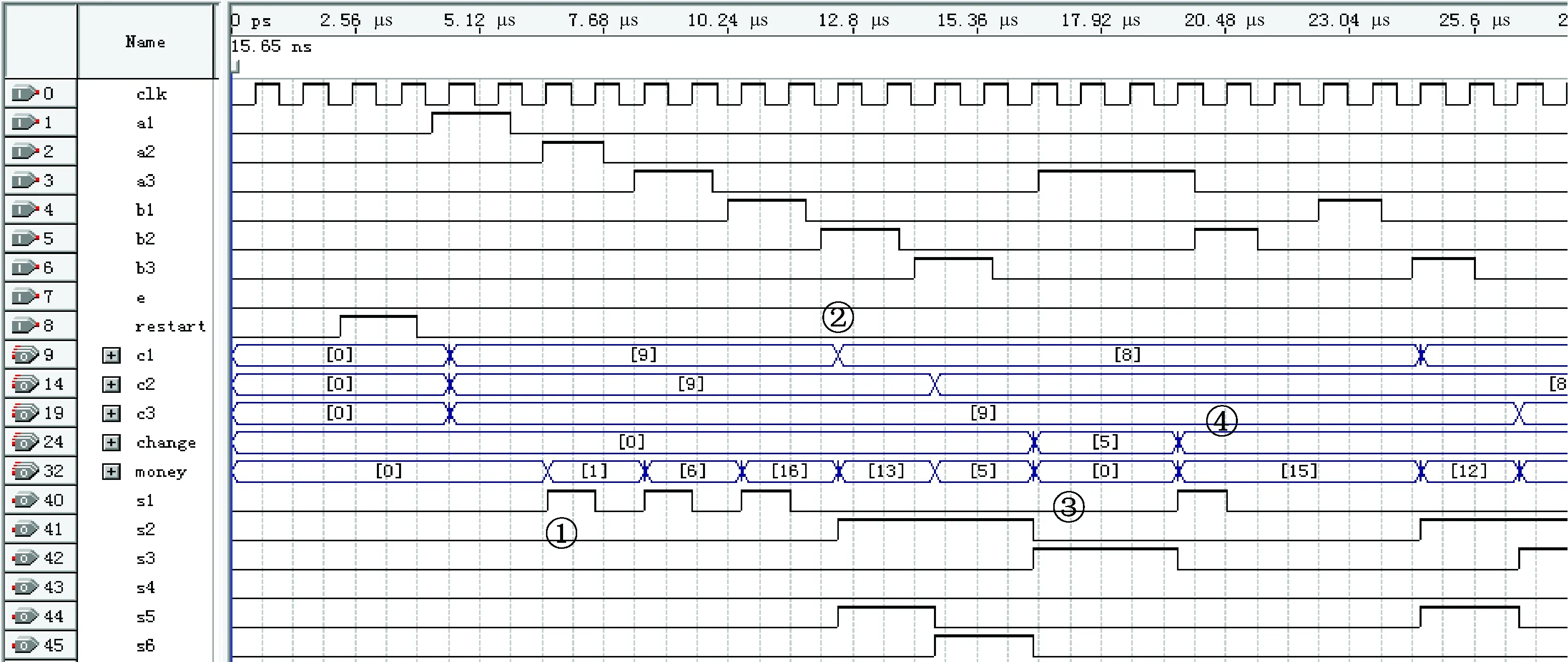

主动能及部分仿真波形见图1、2。其中:a1为1元,a2为5元,a3为10元;b1为3元商品,b2为8元商品,b3为12元商品,c1,c2,c3为三种商品的库存,money为投入钱数,change为找零钱数。s1:投币成功(1) s2:购买成功(1) s3:运行(0),退出 (1) s4:有货(0),缺货(1)。① 代表投钱成功后钱数增加。② 代表购买成功后商品数量减少。③ 代表钱数不够购买商品时,显示找零。④ 代表钱数不够时可以随时投入钱币。⑤ 代表购买商品成功且剩余金额小于3元的情况(此处有13元,购买12元商品)。⑥ 代表商品被购买完即缺货。⑦ 代表缺货提示。

图3 主功能仿真波形

图4 部分功能仿真波形

3.2 性能分析

(1) 由于数码管需要显示顾客投入和找零的钱数及商品库存,所以将显示分为三个部分,且三部分相互关联。考虑到节省硬件资源,数码管采用的是计算模式来显示数据,即通过将钱数的十位个位提出,分开计算并显示。相比列举法,运算速度大大提高[14]。

(2) 为方便顾客购物,点阵显示的图像能清晰地告诉顾客机器是否运转正常以及操作是否成功。例如售货机正常运行时有待机画面,以及顾客的任何操作过后的相应动画提示。与此同时,用延迟器延长了LED显示的时间,使顾客更清晰地看到操作是否成功。

(3) 考虑到售货机的实际运行,男女顾客按键力道大小及压键时间的不同,主程序里加入了防抖程序,切实满足了顾客使用售货机购物时的实际需求。

4 结 语

本文详细介绍了运用单片FPGA芯片进行自动售货机设计的方法,通过对程序的改进优化,充分利用VHDL对FPGA的可编程性,使售货机具有基本的功能[15]。设计从实际使用出发,以简便高效为原则,在满足基本的人机交互的同时,提高程序的运行效率,使得该系统下的自动售货机功能齐备,能满足市场的实际需要。而且对于点阵图像的显示还可以有各种个性化的设计,增加了灵活性,本设计中附加的上货功能也为管理者提供了方便[16]。

[1] 付梦婷,付永庆. 基于CPLD的88键电子琴的设计与实现[J].电子器件,2013,36(11):737-742.

FU Meng-ting, FU Yong-qing. CPLD-based design and implementation of 88 key keyboard [J]. Electronics, 2013,36 (11):737-742.

[2] 赵 刚,何志敏,陈利学.基于FPGA 的EDA 综合实验系统设计[J].微计算机信息,2012,28(1):49-51.

ZHAO Gang, HE Zhi-min, CHEN Li-xue.EDA comprehensive experimental system based on FPGA design[J]. Micro Computer Information, 2012,28 (1):49-51.

[3] 冼立勤,高献伟. MOS管短沟道效应及其行为建模[J].实验室研究与探索,2007,26(10):14-16.

XIAN Li-qin, GAO Xian-wei. Short channel effect MOS tube and behavioral modeling[J].Research and Exploration in Laboratory, 2007,26(10): 14-16.

[4] 韩 进. EDA技术在“数字逻辑”教学实践中的应用[J].实验室研究与探索,2005,24(5):40-42.

HAN Jin. EDA technology in the "Digital Logic" Teaching Practice[J]. Research and Exploration in Laboratory, 2005,24(5): 40-42.

[5] 王晓峰.可编程逻辑器件及硬件描述语言的EDA方法[J].长春大学学报,2005,15(4):14-16.

WANG Xiao-feng. EDA methods of language programmable logic devices and hardware description[J]. Changchun University of Technology, 2005,15 (4):14-16.

[6] 韩延义,李 航,李 岳. 基于FPGA的音频芯片输出控制设计[J].实验室研究与探索,2013,32(5): 94-96,167

HAN Yan-yi, LI Hang, LI Yue. FPGA-based audio chip output control design [J]. Research and Exploration in Laboratory, 2013,32(5): 94-96,167

[7] 王戎丞,陈可中,明 鑫.基于VHDL的数字频率计的设计与实现[J].现代电子技术,2005,28(15):102-104.

WANGg Rong-cheng, CHEN Ke-zhong, MING Xin. VHDL-based design and implementation of digital frequency meter [J]. Modern electronic technology, 2005,28 (15):102-104.

[8] 吴 涛,徐春燕,彭 宏. 基于FPGA的信号与系统实验箱信号源设计[J].实验室研究与探索,2009,28(6):44-47.

WU Tao, XU Chun-yan, PENG Hong. Based Signals and Systems Laboratory Box source of FPGA[J]. Research and Exploration in Laboratory, 2009,28(6): 44-47.

[9] 张友木.基于VHDL语言的几种消抖电路的设计[J].山西电子技术,2011(1):61-63

ZHANGg You-mu. Several debounce circuit design based on VHDL[J],Shanxi Electronic Technology, 2011(1) :61-63.

[10] Galileo Open Service, Signal In Space Interface Control Document (OS SIS ICD) Draft0[S]. 23/05/2006:1-3.

伽利略开放服务,信号在空间接口控制文件(OS SIS ICD)Draft0[S]. 23/05/2006:1-3.

[11] 刘家庆.基于VHDL的2FSK调制解调器设计[J].电子技术,2010(11):73-75.

LIU Jia-qing. 2FSK modem design base onVHDL[J]. Electronics,2010(11):73-75.

[12] 杨文霞,孙青林.数字逻辑电路[M].北京:北京科学出版社,2007:79.

[13] 牟洪江,杨 虹,王 玲.基于VHDL语言的数字频率计的设计[J].电子世界,2013,(19):163-164.

MOU Hong-jiang, YANG Hong, WANG Ling. Digital frequency meter VHDL-based design language[J]. Electronic World, 2013, (19) :163-164.

[14] 徐 伟,刘建成,行鸿彦. 分类并结合专业特色的电子综合课程设计[J].实验技术与管理:2011,28(10):141-143.

XU Wei, LIU Jian-cheng, HANG Hong-yan. Classification combined with professional features of electronic integrated curriculum design [J]. Experimental Technology and Management: 2011, 28 (10):141-143.

[15] 林明权.VHDL数字控制系统设计范例[M].北京:电子工业出版社,2003.

——以“腾讯与360之争”为视角*