2.5G CPOS FPGA设计关键技术研究与实现

刘 健,王文胜

(中国电子科技集团公司第三十研究所,四川成都610041)

2.5G CPOS FPGA设计关键技术研究与实现

刘 健,王文胜

(中国电子科技集团公司第三十研究所,四川成都610041)

随着网络规模的扩大和用户需求的增加,大客户的概念有所扩展,总部-分支的网络应用越来越广。采用何种接入技术,降低组网、维护成本,满足客户实际需求是当前网络建设的焦点。通过对CPOS网络的架构的研究,提出2.5G CPOS网络FPGA设计的总体方案,重点突破2.5G CPOS网络的接入、解析、通道化处理等关键技术的研究和实现,并选用Altera公司的FPGA芯片进行设计实现,加载到FPGA芯片用QUARTUS II信号采集工具Signaltap进行采样验证。

CPOS FPGA 接入 解析 多通道

0 引 言

近年来,同步数字体系(SDH Synchronous Digital Hierarchy)作为一种成熟的传输技术,凭借接口速率高,传输延时小,自愈能力强,带宽利用率高等优势,在传输网上被大量应用,已发展成为目前光纤网上的骨干传输技术。POS(Packet Over SDH)是一种应用在城域网及广域网中的技术,它具有支持分组数据(如IP分组)的优点。POS将长度可变的数据包直接映射进SDH同步载荷中,使用SDH作为物理层传输标准,使用PPP作为数据链路层的链路控制,提供了一种高速、可靠、点到点的数据连接[1]。CPOS是指通道化的POS技术,主要用于提高设备对低速接入的汇聚能力,目前支持STM-1和STM-16两种速率。CPOS充分利用SDH技术优势,提供对带宽精细划分的能力,大幅减少对汇聚型路由器低速物理端口的数量要求,增强其端口汇聚能力和专线接入能力。CPOS技术的推广应用提高了网络接口的丰富性和灵活性,减少网络对传输设备的需求,使路由器部署变得更为简单和智能。目前, CPOS技术正以其明显优势,快速的在网络终端设备(如高端路由器)中取得广泛应用。

1 CPOS网络架构

随着网络规模的发展和用户需求的增加,大客户的概念有所扩大,新形势下大客户已不再局限于党、政、军、金融、交通等企事业集团单位,还包括诸如大中型企业、商业连锁店、写字楼、智能小区、流动和热点地区的用户。

大客户业务也由Internet、语音业务过度到目前数据、视频、VOIP综合接入,接入方式由传统铜线接入发展到光纤接入。接入网络的发展已经从追求覆盖面、增加带宽步入到多业务接入以及综合化管理的新阶段。在物理层面,接入网正朝着物理逻辑层次更清晰,更简化,具有多业务差异化服务能力,具有用户端口唯一标志和可溯源能力的方向发展。所以,采用何种接入技术,如何提供高安全、可靠、差异化业务服务,满足客户实际需求、同时尽量降低组网、维护成本,是运营商当前关注的焦点。

典型大客户具有分部地理位置比较分散、接入点多的特点,是一个“总部-多分支机构”架构,组网模式是点对多点。具体实现方式是每个分支机构通过租用E1专线接入,在距离总部较近的机房收敛汇聚各分支机构数据然后通过光纤接入总部核心交换机或路由器,总部一台155M的CPOS设备就能收敛汇聚63个E1支路的数据[2]。或者对于有较高速率要求的网络,分支采用155M带宽的STM-1的SDH接入,在总部用一台2.5G的CPOS设备就能汇聚16路这样的分支数据,由此可以看出CPOS网络架构能大大减少总部对传输设备以及跳线的需求,能有效减少故障点,方便故障定位。

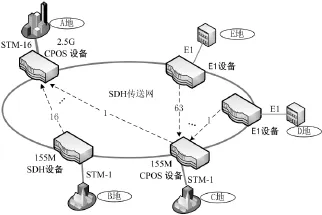

针对这样的“总部-多个分支机构”,提出CPOS网络架构如图1所示。

图1 CPOS网络架构Fig.1 CPOS network framework

其中C地和D、E两地之间构成点对多点的2M专线,D地与E地之间构成点对点的2M专线。C地可表示政府,银行,企业等中型用户。D地、E地分支则表示与C地对应的各政府分支机构,银行各支行网点等小型用户,接入带宽需求一般为N*E1。 C地可通过155M CPOS设备,实现对多条分支信道的收敛汇聚,最多可实现63个E1的收敛汇聚。A地和B、C两点之间构成点对多点的155M专线,B地与C地可构成点对点的155M专线。A地表示更上级的政府、银行、企业等大客户,从而A地可通过2.5G CPOS设备汇聚收敛16个155M支路。

CPOS设备具有反向复用功能,也可以实现对总部分发给支路的高带宽业务的通道化为支路所需的低带宽业务的处理。

2 2.5G CPOS FPGA设计方案

2.1 FPGA设计总体概述

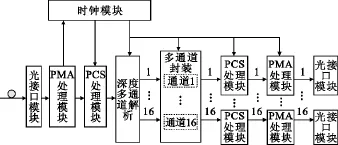

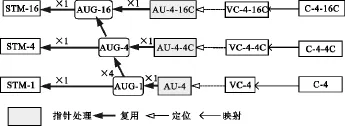

完成2.5G SDH通道化为16个155M SDH的CPOS处理,具体需要实现2.5G SDH光信道的接入、信道协议的解析、通道化处理等几项关键技术,接入技术主要实现信道光信号的光电转换、PMA层处理和PCS层处理等功能。FPGA设计中2.5G SDH的接入基于FPGA芯片的收发器实现,结合所需逻辑资源等条件选择Altera公司的EP2AGX45DF29C6N型号的FPGA芯片来做2.5G CPOS的FPGA设计。其主要的处理流程如图2所示。

图2 FPGA处理流程Fig.2 FPGA process procedure

2.2 FPGA模块化设计思路

2.5G CPOS FPGA设计采用模块化设计思路,其处理流程如图2所示,其中:

1)光接口模块:完成特定速率光信号的线路接入,实现光、电信号之间的互相转换。接收端接收2.5G SDH光信号进行光电转换;发送端将155M SDH电信号进行电光转换,发送到线路。因此光模块需要满足2.5G SDH速率光信号接入,根据需求选取光收发器主要参考工作波长、线路速率、传输距离、调制方式等参数,经过调研,选取Finisar的FWLF163121。

2)PMA处理模块:实现串并转换、时钟与数据恢复和帧头定位。接收端接收经过光接口模块处理的电信号,将高速串行数据解复用为低速并行数据便于后续模块进行数据处理;同时时钟恢复单元提取线路时钟,完成数据再定时功能,FPGA收发器完成对线路数据的恢复,满足抖动性能要求,参照ITU-T G.707标准,利用帧头固定字节和寄存器移位对接收到的数据进行重排,并完成帧头定位以便对数据进行下一步的解扰;发送端接收PCS层加扰后的数据,进行并串转换将并行信号转换为高速串行信号送给光接口模块处理。

3)PCS处理模块:主要完成数据加扰解扰码和对收发器件接收的数据进行帧头定位的功能,为后续的数据处理奠定技术基础。该模块主要与PMA子层处理模块和多通道解析、封装模块相连接进行数据通信。接收方向,接收PMA层处理后的数据,完成数据解扰和帧头定位,送给深度多通道解析模块进行处理;发送方向,接收多通道封装模块处理后的数据,完成数据的加扰处理,送给PMA层处理。

4)深度多通道解析模块:CPOS多通道解析技术主要根据G.707所定义的数据映射、复用关系,实现其逆过程,完成对STM-16的2.5G SDH的解析、提取出16个STM-1的155M通道各自的净荷和开销。

5)多通道封装模块:主要根据SDH帧的数据格式,将各通道的净荷和开销拼接成完整的SDH帧,用于在各自对应的线路传输。

6)时钟模块:在PMA层提取线路时钟,为其他模块提供同步的参考工作时钟。

3 关键技术的研究与实现

3.1 接入技术研究

CPOS接入技术主要研究和解决如何将CPOS设备接入,不影响线路的正常工作。主要包含PMA层,PCS层的处理。

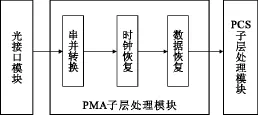

(1)PMA处理

PMA子层处理模块具备2.5G数据收发能力,模块主要完成数据串并转换、时钟恢复、数据恢复等功能,实现光通路层数据接入技术和光通路层再定时技术,是实现CPOS通道化处理的重要前提和基础,其模块功能如图3所示。该模块与光收发器相连接,对内主要是与PCS子层处理模块进行相关数据通信。

图3 PMA子层处理模块功能框Fig.3 Functional block of PMA processing module

接收方向,串并转换实现将2.5G高速的线路数据转换为低速的16位的并行数据,便于后续的数据处理;时钟恢复将完成光通路层线路数据时钟恢复、高速时钟稳定工作以及加密模块与通信设备时钟同步等功能;数据恢复主要是通过移位指示信号控制收发器移位,得到符合G.707标准的数据,为后续的数据处理奠定技术基础。

发送方向,接收来自PCS加扰后的的数据信息,并对数据信号实现相位补偿,减弱来自其他模块的信号与收发器时钟域之间的相位变化,完成低速并行数据到高速串行数据之间的转换,发送至线路接口模块,完成数据物理层上的收发功能。

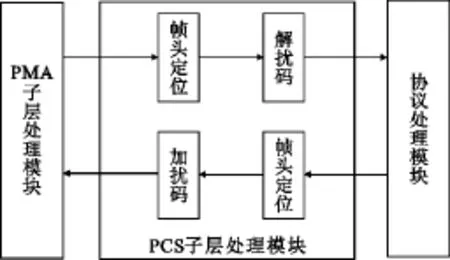

(2)PCS处理

PCS子层处理模块主要完成数据加扰解扰码和对收发器件接收的数据进行帧头定位的功能,为后续的数据处理奠定技术基础,其模块功能框图如图4所示。该模块主要与PMA子层处理模块和协议处理模块相连接进行数据通信。接收方向,完成数据解扰和帧头定位;发送方向,对数据进行加扰。

图4 PCS子层模块功能框Fig.4 Functional block of PCS module

(3)加解扰技术

在SDH帧中,为了防止出现长连“0”或“1”,保证定时恢复的质量[3],保持信号稳定性,保证足够的比特定时含量,必须使用扰码器对信号进行扰码。

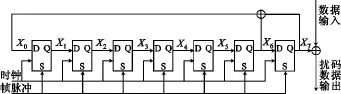

SDH系统中通用的是串行扰码,扰码器的产生扰码多项式:g(x)=1+x6+x7,该8 bit串行扰码器的功能框架如图5所示,然后将产生的扰码多项式与用户数据进行异或,产生加扰或解扰数据,当复位或在帧头位置扰码多项式应该赋为初值16'H04fe。

图5 SDH帧同步扰码器Fig.5 Synchronous scrambler of SDH frame

根据扰码器的多项式以及产生的原理,最后推导出最终16位扰码数据Y[15:0]的结果为:

3.2 多通道解析封装技术研究

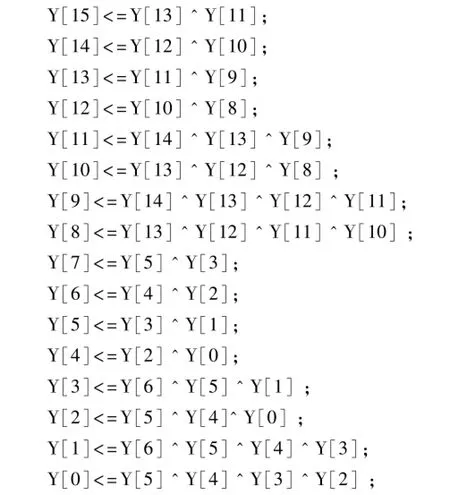

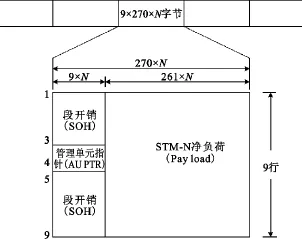

CPOS解析技术主要根据G.707所定义的SDH帧结构图如图6所示[4],数据映射、复用关系如图7所示,实现其逆过程。复用成STM-16的高阶虚容器包括VC4、VC4-4C、VC4-16C。首先将AUG-16/ 4/1从STM-16中分离出来,再根据AUG-N不同的复用路径,针对不同的管理单元进行指针分析,定位各级虚容器在管理单元的位置,再根据虚容器的结构,进一步将虚容器以及承载数据业务的容器从管理单元中分离出来,完成对STM-16的2.5G SDH的协议解析、提取并指示出16个STM-1的155M通道的开销和净荷。

图6 STM-N帧结构Fig.6 Structure of STM-N frame

图7 SDH复用路线Fig.7 Diagram of multiplexing SDH

STM-N是9行×270×N列的块状帧结构,此处的N与STM-N的N相一致,取值范围:1,4,16,…,表示此信号由N个STM-1信号复用而成。STM-N的帧结构由3部分组成:段开销(SOH,Section Overhead),包括再生段开销(RSOH,Regenerator Section Overhead)和复用段开销(MSOH,Multiplex Section Overhead);管理单元指针(AU-PTR);信息净负荷(payload)。AU-PTR是指示信息净负荷的第一个字节在STM-N帧内位置的指针,以便接收端能根据这个指针正确分离信息净负荷。

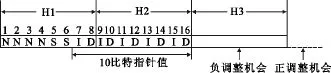

根据STM-16的帧结构,及复用路线图可以看出,将STM-16通道化为16个STM-1需要从STM-16中提取出高阶虚容器VC-4。由于指针调整的缘故,高阶虚容器VC-4的位置是有调整的,从而提取VC-4需要对AU-4进行指针分析。AU-4的指针是由H1和H2组成的16位码组成,3个H3是负调整机会。其定义如图8所示。

图8 AU-4指针Fig.8 AU-4 pointer

在AU-4中以3个字节为一个调整机会单位,因此指针值的范围是0到782,其值指示VC-4中J1的位置。用H1和H2字节的后10比特表示,这10比特又分为I(增加指示比特)和D(减少指示比特)两类,利用它们瞬间取反给出启动指针值调整信息,反转5个I比特出现正调整,反转5个D比特出现负调整,即该帧的后一帧的指针值将加1或减1。从而根据指针调整情况和指针值可定位VC-4的位置,正确提取出VC-4实现通道化处理。

封装技术主要根据SDH帧结构图,将各路STM -1对应的开销和净荷正确拼接起来,形成完整的155M SDH帧,用于在线路传输到各对应支点。

4 结 语

CPOS技术能在“总部-多分支”的网络中减少总部的设备及跳线从而减少故障点,使连接更为简单。用FPGA实现2.5G CPOS的接入、协议解析、

通道化处理、封装等关键技术,为CPOS技术的实际组网应用奠定技术基础。

[1] 于宁.邓煜星.POS技术及发展趋势[J].电信科学, 1999(01):37-39.

YU Ning,DENG Yu-xing.An Overview of Packet over Sonet/SDH[J].Telecommunications Science,1999(01): 37-39.

[2] 徐建光,梅顺良.基于虚容器的SDH专线加密技术研究[J].通信技术,2010,43(05):89-91.

XU Jian-guang,MEI Shun-liang.Encryption Technique based on Virtual Container in SDH Leased Line[J].Communications Technology,2010,43(05):89-91.

[3] 李鹰.STM-4提取VC-12解复用的FPGA设计[J].信息安全与通信保密,2009(03):74-76.

LI Ying.A FPGA-based Design of Multiplexer to Extract VC-12 fromSTM-4[J].Information Security and Communications Privacy,2009(03):74-76.

[4] 邓忠礼.光同步传送网和波分复用系统[M].北京:清华大学出版社,2003.

DENG Zhong-li.Optical Synchronous Transmission Network and Wavelength Division Multiplexing System[M]. Beijing:Tsinghua University Press,2003.

LIU Jian(1988-),male,graduate student, majoring in optical communication networks.

王文胜(1969—),男,研究员,主要研究方向为宽带通信网络。

WANG Wen-sheng(1969-),male,research fellow,mainly engaged in broadband communications network.

Research and Implementation of Key Technology on 2.5G CPOS FPGA Design

LIU Jian,WANG Weng-sheng

(No.30 Institute of CETC,Chengdu Sichuan 610041,China)

With the increase of network scale and requirements of users,the concept of large customers is expanded,and the application of headquarters-branches network becomes become much wider.What kind of access technologies should be used to reduce network maintenance costs and meet customers’demand is now the focus of network construction.Based on the study of CPOS network architecture,the overall solution of FPGA design for 2.5G CPOS network is proposed,with emphasis on the breakthrough of key technologies including access,analysis and channel process.Meanwhile,Altera’s FPGA chip is selected to load onto FPGA chip,thus with QUARTUS II signal acquisition tool Signaltap for sample verification.

CPOS;FPGA;access;analysis;multi-channel

TP311

A

1002-0802(2014)03-0330-05

10.3969/j.issn.1002-0802.2014.03.019

刘 健(1988—),男,硕士研究生,主要研究方向为光通信网络;