一种TD-LTE综测仪中跳频合成器的设计

黄武

(中国电子科技集团公司第41研究所 安 徽 蚌 埠 2 33010)

3GPP组织在LTE系统中定义了3类跳频方式:调度决定频域位置的跳频、分段的伪随机化跳频和镜像跳频。在LTE宽带系统中,跳频技术在上行的数据传输中被采用。LTE系统支持两种跳频方式,一个是子帧间跳频,一个是子帧内跳频。两种方式的区别在于跳频的时间间隔。

在LTE-Advanced中,由于引入了增强MIMO和载波聚合等先进技术,对接收机的带宽要求达到100 MHz的量级,随着带宽的增加,势必影响接收机的诸多性能,特别是干扰、杂散等指标将进一步恶化,从而影响数字调制测量参数如EVM等指标的降低,这也大大损害了接收机的整机性能。所以,在大带宽测量时,往往采取在不改变分析带宽的前提下,通过本振的多次跳变来进行大测量带宽的拟合,保证了大带宽下的接收机的测量指标。

跳频速度的高低直接反映跳频系统的性能,跳频越高抗干扰的性能越好,军用的跳频系统可以达到每秒上万跳。实际上第二代移动通信GSM系统也是跳频系统,其规定的跳频为每秒217跳。出于成本的考虑,商用跳频系统跳速都较慢,一般在50跳/秒以下。由于慢跳频系统实现简单,因此低速无线局域网产品常常采用这种技术。

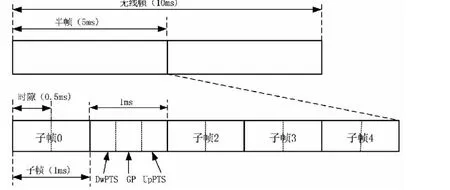

1 LTE的帧结构

LTE的帧结构(TDD)如图l所示。一个10 ms的无线帧由两个半桢构成,每个半帧5 ms,每个半帧由上行子帧、下行子帧和特殊子帧构成。每个子帧长度为1 ms,由两个长度为0.5ms的时隙构成,特殊子帧包含3个部分:DwPTS(下行导频时隙)、GP(保护间隔)、UpPTS(上行导频时隙),其中 GP 是用作上下行子帧转换的保护间隔。DwPTS可以发送下行数据,而GP和UpPTS则不能发送数据。

图1 TD-LTE帧格式结构Fig.1 Configuration of frame for TD-LTE

LTE上行链路通常采用跳频传输方式,即用户在一个子帧的2个时隙中占用不同的频带,并可为LTE上行链路提供额外的频率分集和干扰分集,但是,跳频传输方式也会导致相差法失效。因此,LTE上行链路中的跳频应用也受到一定的限制,要求跳频速度在20 μs以内,才能有效地确保链路最大频偏在其估计范围以内。

近年来,随着大规模集成电路的发展和各种新技术的应用,出现了很多频率合成方案,相应的带来了跳频技术的快速发展,目前归纳起来,实现跳频频率合成的基本方法有三种:直接频率合成法、锁相频率合成法和直接数字合成法。其中直接频率合成法所用模拟器件多,实现过程中用到大量的开关、混频器和滤波器,带来了体积、功耗、屏蔽措施、制作工艺等相关要求,所以大规模集成较为困难,特别是体积和重量的限制,在90年代有被淘汰的趋势,现今随着工艺的进步又出现生机;直接数字合成法(DDS)的特点是可获得极高的频率分辨率,频率切换时间极短,便于集成;缺点是合成频段较低,输出带宽也受到限制,且输出杂散难以解决[1]。目前代表产品有AD公司的AD9858、AD9910等产品,其输入最高时钟频率达到2GHz,输出最高合成频率在450 MHz左右。综上所述,目前研究最深、应用最广的跳频频率合成方式仍是锁相频率合成法[2]。

2 环路参数的影响

锁相跳频频率合成关注的技术指标有:输出频率范围、输出频率分辨率、频率杂散、相位噪声与跳频速度等。针对这些参数分别采用不同技术来达到设计要求,在环路中采用可编程分频器,提高输出频率;采用小数分频技术解决分辨率问题;改变环路带宽,利用环路的窄带滤波特性,来抑制相位噪声和杂散,提高信号的频谱纯度[3]。本文主要讨论通过改变环路的特性参数,加快环路的锁定时间,从而提高频率切换时间,满足TD-LTE综合测试仪的跳频要求。

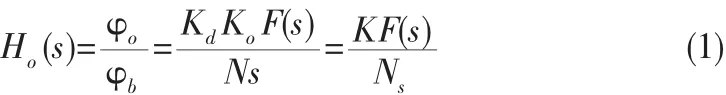

锁相环环路相位模型如图2所示,根据锁相环理论,可推得二阶环的开环传递函数为[1]:

图2 锁相环环路相位模型Fig.2 Model of phase for pll

其中 φi为参考输入相位,φo为输出相位,φe为鉴相输出相位差,φb为反馈相位,Kd为鉴相器增益,F(s)为环路滤波器传递函数,N为分频器分频比,Ko/S为VCO的线性模型。

其闭环传递函数为:

ωn和ξ是环路的两个重要参数,与锁相环的锁定时间相关,由闭环传递函数公式通过拉普拉斯变换的终值定理可以推出环路锁定时间的表达式。

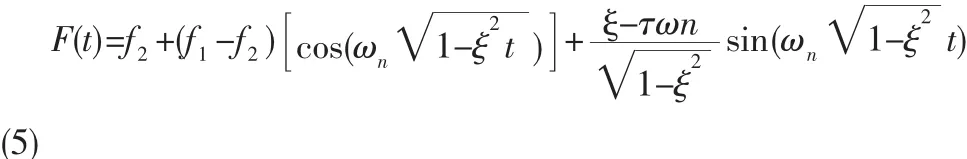

设频率从发f1跳到f2,通过拉普拉斯反变换得到频率阶跃响应为:

从上式可以看出,环路锁定时间与频率跳变范围、阻尼系数和环路固有频率相关,与频率跳变范围成正比,与成反比关系。

可见,在可调的参数范围内,锁相环频率合成器的跳频速度主要由其带宽决定,如何增加环路带宽而又不降低其他指标,成为提高其跳频速度的主要方法。与其对应,变带宽技术在频率合成和锁相技术中被大量的探讨。如果一味地增加环路带宽,将势必损害输入信号频谱纯度,变带宽虽然可以通过改变环路中任何一部分来实现,但主要是由鉴相器和环路滤波器来完成。改进鉴相特性,增加鉴频功能,可扩展环路的捕捉带宽,有利于缩短频率捕获时间。当环路未锁时,增加环路带宽,使频率切换时间减小,同时缩小鉴相时的频差,缩小环路的捕获时间,加快了跳频时间。一般当环路锁定后,恢复或减小环路带宽以抑制相位噪声和杂散[4-5]。

3 实现方案

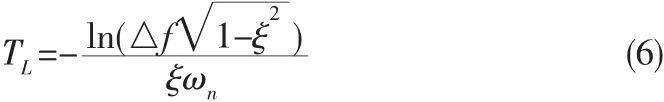

本方案在基本锁相环的基础上增加跳频预置电路,如图3所示。当LTE综测仪工作在非跳频状态下,本振工作在锁相状态,保证寄生、杂散等指标;当LTE综测仪工作在跳频状态时,本振切换增加跳频预置电路,来改善环路参数提高跳频速度。

图3 锁相环跳频预置原理图Fig.3 Pll frequency hopping preset schematics

根据锁相环理论,锁相环频率合成器的频率切换过程,分为频率捕获与相位跟踪两阶段。频率捕获时间与初始频差有关。相位跟踪时间由环路参数决定,实际运算可知,频率捕获时间远大于相位跟踪时间[6],增加预调DAC,就是通过减小初始频差来缩短占据频率切换过程主要时长的频率捕获时间,相当于微波电路中YTO的预置一样,拉近了初始频差。当LTE综测仪工作在跳频状态时,在开始跳频前,LTE综测仪增加了一个跳频学习过程,即在每一个跳频频率点,由跳频码寻址,获得其在环路锁定状态下相对应的预调电压值,经CPU存入跳频RAM中,在跳频过程中,强迫VCO在新的频率附近振荡,这样就达到了减小频差,提高跳频速度的要求[7]。

4 实验结果

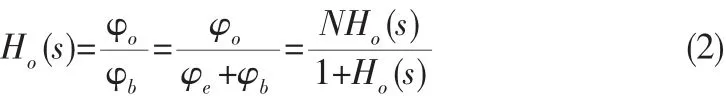

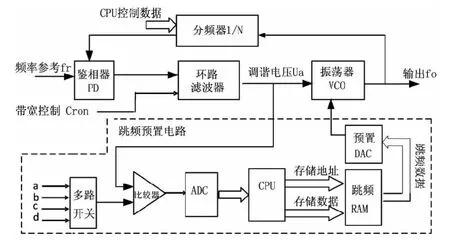

本方案应用于某TD-LTE综合测试仪中的跳频合成器中可达到如下指标:在合成器的单频段频率跳变时间的典型值为16 μs;而整个合成器的频率切换时间还受到调制带宽的限制,跳频的快慢与载波频率高低有关。跨频段频率跳变时间的典型值为100 μs。图4为本装置在设置4个跳频点进行频率跳变时,用实时频谱仪实测的跳频速度值,3个时间间隔测量值为46 μs,即每两点之间的跳频时间约为16 μs。满足LTE综测仪对跳频速度的设计要求。

图4 跳频速度测量Fig.4 Hopping speed measurement

5 结论

本文提出了一种改善锁相环路参数,提高频率切换速度的方法,该方法是通过增加跳频前的预置,动态调整VCO的预置电压,从而得到改善环路的锁定的牵引条件、缩短环路频率捕获的锁定时间,提高频率合成器跳频速度指标。通过实验表明,该方案实现的LTE综测仪频率切换速度达到了16 μs的量级,与国外先进的跳频仪表相当,完全可以满足TD-LTE综合测试仪对跳频速度的要求。

[1]黄智伟.锁相环与频率合成器电路设计[M].西安:西安电子科技大学出版社,2008.

[2]蓝天,张金林.直接数字频率合成器DDS的优化设计[J].电子技术应用,2008(1):23-25.LAN Tian,ZHUANG Jin-lin.Optimal design of direct digital frequency synthesizer of DDS[J].Application of Electronic Technique,2008(1):23-25.

[3]张克舟,陆洪涛.基于AD9910的宽带捷变频频率合成器设计[J].国外电子测量技术,2011,30(8):73-76.ZHANG Ke-zhou,LU Hong-tao.AD9914-based wideband agile frequency shnthesizer design [J],Foreign Electronic Measurement Technology,2011,30(8):73-76.

[4]周研,刘祖深.基于双DDS跳变的捷变频率发生器的设计[J].电子测量与仪器学报,2010,24(6):90-94.ZHOU Yan,LIU zu-shen.Design for DDS-based dual-hopping frequency generator[J].Journal of Electronic Measurement and Instrument,2010,24(6):90-94.

[5]梁强,杨永跃.捷变微波频率合成器的设计[J].国外电子测量技术,2006:39-42.LIANG Qiang,YANG Yong-yue.Agile microwave frequency synthesizer design[J].Foreign Electronic Measurement Technology,2006:39-42.

[6]向浩,姚远.跳频电台综合测试技术[J].国外电子测量技术,2010,29(10):39-43.XIANG hao,YAO yuan.Hopping radio technology integrated test[J].Foreign Electronic Measurement Technology,2010,29(10):39-43.

[7]张波,邵定蓉.跳频快速捕获技术[J].电子测量技术,2005,3(2):65-73.ZHANG Bo,SHAO Ding-rong.Hopping quick capture technology[J].Electronic Measurement Technology,2005,3(2):65-73.