FPGA 实现海德汉绝对式编码器与上位机的智能通讯

陈 琳,钟 文,韦庆情,潘海鸿,罗海国,黄炳琼

(1.广西大学,广西南宁530004;2.广西制造系统与先进制造技术重点实验室,广西南宁530004)

0 引 言

随着现代工业快速发展,精密数控机床、工业机器人等工厂设备对伺服驱动系统提出越来越高的要求,准确测量控制对象的位置信息对提高伺服系统的控制精度十分重要[1]。光电编码器具有精度高、惯量小、稳定性好等优点被广泛应用于需要检测角度的装置和设备中,如回转台、数控机床、机器人等[2]。

绝对式编码器作为一种融合数字技术的精密测角装置,其输出位置值和电机轴的位置一一对应,便于记忆和保存,且可实现快速、及时、准确的位置检测与控制[3]。绝对式编码器数据输出方式一般采用串行通讯方式。EnDat 接口协议采用全双工同步串行数据传输方式,具有连线简单、传输速度快、抗干扰能力强等优点,通常作为海德汉编码器、光栅尺的通用数据传输接口协议,并已成为行业标准[4]。海德汉公司提供专用数据处理芯片供用户使用,即将海德汉绝对式编码器输出的串行信号输送到上位机控制器中处理,但该芯片通常价格比较昂贵。为了实现EnDat 绝对式编码器与上位机之间的通讯,提出采用FPGA 实现对EnDat (EnDat 2.1 和EnDat 2.2)绝对式编码器通讯接口电路设计。

1 EnDat 接口协议介绍

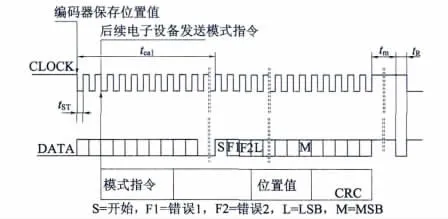

海德汉编码器的双向数字接口——EnDat 接口,不仅能给绝对式和增量式编码器传输它们的位置值,而且还可以传输或更新在编码器中所存储的信息。EnDat 接口协议典型时序如图1 所示[5],数据帧传输周期从时钟信号CLOCK 的第一个下降沿开始,编码器就开始保存测量值并且计算位置值;两个时钟信号周期后,编码器接收后续电子设备发送的模式指令;经tcal时间后,编码器从S 开始向后续电子设备进行数据的传输;图1 中错误位F1 和F2一般只存在EnDat 2.2 指令中,它们是检测类信号,表示编码器发生可导致不正确位置信息的故障;编码器从最低有效位(LSB)开始发送绝对位置值,直到发送完5 位循环冗余校验码(CRC),这才完成一个传输周期的数据帧传输。

图1 EnDat 接口典型时序图[5]

在数据帧结尾处,通常时钟信号和数据信号必须被置为高电平,再经过tm时间后,数据信号由高电平变为低电平,维持低电平tR时间之后,时钟信号才可以再次启动新的一次数据传输。编码器恢复时间tm通常为10 μs 到30 μs,但采用EnDat2. 2 接口的编码器可通过参数设置将编码器的恢复时间tm设置为1.25 μs 到3.75 μs;tR最大为500 ns。

2 EnDat 绝对式编码器智能通讯接口设计

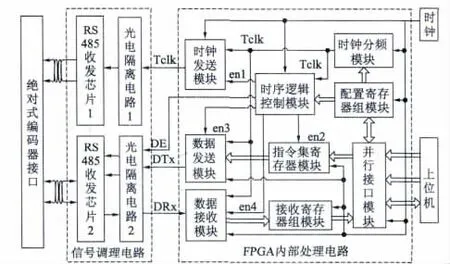

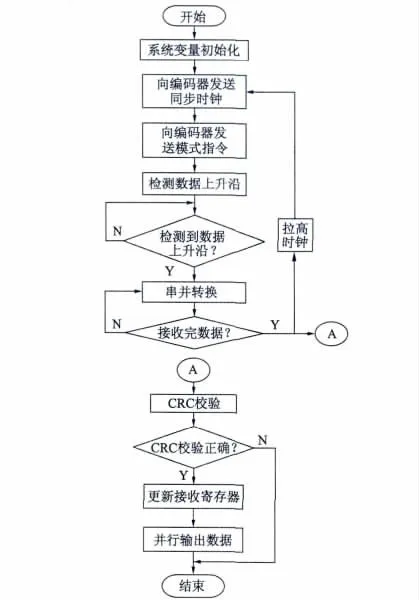

基于FPGA 芯片的EnDat 绝对式编码器智能通讯接口结构框图如图2 所示。其包括绝对式编码器接口、信号调理电路、FPGA 内部处理电路、上位机和时钟。绝对式编码器接口外接EnDat 绝对式编码器;信号调理电路由RS-485 收发芯片1、RS-485收发芯片2、光电隔离电路1、光电隔离电路2 组成;以FPGA 芯片为核心,实现编码器与上位机的智能通讯。在Altera 公司Quartus II 7.2 集成环境下运用硬件描述语言[6]Verilog HDL 编写程序完成所设计的整个FPGA内部处理电路功能模块(图2):并行接口模块、配置寄存器组模块、时钟分频模块、时序逻辑控制模块、时钟发送模块、指令集寄存器模块、数据发送模块、数据接收模块和接收寄存器组模块,实现EnDat 绝对式编码器输出串行数据的解码转换等处理;其主程序流程图如图3 所示。

图2 EnDat 绝对式编码器通讯接口结构框图

图3 FPGA 内部处理电路的主程序流程图

结合图2 中对FPGA 中各个功能模块阐述如下。

时钟分频模块可以根据配置寄存器组模块中的配置信息值,对输入的时钟信号进行分频产生所需频率的同步时钟信号Tclk。

在可编程逻辑器件完成初始化后,时序逻辑控制模块产生使能信号en1、en2、en3、en4 和DE。当使能信号en1 有效时,时钟发送模块接收同步时钟信号Tclk,并将该同步时钟信号Tclk 由光电隔离电路1、RS-485 收发芯片1 发送到绝对式编码器接口;使能信号en2 有效时,指令集寄存器模块根据并行接口模块发送的指令选择信号对指令集寄存器模块中存储的并行模式指令进行选择,并将选择的并行模式指令输送给数据发送模块;使能信号en3 有效时,数据发送模块将指令集寄存器模块输出的并行模式指令转换为串行模式指令DTx,该串行模式指令DTx 经光电隔离电路2 和RS-485 收发芯片2发送到绝对式编码器接口;使能信号en4 有效时,数据接收模块开始检测经绝对式编码器接口、RS -485 收发芯片2、光电隔离电路2 传输来的串行数据DRx 的上升沿,一旦上升沿到来说明接收到数据起始位S,启动数据接收模块接收串行数据DRx,并对该串行数据DRx 进行串并转换和CRC 校验,且将校验正确的并行数据更新到接收寄存器组模块;使能信号DE 用于控制切换RS-485 收发芯片2 的工作状态。

由于EnDat 传输的数据类型分为位置值、位置值及附加信息或参数,且编码器发送的数据类型由后续电子设备发送给编码器的模式指令决定。因此,基于FPGA 所设计出的EnDat 绝对式编码器智能通讯接口具有多种工作状态,以满足不同的数据帧格式要求。其工作状态包括:读编码器位置值、读编码器位置值及附加信息、读编码器参数等。这些工作状态可以由上位机通过并行接口模块向配置寄存器组模块写入配置信息值:发送给编码器同步时钟的频率信息值、编码器传输位置值所需的时钟脉冲数信息值等。这些配置信息值分别被传送给时序控制模块和时钟分频模块进而产生相应的使能信号en1、en2、en3、en4、DE 和所需频率的同步时钟信号Tclk。

3 实验与结果

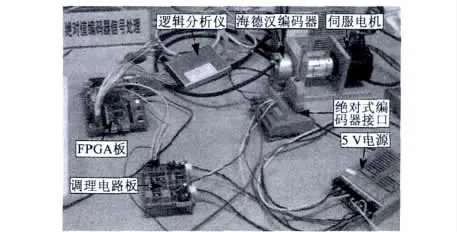

根据图2 搭建基于FPGA 的EnDat 绝对式编码器智能通讯接口实验平台,如图4 所示。伺服电机型号为SGMPH-01A1A21;海德汉绝对式编码器型号是ECN1313,遵循EnDat 2.2 数字接口协议,绝对位置值为13 位;调理电路板实现海德汉绝对式编码器输出信号进行差分变单端、光电隔离等调理左右;采用EP1C6Q240C8 型芯片作为FPGA 板核心,根据图1~图3 编程实现智能通讯接口;实验过程中用逻辑分析仪采集FPGA 输出信号进行实验结果分析。

图4 EnDat 绝对式编码器智能通讯接口实验平台

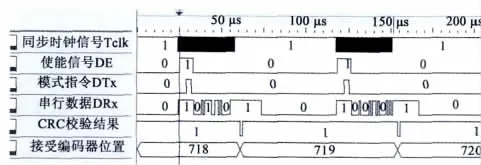

实验中,编码器智能通讯接口数据传输速率设定为1 MHz,数据采集结果如图5 所示。图5 中使能信号DE 为高电平时RS-485 收发芯片2 切换为发送状态;当DE 为低电平时,RS-485 收发芯片2切换为接收状态,FPGA 接收串行数据,并进行串并转换和CRC 检验;当CRC 校验结果为低电平表示一帧数据传输正确,并将该帧并行数据更新到接收寄存器组模块。图5 中接收到编码器位置值以1 为基数递增,表示伺服电机正方向旋转。

图5 实验数据采集图

上述实验结果证明,所提出的基于FPGA 的EnDat 绝对式编码器通讯接口设计方案可行,能够完成对EnDat 绝对式编码器输出的串行数据进行串并转换、CRC 校验等处理,并可实现EnDat 绝对式编码器与上位机之间的智能通讯。

4 结 语

根据海德汉公司EnDat 接口协议,采用Verilog HDL 语言设计出基于FPGA 的EnDat 绝对式编码器智能通讯接口。通过实验平台验证了所设计的智能通讯接口可完成对接收到的串行数据进行串并转换、CRC 校验等处理,实现EnDat 绝对式编码器与上位机之间的通讯。此外该设计可通过改变FPGA内部配置寄存器组模块中的配置信息值,进而改变接口工作状态,可连接不同型号的EnDat 绝对式编码器。这表明基于FPGA 的智能通讯接口具有很强的实用性,可以替代专用接口芯片,为实现通过上位机获取电机准确的位置信息提供一种新的方法。

[1] 马有良,任同.光电编码器脉冲检测电路设计[J].仪表技术与传感器,2009(10):76-77.

[2] 刘琳,陈建平.通过ENDAT 接口获取绝对编码器位置[J].微电机,2009,42(12):77-79.

[3] 史敬灼,王秀丽,徐殿国.交流伺服系统光电编码器信号处理电路设计与实现[J].微特电机,2007,35(11):18-19.

[4] Heidenhain.Endat 2.2 position encoder bi-directional interface[M].Heidenhain 公司,2011.

[5] Heidenhain.Endat 2.2 位置编码器双向数字接口[DB /OL].http:/ /www.haidenhain.com.cn.

[6] 夏宇闻.复杂数字电路与系统的Verilog HDL 设计技术[M].北京:北京航空航天大学出版社,1999.