一种基于NIOSⅡ处理器的频谱分析系统设计

(1.赣南师范学院科技学院,江西赣州341000;2.郑州铁路职业技术学院,郑州450052)

(1.赣南师范学院科技学院,江西赣州341000;2.郑州铁路职业技术学院,郑州450052)

介绍基于NIOSⅡ频谱分析系统采用离散傅立叶变换(DFT)算法原理。该系统利用NiosⅡ软核处理器,加上LCD、键盘、AD芯片、滤波器和简单的外围电路,完成了信号的采集、处理和数字DFT,并把结果送到LCD显示。测试结果表明,本频谱分析系统能分析带宽为0~5MHz的信号,分辨率达到1Hz。本系统具有性能稳定、结构简单、操作方便、可在线升级和成本低的优点。

频谱分析;DFT;NIOSⅡ;FPGA

频谱分析是微电子测量领域中最重要的测量参数之一,目前市场上的频谱分析系统多以硬件电路来实现,其内部结构复杂,而且是不可升级的封闭系统,而且价格昂贵[1]。本系统使用 Altera公司的NiosⅡ软核处理器实现CPU,利用FPGA实现DFT,在FPGA上实现整个系统的构建。关键的硬件模块使用用Altera公司软件QuartusⅡ完成设计。整个频谱分析系统利用利用NiosⅡ软核处理器通过Avalon总线进行控制。

1 离散傅立叶变换(DFT)算法原理

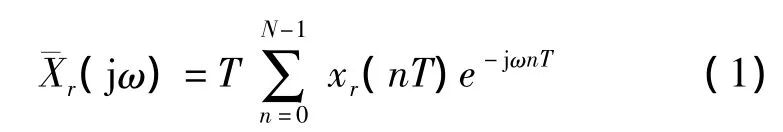

设χr(t)为连续信号,最高频率为fa,持续时间为T。通过对χr(t)以T为采样间隔进行采样可以得到。如果采样N后对Xr(jω)作零阶就可以得到[2]:

对区间进行采样间隔为M采样N点,此时采样频率fc=MN,把f=kM代入式(1)后,令,通过对连续信号采样进行DFT并且乘上T的近似方法得到频谱特性:

信号的频谱可以表示为:

采样速度fc满足fc>2fa时可以避免DFT运算时发生频率混叠现象。增加记录时间和采样点数可以提高谱的分辨率,同时谱分析的范围不会减少。提高分辨率的条件是满足时域采样定理,采样频率fc最好是最高频率fa的3倍~5倍[3]。

2 系统硬件设计

2.1 系统整体硬件设计

系统是基于NIOSⅡ系统实现的。整机设计方案如图1所示,包括:预处理电路、AD电路、在FPGA上实现的NIOSⅡ系统和DFT处理模块、SDRAM芯片、TFT-LCD。其中NIOSⅡ系统是核心,与液晶显示模块、键盘和D/A转换器等外围部件构成了一个完整的主控系统。

图1 NIOSⅡ系统整体方框图

2.2 NIOSⅡ系统制定

设计里采用具有低静态和动态功耗低优点的Altera公司的cycloneⅡ型号FPGA芯片。在QuartusⅡ平台上完NIOSⅡ的制定。

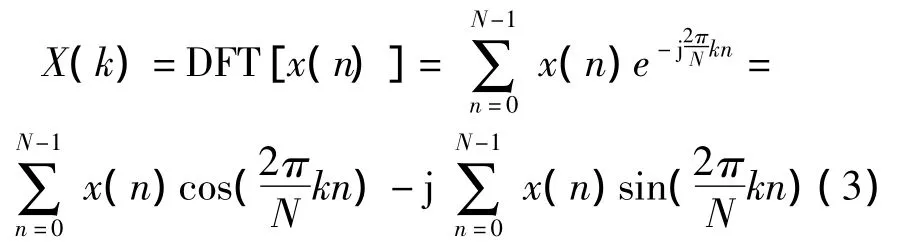

需要定制的内容包括一个NiosⅡ嵌入式处理器、一个JTAG UART、Avalon总线、SDRAM、UART(RS-232)、I/O口、System ID[4]。完成定制后NiosⅡ系统的模块信息列表如图2所示。

图2 NiosⅡ系统模块信息列表

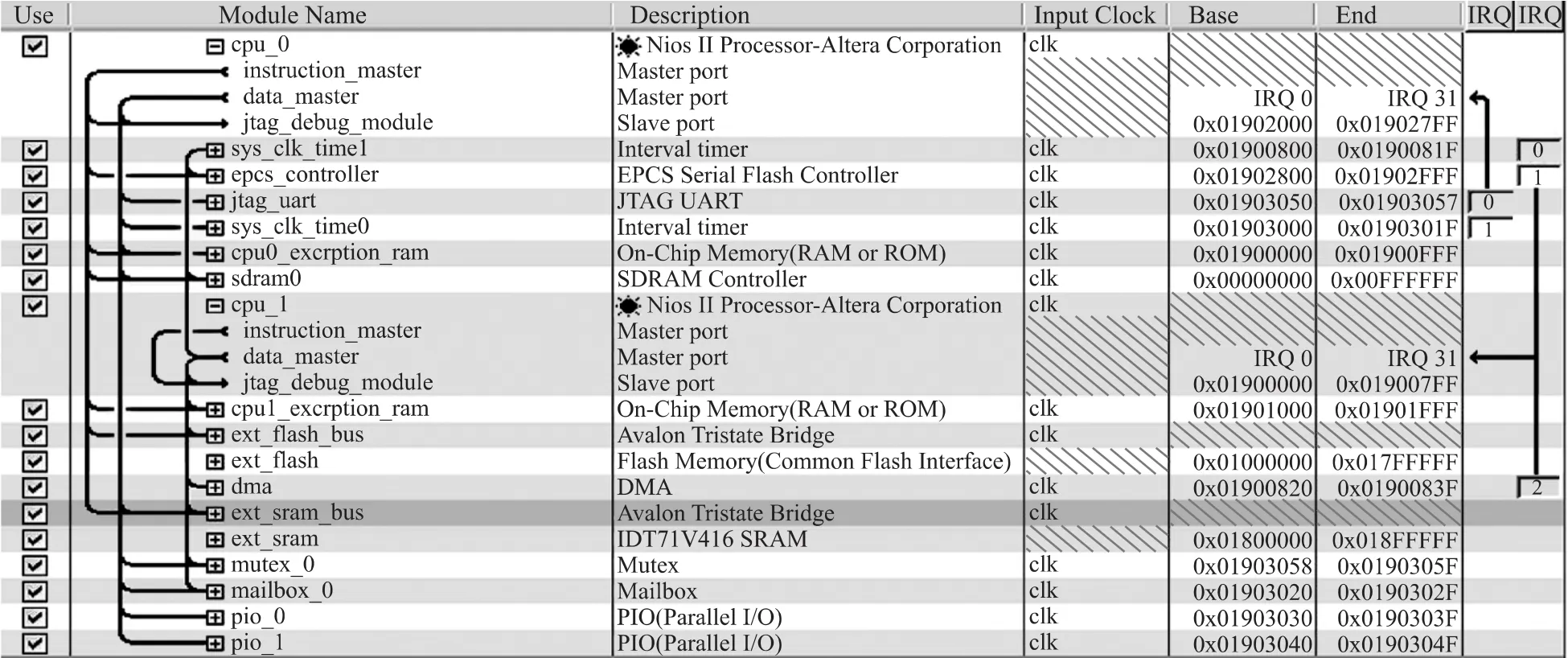

2.3 DFT模块设计

DFT模块的主要功能不但要进行DFT转换,还要控制采样速率、保持波形和数据存储。内部主要包括乘累加器、平方器、加法器和开方器4部分。首先经过乘累加器(MULT_ADD)计算x(n)× sin和x(n)cos,计算结果通过平方器(MUL)和加法器(ADD)可以的到|X(k)|2,然后再使用开方器开方就能得到相应的|X(k)|,从而实现DFT变换[5]。在 FPGA内部建 16 bit双口RAM用来存储数据(数据位由8 bit增加到16 bit)。这样使刷新数据和显示读出数据能实现了同时进行,所以不会产生逻辑冲突。其DFT模块连接图如图3所示。

2.4 语音信号与处理电路

语音信号与处理电路图4所示,前置放大器由INA163实现,通过调节R g改变放大倍数,采用固定增益的超低电压、TPA6102实现语音信号的二级放大。使用电阻分压实现预处理信号的幅度调整[6]。

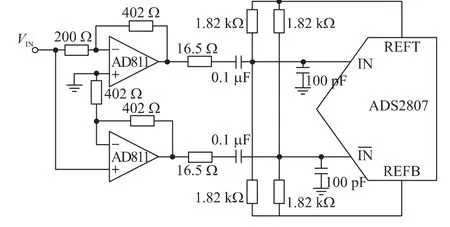

2.5 AD设计

选用高速A/D转换器ADS2807做为A/D转换器,这种A/D转换器的最高采样时钟为50Msample/s。高速运放AD811可以提供适当的输入信号增益,用来匹配输入电压的范围[7]。A/D转换器硬件电路如下图5所示。

图3 DFT模块

图4 语音信号预处理电路

图5 AD转换电路

3 系统软件设计

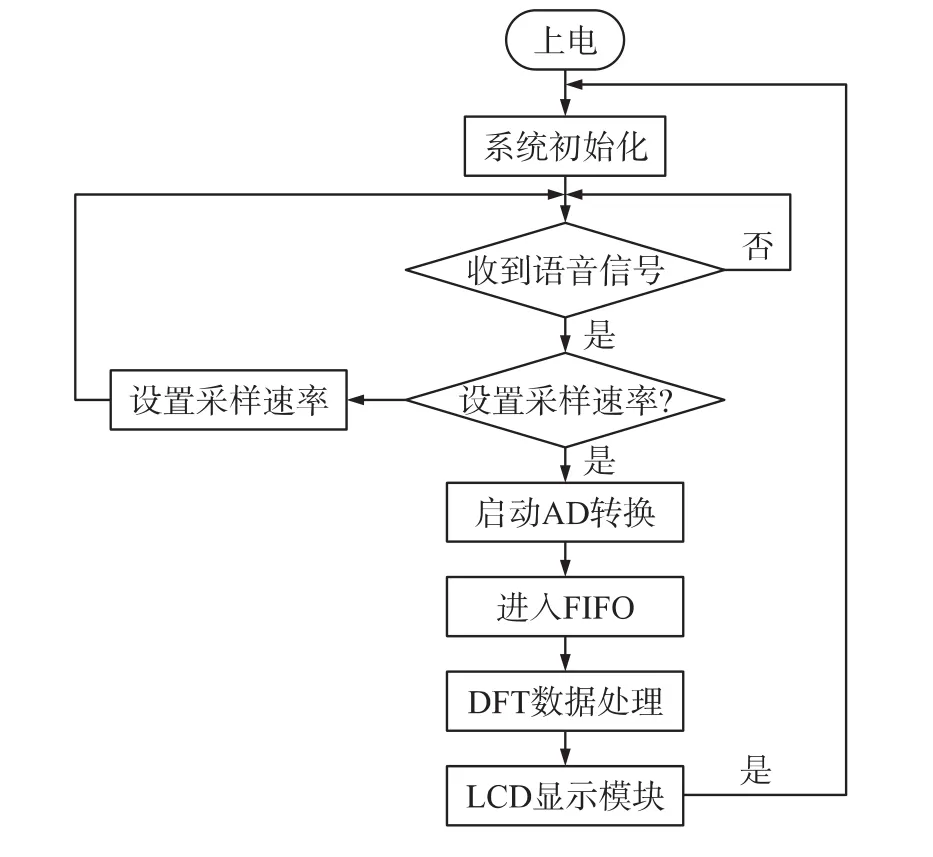

系统软件流程框图如下面图6所示,软件系统实现的主要功能有:液晶显示驱动和对键盘进行扫描与信号预处理以及DFT数据处理,其中DFT计算和数据处理是核心功能。

图6 系统软件流程框图

系统软件部分运用Verilog HDL与C语言相结合的方式编写,最终在SOPC Builder和QuartusⅡ环境下完成定制[8]。

点击开始后系统进行初始化,软件检测声音信号,系统按照预先设定采样速率进行数据采集,然后启动A/D,存数据进FIFO,系统通过总线把数据传输到DFT模块进行数据处理与计算。最后将结果输送到LED显示[9]。

4 测试结果和结论

4.1 测试结果

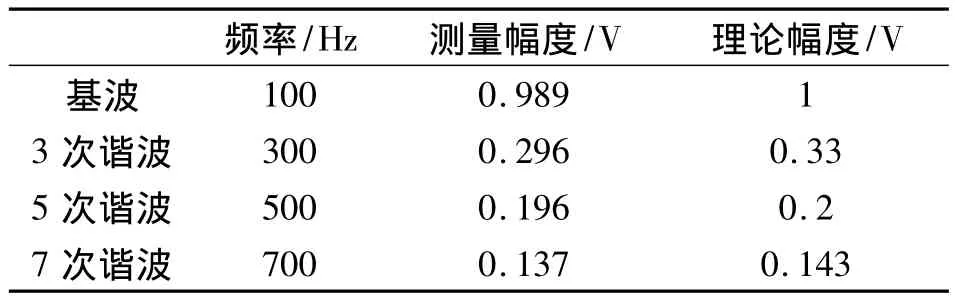

通过给频谱分析系统输入一个峰-峰值为2 V、频率为100 Hz的方波信号来验证本系统的正确性,具体的显示结果如图7所示。

图7 测试结果

显示的结果表明频谱只有奇次谐波,并且基波、三次谐波、五次谐波和七次谐波的幅值和方波理论频谱基本吻合,也就是幅值满足1、1/3、1/5、1/7的理论数值[10]。测量值和理论值的对比结果如表1所示。

表1 幅度测量值与理论值比较

本频谱分析系统显示的频谱图正确,幅度测试的误差较小,能够完成信号频谱的测量,达到了预期设计的要求。

4.2 结论

本系统利用NiosⅡ软核设计CPU控制系统,数字DFT的算法是在FPGA内部完成。这样不但能够实时进行信号处理,而且节省了硬件资源;可以根据实际的需要对模块进行替换升级,可以应用在不同的领域;系统实现了片上设计,降低了系统成本。系统运行稳定,具有很好的应用前景。

[1]刘祖深.频谱分析仪全数字中频设计研究与实现[J].电子测量与仪器学报,2009,23(2):39-45.

[2]陈小桥,胥鸣,葛文丽.基于FPGA的数字频谱分析仪的设计与研究[J].武汉大学学报(工学版),2010,43(2):269-272.

[3]宋泽琳,郑恩让,马令坤.基于NiosⅡ处理器的液晶显示接口及驱动程序设计[J].液晶与显示,2011,26(2):205-209.

[4]赵擎天,尉广军,姚义.基于SOPC的多路并行同步数字信号采集系统设计[J].军械工程学院学报,2010,32(7):96-99.

[5]傅中君,周根元,陈鉴富.基于准同步DFT的非整数谐波分析算法[J].仪器仪表学报,2012,33(1):235-240.

[6]黄翔东,王兆华.全相位FFT相位测量法的抗噪性能[J].数据采集与处理,2011,26(3):286-291.

[7]周文委,王涌.一种DDS信号发生方法与频谱研究[J].电子器件,2009,32(6):620-622.

[8]任全会,黄根岭.基于SOPC全相位FFT相位差测量系统研究与实现[J].电测与仪表,2012,49(11):30-34.

[9]章坚武,赵琪,邹婧媛.避免干扰的低能耗无线传感器网络动态频谱分配算法[J].传感技术学报,2009,22(10):1481-1485.

[10]袁慧梅.非正弦无功功率计算的FPGA设计与实现[J].电测与仪表,2012,49(1):90-93.

一种基于NIOSⅡ处理器的频谱分析系统设计

黄成华1*,付 涛2

Design of Spectrum Analyzer System Based on NIOSⅡProcessor

HUANG Chenghua1*,Fu Tao2

(1.College of Science and Technology,Gannan Normal University,Ganzhou Jiangxi341000,China; 2.Zhengzhou Railway Vocational and Technical College,Zhengzhou450052,China)

A realization method for spectrum analyzer system of NIOⅡ is introduced.The system uses the Discrete Fourier Transform(DFT)algorithm principle,and NiosⅡsoft-core processor,coupled with the LCD,keyboard,AD chip filter and a simple external circuit to complete signal acquisition,signal processing,digital DFT,and displays the data on the LCD with the help of LCD,The test results shows that the spectrum analyzer system can analyze the signal bandwidth of 5MHz resolution of 1Hz.This system has a stable performance,simple structure,convenient operation,online upgrade and low cost advantages.

spectrum analyzer;DFT;NIOSⅡ;FPGA

10.3969/j.issn.1005-9490.2013.06.018

TP317.4;TN911.73 文献标识码:A 文章编号:1005-9490(2013)06-0833-04

2013-07-01修改日期:2013-07-25

EEACC:6140;7210

黄成华(1978-),男,汉族,江西赣州人,赣南师范学院科技学院工作,实验师,通信与信息系统硕士(南昌大学),研究方向为电子通信、计算机技术,gzhuangchenghua@163.com;

付 涛(1980-),男,汉族,河南洛阳人,硕士,讲师,主要研究方向为电子工程,传感检测,电子测量。