IXP425和DM642的会议电视多点控制单元硬件设计*

宋庆恒,王晓鹏

(怀化学院 物理与信息工程系,怀化 418008)

引 言

“会议电视系统”是指多个不同地方的人或者群体,通过通信线路以及多媒体通信设备,将声音、影像以及文字资料互相传送,实现即时和互动的沟通,从而达到完成传统的地点集中式会议目的的系统。采用会议电视的方式,可以使身处多个会场的与会者,既能听到其他会场人员的声音,又能看到其他会场的图像,与会人员可以通过音/视频传输通信来发表意见、观察对方形象,另外可出示实物、图纸等增强现场感,还可以通过传真或共享电子白板等方式及时传送相关文件、图表或讨论问题等,缩短与会者之间的空间距离,改善会议气氛,使与会者都能身临其境,如同在一个地方开会一样[1]。

会议电视系统主要由终端设备、传输通道(通信网)以及多点控制单元MCU(Multipoint Control Unit)组成。其中多点控制单元是会议电视系统的核心部分,它的作用相当于计算机网络里的交换机。交换机将来自各会议场点的信息流,经过同步分离后,抽取出音频、视频、数据等信息和信令,再将会议场所的信息和信令,送入各处理模块,完成相应的音/视频混合或切换、数据广播和路由选择、定时和会议控制等过程,最后将会议地点所需的各种信息重新组合起来,送往各会议电视终端。本论文立足于设计一个成本较低、运行较稳定、功能较全、容量较大、运算速度较快、兼容性好、安全性较好、操作简单、能在2M网络带宽下运行的针对中小型用户的嵌入式会议电视多点控制单元。

会议电视多点控制单元(MCU)的主要功能是:

① 媒体控制、媒体处理:包括音视频的提取,音频和视频的重新编码、混合、切换等,数据的广播和路由选择,语音激励的计算以及其他需要的媒体功能;

② 可接收其他多点控制单元转发的音视频数据,重新进行音/视频切换或混合后发送到会议电视终端进行解压解码,还原成声音、影像和计算机数据后进行本地输出;

③ MCU和终端遵循协议(如 H.323、SIP等)进行连接;

④ MCU和终端可接收对方发送的控制信号并进行响应;

⑤ 网络接入功能;

⑥ 可通过RS232进行参数设置。

1 方案设计

方案1:参考文献[2]中提出了一种基于TCP/IP协议的桌面视频会议系统中多点控制单元的实现方案,该方案采取纯软件式结构,方案成本低,开发周期短,但该方案处理音视频路数有限,画质较差。

方案2:参考文献[3]中提出了一种基于DSP-642的会议电视硬件平台方案,设计和实现了基于H.264协议的像素域多画面合成的PCI通信模块、视频编解码模块,但容量只有4路,画质一般。

综合比较以上2种方案,结合本会议电视多点控制单元MCU的具体情况,本文设计的会议电视多点控制单元MCU采用Intel嵌入式处理器IXP425作为主控制器,采用4片DM642芯片作为数据处理芯片,主控制器与数据处理模块之间采用PCI总线进行通信。这种方案开发周期相对较短,TI、Intel等芯片厂商提供了完善的软硬件开发包,另外由于采用PCI总线连接主控制器模块和数据处理器模块,数据传输速度快,吞吐率高。

2 系统设计

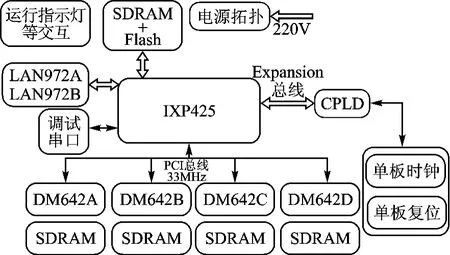

系统框图和采用的功能芯片如图1所示。系统主要由控制模块和音/视频处理模块组成。

图1 系统框图

控制模块由单板上的IXP425+CPLD组成。负责单板的资源和信息管理,把从业务单板发送过来的音/视频信号转发给相应的DM642处理。单板CPLD主要实现单板的复位、时钟检测、片选信号控制、寄存器读写、单板信息等功能。音/视频处理模块由单板上4片DM642完成,是单板的核心模块。决定音/视频处理模块性能的有两个关键因素:音/视频算法性能以及PCI总线的传输性能。

为了增强PCI总线的传输性能,可从如下两个方面改善:提高PCI总线传输效率;PCI总线上任何一个器件都可以作为主器件发起传输,这样DSP芯片之间的数据传输不用通过IXP425转发,节约总线带宽。

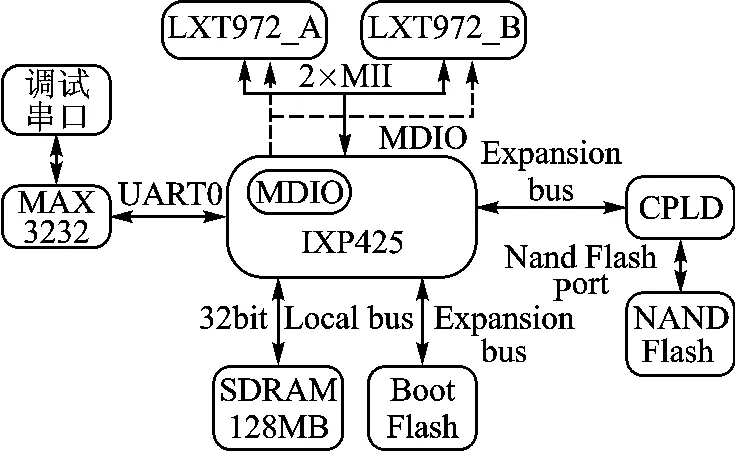

2.1 IXP425模块

IXP425模块主要包含CPU最小系统、CPLD控制模块、调试模块、网络管理模块等。框图如图2所示。

图2 模块框图

IXP425自身具有Expansion总线,能使flash、HPI总线设备、SDRAM等设备与内部ASHB挂接,可兼容Intel/Motorola等制式接口,有cs[7:0]8个bank选择,每个块大小为16MB,若采用WinCE操作系统,Flash空间则至少在20MB以上,故最小系统设计时利用了cs0及cs1两个bank作为系统存储空间。为了给程序下载模式留下足够的存储空间,又增加了两片16MB的Flash。Flash连接如图3所示。

图3 最小系统Flash连接框图

由于IXP425内置了专用的SDRAM控制器,根据其接口原则,同时考虑到平台对运算性能留有一定余量,最小系统中对SDRAM部分的设计选用了2片32MB的SDRAM,硬件兼容128MB的SDRAM设计。

2.2 网口设计

IXP425内部有3个与XScale核并行工作的网络处理机NPE,能对外部提供2个MII接口,并行工作的原理使得网络处理性能较好,支持 协议内容,标准的接口只需外接PHY物理接口芯片,平台中采用了Intel的LXT972A,即能完成与外界数据的交互。当然,变压器的使用也是必须的,利用了 HALO生产的TG110-S050N2与RJ45接口挂接,连接示意图如图4所示。由于IXP425内置了MAC控制器,完善的MII接口使得平台的网络应用比较简单而具有针对性。

图4 网口连接示意图

2.3 音/视频处理模块设计

2.3.1 PCI接口设计

IXP425PCI控制器外部挂了4片DM642,总线为33 MHz,连接示意图如图5所示。IXP425PCI总线主要完成对DM642的启动加载、芯片配置管理、PCI总线仲裁和媒体流调度。DM642芯片组主要完成音/视频媒体流的编码、音/视频合成的功能。目前的容量为4路音/视频合成,视频算法为 H.264,语音算法为 AAC、G.723.1等。

图5 PCI连接示意图

其中,DM642A占用IXP425的PCI时隙1,DM642B占用IXP425的PCI时隙2,DM642C占用IXP425的PCI时隙3,DM642D占用IXP425的PCI时隙4,其有差异的对应引脚互连如下:DM642A与IXP425的PCI引脚对应。PCI中断控制信号由CPLD进行会聚后上报给CPU,CPU通过读取CPLD内部的中断寄存器来判断外围PCI设备的中断事件。

2.3.2 音/视频处理模块最小系统设计

EMIFA允许无缝连接多种SDRAM,由于选用的SDRAM大小为64MB,根据DM642EMIFA的接口准则,DM642最小系统如图6所示。

图6 DM642最小系统连接示意图

芯片选择由CE0完成,选用2片16MB大小的SDRAM进行位扩展后,最大寻址空间为32MB,行地址选通为 A[3:10],列地址选通为 A[3:14],块选择(bank select)为 A[15:16],故使用 DM642地址线 A[3:16]。DM642内核工作在50M×12Hz的模式下,EMIF接口工作在25M×5.33Hz,PCI接口工作在33MHz时钟频率下。

2.3.3 Flash设计

IXP425外挂一片Flash,存储BOOT程序。芯片启动后,从大容量Flash中导入IXP425所需映像到内存中。DSP的程序不单独配置Flash存储器,IXP425通过PCI总线把DSP的程序导入到各自的RAM中运行。IXP425是PCI总线的主器件,其他DSP芯片为从器件。

IXP425通过PCI总线启动DSP的过程如下:

① DSP的配置引脚设置为PCI BOOT模式(AEA[22:21]=01,[PCI_EN:TOUT0/MAC_EN]=10)

② IXP425通过CPLD释放DM642的复位引脚,DM642进入安装状态;

③ IXP425通过PCI总线配置DM642的PCI寄存器;

④ IXP425设置DM642的存储器和I/O空间;

⑤ IXP425把DM642的BOOT程序导入DM642内部RAM中,起始地址为0;

⑥ IXP425访问DM642的存储器空间,把程序写入DM642的内存中,DM642的页寄存器(DSPP)可以使IXP425能够访问DM642的所有空间;

⑦ IXP425置DM642的HDCR寄存器的DSPINT位为1,把DM642从安装状态释放;

⑧ DM642从地址0处开始运行BOOT程序。

2.3.4 CPLD设计

单板CPLD完成的具体功能如下:单板IC复位控制、中断处理、时钟检测、时钟分频、时钟计时(时钟同步)、片选译码、I/O扩展,单板采用一片CPLD,CPLD资源要求仅能使用到70%,预留日后升级使用和防止布线紧张。

2.4 时钟设计

(1)PCI时钟

33MHz晶振的输出经过一个BUF之后分出8路:一路给CPLD作为检测时钟;一路给IXP425的OSC_IN作为芯片工作时钟;一路给IXP425的EX_CLK引脚,作为Expansion总线时钟;一路给IXP425的PCI,作为PCI的时钟;剩下4路送给PCI时钟驱动器。

(2)以太网及SDRAM时钟

50MHz晶振作为CPLD的主时钟,该时钟经过2分频后送给各路以太网芯片作为各自芯片的主时钟,各个时钟没有同步要求。DM642SDRAM时钟由ICS512倍频获取,而IXP425的SDCLK_OUT驱动能力较强,直接驱动4片SDRAM工作。

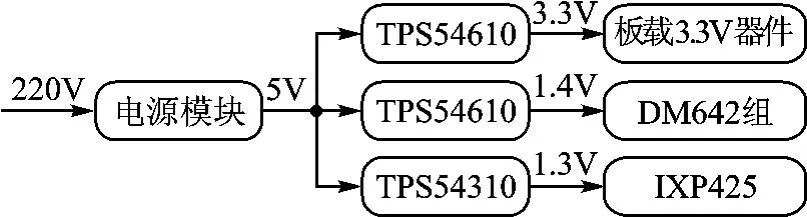

2.5 单板电源设计

电源框图如图7所示。

图7 电源框图

2.6 JTAG链接

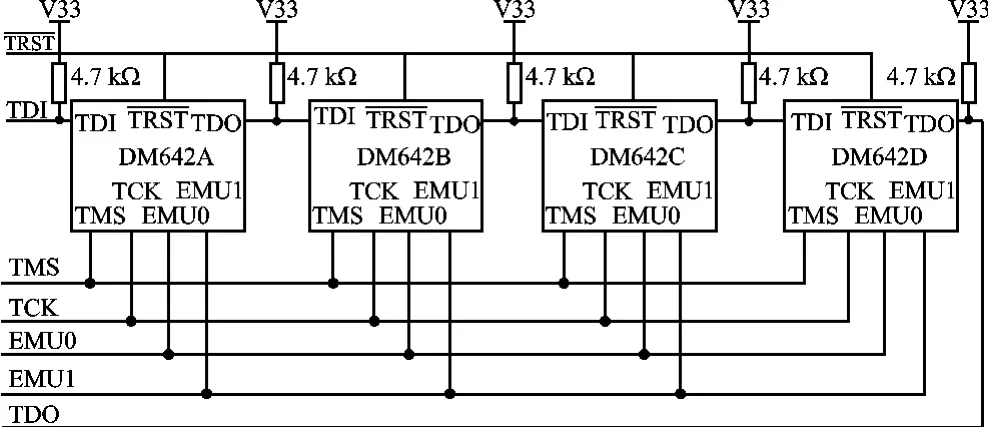

单板CPU、CPLD的JTAG单独成链,方便加载和调试,4片DM642连成一条菊花链,硬件兼容各个芯片单独调试,菊花链框图如图8所示。

图8 DM642菊花链框图

3 硬件调试

本多点控制单元的硬件部分主要进行以下调试:

① 电源、复位模块调试:焊接电源模块芯片及外围电路,测试+5V、3.3V、1.4V、1.3V电压输出是否正常。电压输出正常后,焊接复位电路元件,上电后观察复位电压及延续时间是否满足设计要求,用示波器测量复位信号的电平和持续时间等是否与设计相符。上电后注意各电压转换芯片是否烫手,不正常则立即断开电源进行检查。

② 最小系统调试:在板上焊接IXP425芯片、DM642芯片、CPLD、SDRAM、Flash、JTAG接口及各模块电路外围元件。用放大器仔细检查有无短路、断路、虚焊、漏焊、假焊等情况。无问题后上电,测量各芯片工作电压是否正常,用示波器和频率计测量各模块的工作时钟是否正常。利用JTAG口将硬件与计算机相连,配置好控制寄存器后,测试SDRAM读写功能是否正常,Flash擦写功能是否正常。如果工作不正常,检查时序信号、硬件连接等情况。

③PCI总线调试:测试各功能模块之间数据传送是否正常,如IXP425读写4块DM642,DM642之间读写数据等,需结合计算机、示波器、频谱分析仪、逻辑分析仪等进行测试。

④ 网络收发模块调试:焊接LTX972A及外围器件。检测IXP425的MII接口与LTX972A芯片之间连接是否正常,通过Intel提供的LTX972A测试程序测试网络收发模块是否能与本地PC机通过网口进行数据通信。

4 结 论

本多点控制单元在设计上具有以下特点:

① 非PC机的嵌入式会议电视多点控制单元设计;

② 内部采用PCI总线连接,解决会议电视多点控制单元内部突发大数据量传输和各数据处理模块的同步问题;

③ 多并行数据处理模块设计。

[1] 宋庆恒.基于IXP425和DM642的会议电视终端硬件设计[J].电视技术,2010:34(5):117-120.

[2] 杨建华,黄瑞光.基于TCP/IP协议的桌面视频会议系统中多点控制单元的实现[J].计算机应用,1998:18(12):18-20.

[3] 李彩琴.基于高性能DSP在视频会议多点控制单元(MCU)中的应用[D].西安:西安电子科技大学,2007.

[4] 杨高波,韩龙.视频会议系统综述[J].视频技术应用与工程,2004(9):60-63.

[5] 刘琼,安涛,金刚.基于DM642视频采处理统硬件设计[J].微计算机信息,2007(23):180-182.

[6] 韩非,胡春海,李伟.TMS320C6000系列DSP开发应用技巧[M].北京:中国电力出版社,2008:226-235.