Kinetis微控制器eDMA和I2S的音频接口设计※

李晶皎,荣超群,刁丽芳

(东北大学 信息科学与工程学院,沈阳 110819)

引 言

MK60N512是飞思卡尔公司Kinetis系列微控制器集成度最高的芯片[1-2],它基于 ARM Cortex-M4内核,具有功耗低、性能高、成本低的特点,旨在为嵌入式音频、汽车电子和电源管理等提供灵活的解决方案[3]。MAX5556是美信公司一款低功耗、立体声音频数/模转换器(DAC)[4],支持标准I2S总线协议,采样精度最高可达24位,采样率为2~50kHz。采用Σ-Δ调制技术,能够对量化噪声进行有效整形,减小量化噪声[5]。

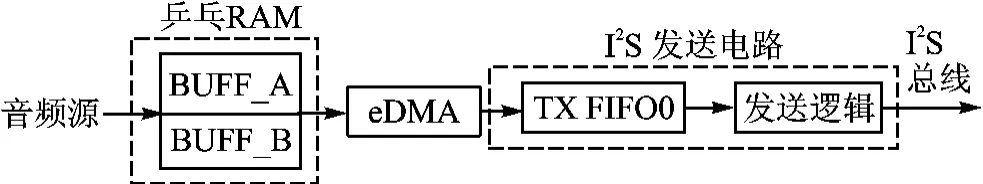

音频处理系统中,采用DMA实现音频数据在微控制器内的传输,能减少内核的参与,降低内核负担[6]。系统的数据传输通道如图1所示,音频信号暂存在缓存区中,由DMA传输到I2S总线模块的发送电路。为了保持音频信号的连续性,采用“乒乓RAM”设计缓存。图中A/B表示乒乓RAM的编号。

图1 数据传输通道

1 MK60N512I2S总线和eDMA介绍

1.1 I 2S总线模块

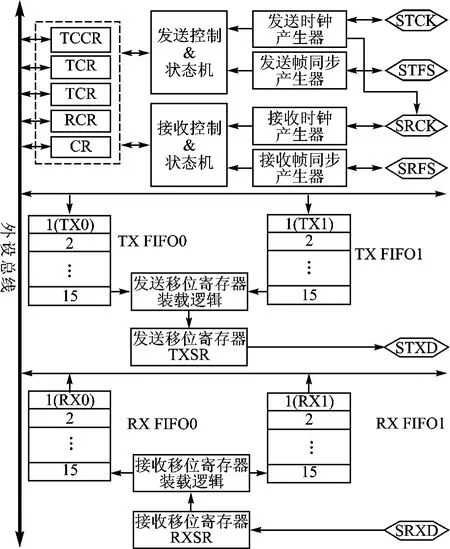

MK60N512的I2S总线模块有3种基本操作模式:普通模式、网络模式和门控时钟模式,针对音频上的应用,I2S总线模块还支持两种衍生模式:I2S总线模式和AC97模式。I2S总线模块的结构如图2所示,由发送电路、接收电路、串行时钟和帧同步时钟产生电路组成。STCK、SRCK分别为串行发送、接收时钟端口,STFS、SRFS为串行发送、接收帧同步端口,STXD、SRXD为串行发送和接收数据端口。在同步模式下,STCK端口被发送和接收单元共同使用。

发送电路和接收电路均有两个FIFO,宽度为32位,深度为15。对发送数据寄存器TX0/TX1和接收数据寄存器RX0/RX1的写入与读取可以访问这些FIFO。发送逻辑将TX FIFO中的数据转移出来,装入发送串行移位器TXSR,然后从STXD端口串行发送;接收逻辑将数据从输入的数据帧中转移出来后,将它们放入接收RX FIFO的入口。当TX FIFO中空缺数目或RX FIFO数据达到设定的数目时,会触发中断或者DMA传输。

图2 MK60N512的I 2S模块结构

1.2 eDMA

MK60N512的eDMA高度可编程,数据传输高度优化而几乎不需要CPU内核干预。与普通的DMA不同,eDMA的传输由主循环(Major Loop)和辅循环(Minor Loop)组成。主循环由外设自动触发,每次主循环结束后源地址、目的地址都会按照TCDn_SOFF、TCDn_DOFF寄存器中的值自动偏移而不需要CPU去修改。除了所有传输结束后产生中断申请外,eDMA还支持“半中断”,即主循环完成总循环次数一半时产生中断申请,这特别适合“乒乓RAM”设计。

2 MAX5556介绍

2.1 引脚定义和内部结构

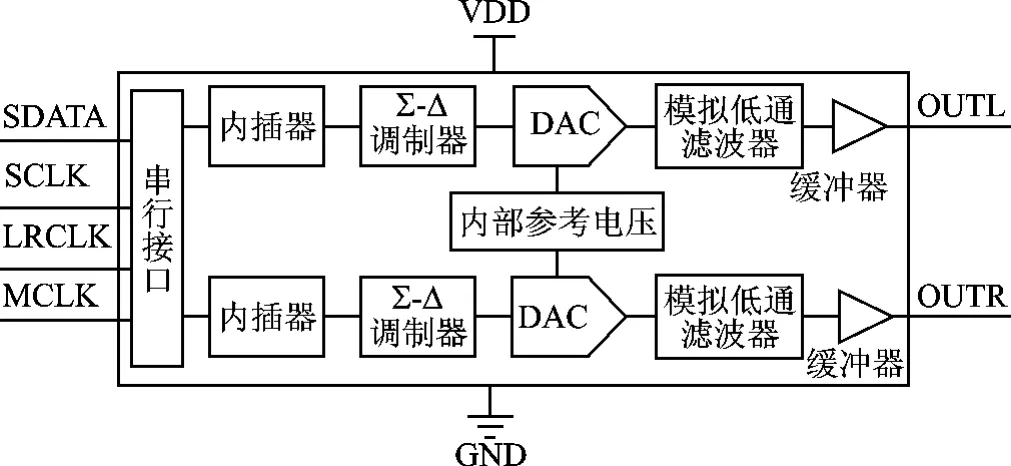

MAX5556内部结构如图3所示,MCLK为主时钟,LRCLK为左/右声道选择时钟,SCLK为外部串行时钟,SDATA为串行音频输入,OUTL/OUTR为左/右声道输出。串行接口模块获取音频数据后,由内置数字插值器、滤波器对其进行滤波,以去除基带音频信号携带的谐波噪声;音频数据经Σ-Δ调制器调制后由DAC转换,输出的模拟信号经由内部的模拟低通滤波器进行滤波,衰减高频量化噪声;内置输出缓存器能驱动大于3kΩ的负载电阻和高达100pF的负载电容;最终模拟音频信号从OUTL/OUTR输出。

图3 MAX5556内部结构

2.2 工作模式

MAX5556支持外部串行时钟模式和内部串行时钟模式。在一个LRCLK周期内,若检测到有效的SCLK,则进入外部串行时钟模式,SCLK作为采样时钟;如果检测不到有效的SCLK,则进入内部串行时钟模式,采样时钟由内部生成。内部采样时钟的频率根据检测到的MCLK与LRCLK的比值确定,若MCLK与LRCLK的比值为384,则内部采样时钟频率为48×fLRCLK;若MCLK与LRCLK的比值为256或512,则内部采样时钟频率为

2.3 数据格式

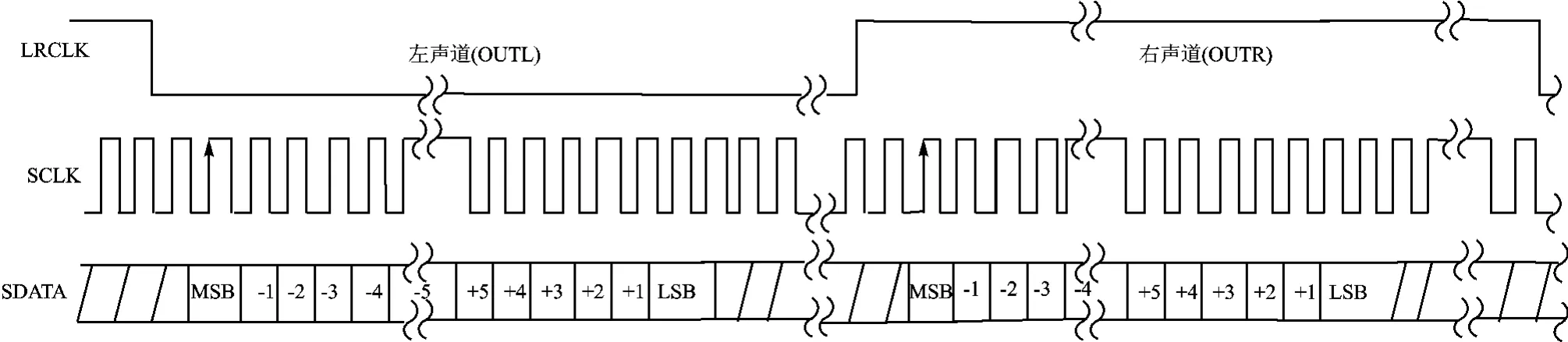

MAX5556支持左对齐16位或者24位数据格式。当其工作在外部串行时钟模式,或工作在内部串行时钟模式,且同时MCLK与LRCLK的比值为384时,有效数据为24位。如果数据不足24位,低位补零;超过24位的数据会被忽略。当工作在内部串行时钟模式,且MCLK与LRCLK的比值为256或512时,有效数据为16位。MAX5556数据格式如图4所示。每次LRCLK沿变化后的第二个SCLK上升沿时,SDATA上数据开始有效,出现最高有效位(MSB);24个或者16个时钟周期后出现最低位有效位(LSB)。LRCLK为0时,数据进入左声道DAC;LRCLK为1时,数据进入右声道DAC。

3 系统硬件电路设计

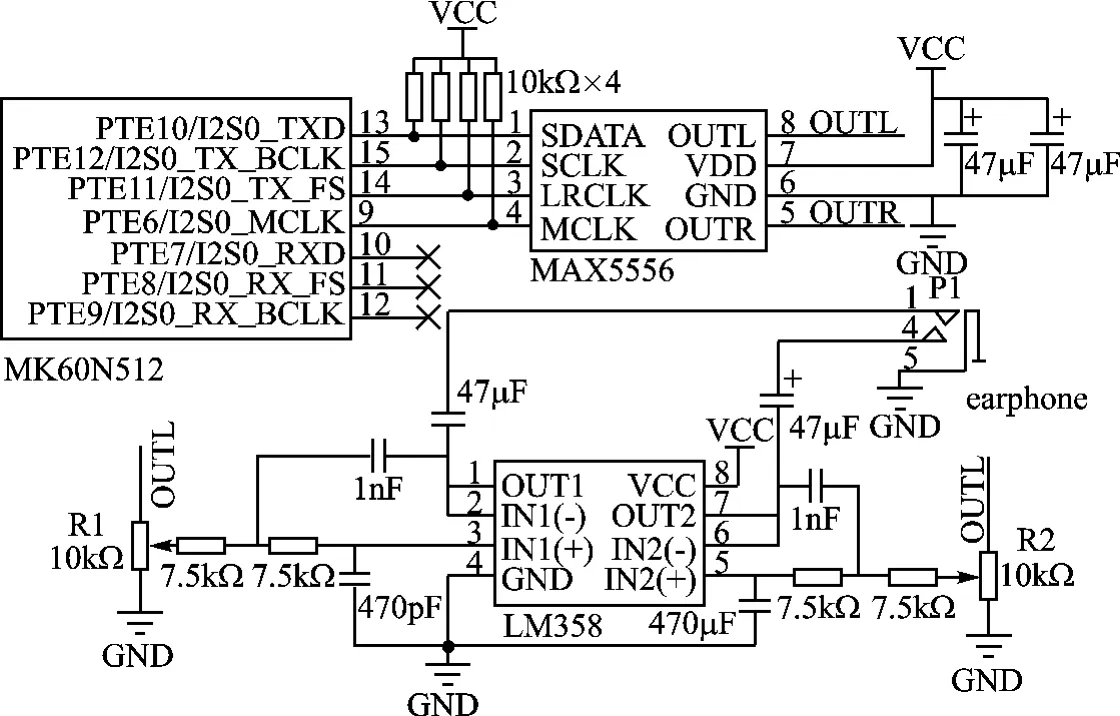

MK60N512通过I2S总线将音频数据传输给MAX5556进行数模转换,输出模拟音频信号由滤波电路进行滤波,同时提高带负载能力。I2S总线模块工作在I2S总线主模式下,发送电路的STCK、STFS和STXD端口对应的引脚分别为BCLK、TX_FS和TXD,I2S总线模块的主时钟通过MCLK引脚输出。硬件电路如图5所示。由于MK60N512工作在3.3V电压下,而MAX5556工作电压为5V,为了提高数据传输的稳定性,接口均采用上拉方式。

图4 MAX5556数据格式

图5 硬件电路

LM358在5V单电源供电时有效输出为1.5~3.5V,而MAX5556的输出可以达到0~5V,因而在输入端使用R1和R2对原始信号进行衰减,防止输出信号出现削顶失真。

4 软件设计

4.1 “乒乓RAM”设计

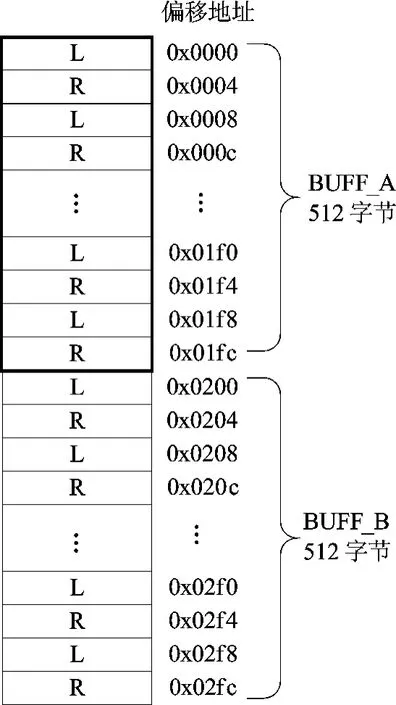

MK60N512的I2S总线模块在I2S总线模式下支持双声道,音频数据在FIFO中交错存放,因此在缓存中的音频数据也需要交错存放。数据缓存如图6所示,其中L/R表示音频左/右声道。每个音频数据占用4个字节空间,缓存BUFF_A、BUFF_B在物理地址上是连续的,它们大小均为512字节,共存储256个音频数据。当DMA从缓区BUFF_A中读取数据时,CPU向缓存区BUFF_B中存储下一组音频信号;当DMA将BUFF_A中的数据全部传输结束后,将DMA通道源地址切换到BUFF_B,同时CPU向BUFF_A存储数据,如此反复。

4.2 I 2S总线模块的配置

图6 数据缓存

配置I2S总线模块工作在I2S总线主模式下,默认一帧数据长度是32位,而且为左对齐模式;使用帧同步TX_FS作为声道选择时钟,且同步帧长度为一个字。由于MAX5556的SCLK信号由MK60N512提供,MAX5556工作在外部串行时钟模式,有效数据位是24位,因而配置发送数据位为24位。按照MAX5556的数据格式,数据需要在SCLK下降沿输出从TXD数据,且需要发送早期帧同步,让数据延迟一个采样时钟,还需要根据音频采样频率设置帧频率。

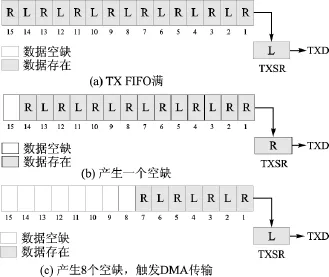

使能TX FIFO和其DMA请求,当FIFO中空缺数达到8时,启动一次DMA主循环。图7为音频数据在TX FIFO移动过程。图7(a)中FIFO为满,随着发送移位逻辑从FIFO从取出一个数据后,FIFO产生一个空缺,如图7(b)所示。当发送8次数据后,FIFO空缺数达到8个,则触发DMA主传输,如图7(c)所示。

I2S总线的初始化代码略——编者注。

4.3 eDMA配置

当TX FIFO空缺数达到8时,触发DMA主循环,故每次主循环传输数据数目是32字节,每次主循环源地址偏移也是32字节,完成缓存区1 024字节数据传输需要32次主循环。第16次主循环结束,DMA已经将BUFF_A中所有数据传输完毕,DMA源地址指向BUFF_B,并产生“半中断”请求,CPU开始向BUFF_A中存储下一组512字节音频数据。

图7 FIFO中的数据和空缺

当BUFF_B中数据传输结束后,源地址恢复到BUFF_A起始地址,并产生中断请求,CPU响应中断并向BUFF_B中存储下一组512字节音频数据。可以看出,在传输过程中,CPU只需要响应两次中断请求,然后向缓存区写入音频数据。每次主循环结束后源地址偏移32字节,完整的传输结束后,源地址恢复到BUFF_A起始地址,这些操作都是通过eDMA模块自己完成的。

DMA的初始化代码略——编者注。

5 测试结果

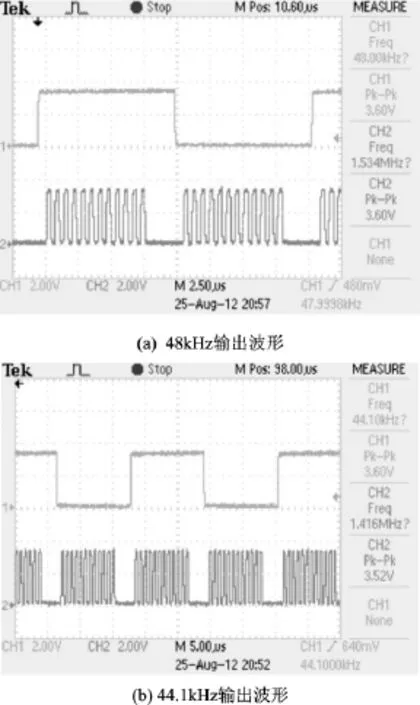

图8为TX_FS和TXD的波形图,通道1为TX_FS,通道2为TXD。左/右声道发送的音频数据均是0x555。图8(a)的发送帧频率为48kHz,图8(b)的为44.1kHz。从图8中可以看出,数据长度为24位,左对齐模式,而且数据与帧同步有一个采样时钟的延时,符合MAX5556的数据格式和时序。

结 语

本文设计了基于Kinetis MK60N512和MAX5556的立体声音频接口,MK60N512将音频数据按照MAX5556的数据格式和时序通过I2S总线传输给MAX5556,MAX5556内部DAC将数据转化为模拟信号输出,并由滤波电路对音频信号进行滤波,同时提高带负载能力。使用MK60N512内部高性能可配置的eDMA提高系统数据传输速率,降低CPU的负担。测试表明,系统能输出立体声音频,输出频率可调,可以为Kinetis系列微控制器音频解决方案提供参考。

图8 I 2S总线输出波形

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1] 刘贯营,赵玉荣.Cortex-M4内核微处理器DMA方式的高速 A/D采样[J].单片机与嵌入式系统应用,2012(7):71-72.

[2] Freescale.K60Sub-Family Reference Manual[EB/OL].[2012-09].http://www.freescale.com.

[3] 丁燕.基于Freescale Kinetis的农田灌溉控制板卡的设计[J].电子技术,2011(2):5-8.

[4] Maxim.MAX5556:Low-Cost Stereo Audio DAC[EB/OL].[2012-09].http://www .maxim-ic.com.

[5] 刘素娟,张特,陈建新.新型双声道音频Σ-ΔDAC小面积插值滤波器的设计实现[J].电子与信息学报,2011,33(3):749-753.

[6] 邵富杰,张国利,周勇.基于I2S总线实现嵌入式语音采集与回放[J].微计算机信息,2011,27(6):72-74.