嵌入式AES加密存储器的硬件实现

冯 妮,张会新,卢一男,刘文怡

(中北大学a.仪器科学与动态测试教育部重点实验室;b.电子测试技术重点实验室,山西太原 030051)

嵌入式AES加密存储器的硬件实现

冯 妮,张会新,卢一男,刘文怡

(中北大学a.仪器科学与动态测试教育部重点实验室;b.电子测试技术重点实验室,山西太原 030051)

介绍了一种基于FPGA的AES硬件加密系统,该系统实现了电子数据的加密及存储。详细说明了AES加密算法的FPGA架构,AES核心算法的接口时序设计,AES加密存储器的硬件设计以及算法验证。硬件加密较之软件加密有实时性高、数据量大以及性能好的特点。FPGA开发周期短的特点与AES灵敏性好、实现效率高、安全性能高的优势相辅相成,为需要保密的电子数据提供更加可靠的保证。

AES;FPGA;数据加密;加密存储器

随着人们对信息安全的要求越来越高,电子数据加密技术也逐步登上历史舞台。因为AES加密算法具有灵活性高、容易实现、对称加密的特点,已被广泛应用于各行各业。其算法块的大小可变为128,192,256位,密钥位宽有128,192,256 三种且对应的加解密轮数为 10,12,14轮[1-2]。基于软件加密算法有生成时间长、执行速度慢的缺点,硬件加密算法的可塑性则受到了人们的广泛关注。它具有高速性、灵活性和易维护性的特点,同时用硬件实现加密,即可将加密生成过程封装于芯片中,很难被盗者篡取,安全性更高。

1 系统构成

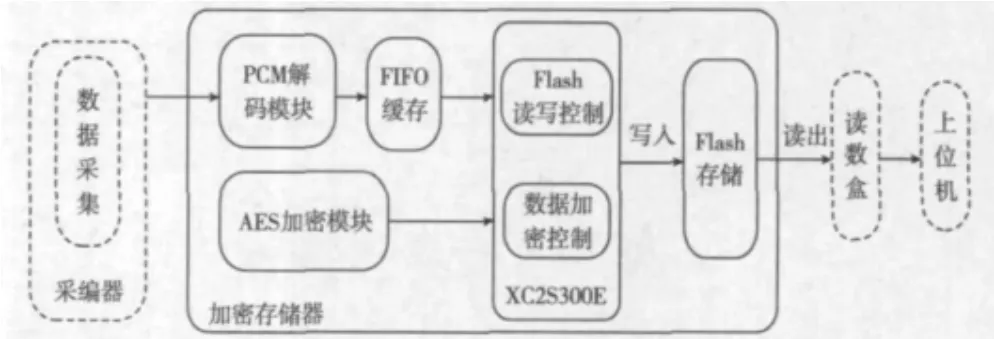

本系统以Spantan-2系列的XC2S300E为中控逻辑单元,主要完成数据的硬件加密及Flash存储。存储器接收到采编器采集的数字量,进行解码后缓存入FIFO,对FIFO中的数据进行AES加密,由FPGA控制加密数据的读与写,最后通过上位机将Flash中的加密数据进行分析和处理,得到的数据就是前端设备传输的实测数据。主要的参数如下:1)AES加密算法的数据吞吐率为90 Mbit/s;

2)明文输入和密文输出接口为128位,密钥长度为128位;

3)密钥注入方式为编程器烧制。系统框图如图1所示。

图1 系统结构图

2 系统设计

2.1 AES加密的FPGA架构

AES加密的内部架构主要包含五大模块,如图2所示。当FPGA检测到开始加密的指令后,初始化序列模块将输入的128位明文按照矩阵排列,同时初始密钥根据子密钥生产模型进行10轮变换,从而快速产生10轮子密钥。初始化后的128位明文和子密钥经过10轮迭代后得到密文[3-4]。结束序列模块主要负责将轮变换后的密文进行反矩阵排列,排列后的128位密文则传送到输出端口。当FPGA收到结束加密的指令时,即完成加密过程,与此同时将128位密文数据存入Flash进行长期存储。

图2 FPGA内部结构图

2.2 接口时序设计

数据的准确采集和完整接收是存储器进行存储的前提[5]。本设计在12个clk内实现了128位明文的数据加密。当第1个clk来临时,load信号被拉高,在总线上会采样到128位明文,同时初始密钥会被装载到密钥扩展模块中。通过加密系列运算,10个clk内完成了10轮加密循环。在第12个clk内,输出总线上会采集到128位密文。FPGA控制done信号被拉高,此时128位密文被送到输出端口。具体时序图如图3所示。

图3 AES加密的接口时序图

2.3 嵌入式加密存储器硬件设计

嵌入式加密存储器就是将AES加密过程封装于存储器的主控芯片中,实现数据流的加密与存储功能,既增强了系统的可靠性,也保证了电子数据的安全性。采用Spantan-2系列的XC2S300E作为本设计的主控芯片,是因为它的门阵列数最高可达300 000个,可利用的最多的I/O口有329个,CLB总共有1 536个,BLOCK RAM BITS为64 kbit,可配置逻辑块丰富以及芯片时钟远远大于工作时钟等都已经为数据加密存储器增加了很高的可靠性[6-8]。

在硬件设计中,FPGA时钟频率选用60 MHz,12个clk内完成128位明文的一次加密过程。在ISE中生成的FPGA原理图如图4所示。首先,存储器将接收到的pcm数字量进行解码处理,解码后的数据缓存入内部FIFO进行速度匹配。data8to128主要是将USBFIFO内的8位数字量匹配为128位的明文,然后AES模块对明文进行加密处理。最后,将加密完的128位密文写入外部FIFO,此模块采用IDT7207作为缓存芯片来匹配速度。

3 系统验证

图4 FPGA原理图

本系统采用硬件描述语言(VHDL)进行程序编写,使用(chipscope)硬件在线仿真软件对嵌入式AES加密系统进行实验验证[8]。AES加密在FPGA中实现的验证步骤如下:1)先对AES加密模块中各子模块进行验证;2)再对AES加密模块进行整体算法验证。工程项目中会使用不同组的明文和密钥来验证结论的正确性。本设计针对一组明文和密钥进行仿真,经过验证可得出密文是正确的。图5是对整体算法进行验证,其中,明文为128位,共16 byte,经过10轮子循环得到128位密文。

由图5可知:明文为32 43 F6 A8 88 5A 30 8D 31 31 98 A2 E0 37 07 34;密文为39 25 84 1D 02 DC 09 FB DC 11 85 97 19 6A 0B 32。

4 结束语

本设计是在研究AES加密算法的基础上实现了电子数据的加密与存储。与一般的固态存储器相比,加密存储器先将前端设备传来的数据进行加密处理,再送进Flash进行存储,数据的安全性和系统的可靠性已经在工程项目中得到体现。AES加密领域可优化的地方还有很多,比如密钥长度可扩展到192位或256位,那么基于AES-192或AES-256的加密存储器也有待应用于各行各业中。

图5 AES算法的chipscope验证(截图)

:

[1]李全民,张运楚.一种用数字技术加密模拟电视信号的方法[J].电视技术,2000,24(9):47-48.

[2]DAEMEN J,RIJMEN V.高级加密标准(AES)算法——Rijndael的设计[M].谷大武,译.北京:清华大学出版社,2003.

[3]李玮.若干分组密码算法的故障攻击研究[D].上海:上海交通大学,2009.

[4]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002.

[5]平亮,孙军,周军.一种基于JPEG标准的数字图像加密算法[J].电视技术,2006,30(7):87-90.

[6]路伟.基于FPGA的AES加密算法在网络认证中的应用[D].哈尔滨:哈尔滨工程大学,2006.

[7]钟名富.分组密码SMS4安全性分析[D].西安:西安电子科技大学,2008.

[8]张金辉,郭晓彪,符鑫.AES加密算法分析及其在信息安全中的应用[J].信息网络安全,2011(5):31-33.

张会新(1980— ),博士,主研动态测试技术及智能仪表等;

卢一男(1988— ),硕士生,主研电路与系统;

刘文怡(1970— ),博士生导师。

Implementation of Embedded AES Encryption Algorithm in Hardware

FENG Ni,ZHANG Huixin,LU Yinan,LIU Wenyi

(a.Key Laboratory of Instrumentation Science&Dynamic Measurement;b.Science and Technology on Electronic Test&Measurement Laboratory,North University of China,Taiyuan 030051,China)

An AES hardware encryption system which achieves the target data encryption based on FPGA is introduced in this paper.The overall structure of AES encryption algorithm,the interface timing design of the core algorithm,hardware design of AES encryption memory and algorithm verification are described in detail.Hardware encryption,than software encryption,has the characteristics of real-time,large volumes of data and good performance.FPGA has a short development cycle,and AES has some advantages of good sensitivity,high efficiency and high safety performance.They complementary provide a more reliable guarantee for the confidential and electronic data.

AES;FPGA;data encryption;encryption memory

TN91

A

【本文献信息】冯妮,张会新,卢一男,等.嵌入式AES加密存储器的硬件实现[J].电视技术,2013,37(3).

国家自然科学基金项目(61004127)

冯 妮(1987— ),女,硕士生,主研总线技术及自动检测仪器;

责任编辑:魏雨博

2012-07-25