逻辑综合在数字IC设计中的应用

赵庆哲,王兆勇

(中国电子科技集团公司第四十七研究所,沈阳 110032)

1 逻辑综合概述

什么是逻辑综合?逻辑综合是指应用相关工具软件读入IC设计者所设计的RTL(Register_Transition_Level)的Verilog HDL或者VHDL源代码,以一定的半导体工艺库为目标,在时序或面积约束下,将RTL源代码映射成为门级网表的过程。逻辑综合将IC设计者的设计意图转化成为了实际的电路连接形式,它是IC设计流程中联系前端和后端的桥梁,后续对设计的处理都是以逻辑综合后生成的门级网表为基础进行的。

2 逻辑综合的方法

2.1 逻辑综合流程

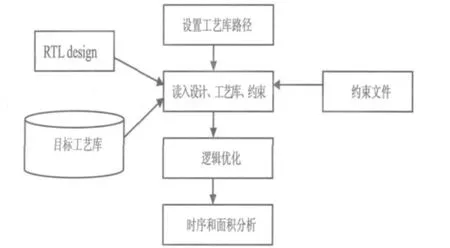

逻辑综合的流程主要分为四个部分:首先,建立逻辑综合环境,包括半导体工艺库的路径设置以及对工艺库中一些特殊元器件使用的设置;其次,读入设计和目标工艺库以及约束文件;第三,对设计进行逻辑上的优化;第四,对优化后的设计进行时序分析,如果没有达到约束目标,那么就需要修改设计并重复上述过程。图1表示的就是综合流程。

图1 逻辑综合流程

2.2 逻辑综合的方法

结合逻辑综合流程图,我们详细阐述逻辑综合的方法。

目标工艺库路径的设置:由于逻辑综合以一定的半导体工艺库为目标,因此,我们首先要设置工艺库的路径,便于综合工具对其进行寻找。半导体工艺厂商提供的.db形式的工艺库文件可以作为目标工艺库文件。对于目标工艺库的路径设置方式,不同的软件工具有不同的形式,但大致上都是设置目标工艺库的路径和目标工艺库文件。目标工艺库是工艺库中最差情况的工艺库。同时,还需要设置最好和最坏两个极端情况的工艺库及其路径,之所以这样设置,是为了在时序分析的时候能更好地分析setup timing和hold timing。最后需要设置链接库。在一些设计中往往存在一些宏单元,例如存储器单元和I/O单元,它们不属于标准单元库中的单元,因此,需要将其设置为链接库,在逻辑综合的时候会在需要时调用这些宏单元。注意,这些宏单元文件必须作为链接库来进行设置,如果作为目标库进行设置,则在逻辑综合过程中软件会将宏单元作为目标库来使用。

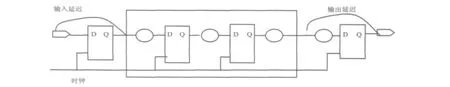

读入设计、工艺库和约束:这是逻辑综合读取RTL设计和工艺库以及约束的过程。对于RTL设计,综合工具可以接受VerilogHDL和VHDL形式的文件,但是RTL设计应该是可综合的结构,否则在读取过程中会产生一些警告或者错误信息,导致综合结果出现偏差。对于工艺库,在其路径设置完成后,逻辑综合工具会自动将其读入到软件的内存之中以待使用。约束文件是逻辑综合过程中重要的文件,它是IC设计者期待的IC所能达到的时序或面积上的目标。是整个逻辑综合过程中逻辑优化的指导方向。基本的约束包括对时钟的约束和对输入输出端口的约束。对时钟的约束主要是设置时钟名称、端口以及周期等信息;对于输入端口的设置,主要是输入信号相对于时钟的延迟时间;而对于输出端口的设置则是对下游电路的延迟时间进行设置。图2就是时钟以及输入输出延迟示意图。

图2 输入输出延迟示意图

读入逻辑综合所需的文件后,综合工具便开始了逻辑优化过程,这个过程基于上述的约束目标。在逻辑优化过程中,对设计进行处理有两种方式,一种是保留设计层次,另一种是将设计全部展平,也就是打破设计的全部层次。由于逻辑综合一般不进行跨越模块边界优化,因此对于时序要求很严格的设计来说,打破层次的综合方式比较适合,而对于时序要求不严格的设计而言,则两者都在可选之列。

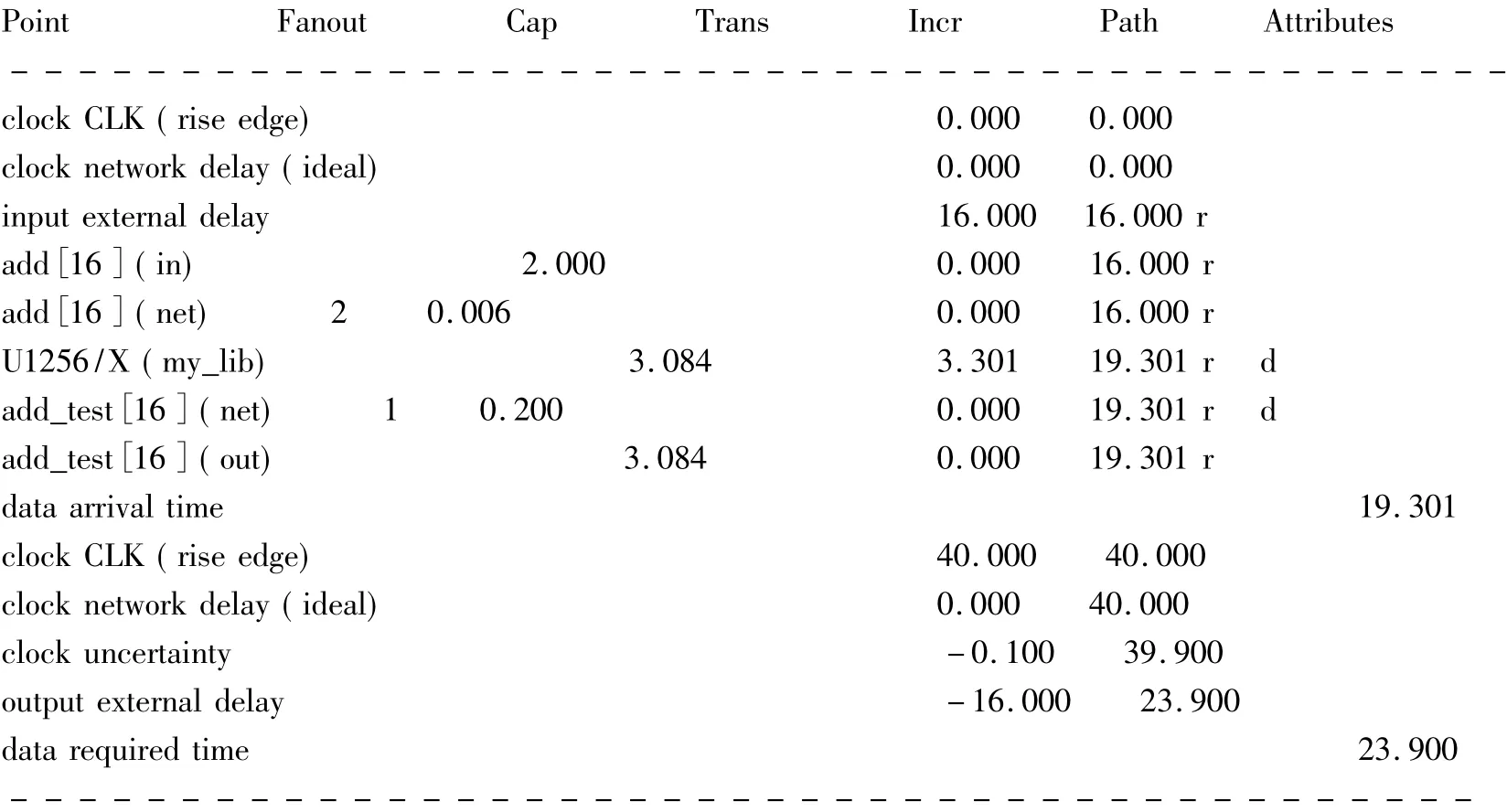

时序和面积分析:逻辑综合工具内嵌有静态时序分析工具,因此在逻辑综合完成后,可以对设计进行时序和面积分析。分析的目标有两个,即setup timing和hold timing分析。前者是对设计中寄存器的数据信号先于时钟信号稳定的时间进行检查,如果出现违背,则说明寄存器不能正确地采集到输入信号。而后者是寄存器的数据信号晚于时钟信号稳定的时间,如果出现违背,则说明上下两级寄存器之间的数据变化太快以致后级寄存器无法正确采集到前级寄存器的数据。时序分析清晰地表示出了路径的时序状况,下面就是某设计的时序分析报告。

从这个报告中我们可以看到时序路径的起点和终点以及分析的类型、所属的时钟域以及路径上的时序变化情况。

2.3 生成文件

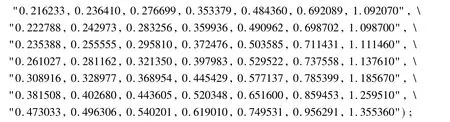

逻辑综合完成后,生成的文件有门级网表文件和.sdf、.sdc文件。门级网表是映射到目标工艺库的设计,是一种门级连接。它是后续流程的基础。.sdc文件是逻辑综合工具生成的关于设计的约束文件,它是逻辑综合所用的约束文件的生成物,提供给后端P&R用作时序约束。.sdf文件是设计中各个单元的延迟文件,它是根据标准单元库中单元的时序数据计算而来的。单元在不同的load和transition time条件下的延迟是不同的,在标准单元库中,存在一个二维的查找表,表的纵向和横向分别是transition time和load,以下是某标准单元库中的时序二维表。

逻辑综合过程中,软件根据单元实际的transition和load进行查表,如果超出了表的范围,那么计算的延迟值便不是一个准确值。如果在表内,为了准确计算单元延迟,找出与实际延迟值相邻的四点,根据四点差值算法,计算单元的延迟并写入.SDF文件之中。

3 结 束 语

以上就是逻辑综合的基本过程,完成上述各步骤,就完成了一个设计的逻辑综合过程。逻辑综合是一种自动化的设计方式,主要依据一定的算法对设计进行处理,因此,缺乏灵活性。因此要求设计者对电路要加深理解,对硬件描述语言与逻辑综合的关系要清楚地把握,只有这样,逻辑综合工具才能综合出理想的电路结构。同时,逻辑综合人员也要对标准单元库有所了解,对内部元器件的特性要熟悉,这样,才能给出适当的设计约束,从而更好地完成逻辑综合工作。

[1]Himanshu Bhatnagar,著.高级 ASIC 芯片综合[M].张文俊,译.北京:清华大学出版社,2007.

[2]Weste,Harris,著.CMOS超大规模集成电路设计[M].汪东,李振涛,李宝锋,等译.北京:中国电力出版社,2005.