应用于USB全速设备中的锁相环设计

蒋 旭,沈海斌

(浙江大学 电气工程学院,浙江 杭州310027)

0 引 言

锁相环 (phase locked logic,PLL)能够跟踪输入信号的相位和频率,并输出相位锁定、低抖动的其它频率信号,已经在数字信号处理、无线电通讯、自动化控制等领域得到了广泛的应用。近年来,锁相环技术也越来越多的被用于通用串行总线(universal serial bus,USB)设备中的数据同步和采样[1]。

通用串行总线是一种具有传输速度高的总线接口,支持的传输速率有1.5Mbit/s (低速),12Mbit/s (全速)和480Mbit/s(高速)[2]。主要有以下3种方法为 USB设备提供时钟:①在USB芯片中设计基于采样计数的时钟恢复单元,该方法的缺点是采样时钟频率较高,导致功耗较大;②在USB芯片中设计所需时钟频率的振荡器,该方法的不足是受工艺的影响较大和精度较低,即使同一流片批次的芯片振荡频率也有较大偏差;③在USB芯片中内嵌一个用于倍频的锁相环,外接低频的晶振作为芯片的输入,该方法的不足是外接晶振导致成本偏高。

由于现有方法的不足之处,本文提出了一种应用于USB全速设备中的锁相环设计方法。该锁相环利用USB总线上传输的数据恢复出可用于USB全速设备的48MHz本地时钟,以及产生3MHz、6MHz、12MHz、24M、96M时钟以供全速设备使用,有效的避免了现有方法的不足之处。

1 USB全速设备中锁相环的基本原理

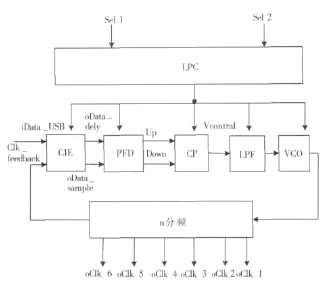

传统的电荷泵锁相环一般由5个模块组成[3-4]:鉴频鉴相 器 (phase frequency detector,PFD)、电 荷 泵 (charge pump,CP)、低通滤波器 (low pass filter,LPF)、压控振荡器 (voltage control oscillator,VCO)、分频器 (frequency divider)。为了应用于USB全速设备中的数据传输和采样,本文在传统的电荷泵锁相环基础上,增加了时钟信息提取单元(clock information extraction,CIE)和低功耗控制模块 (low power control)。锁相环的原理结构如图1所示。

图1 USB全速设备中锁相环的原理结构

iData_USB为USB设备传输的数据,时钟信息提取模块根据振荡器产生的时钟把传输数据中的时钟信息提取出来传递给鉴频鉴相器;鉴频鉴相器将时钟信息转化为控制电荷泵充放电的控制电压 (Up/Down);电荷泵单元根据Up/Down电压进行充放电,从而调节振荡器的压控电压;该压控电压经过低通滤波器后控制振荡器的振荡频率,使得振荡频率 (相位)朝着iData_USB的频率 (相位)变化,形成反馈环路。当振荡频率和输入数据的传输速率保持一致时,锁相环电路进入锁定状态。

2 USB全速设备中锁相环的设计实现

下面将分别介绍USB全速设备中锁相环中各个部分的工作原理和实现方法。

2.1 时钟信息提取单元 (CIE)

根据USB协议中规定USB全速设备数据传输速度为12Mbit/s,总线上传输的数据信号经过NRZI编码[5],再以差分的形式在D+和D-数据线上传输,而时钟信息则包含在数据信号中,所以我们需要从12Mbit/s的数据信号中提取所需的时钟信息。时钟信息提取单元的作用就是从传输的数据信号中将时钟信息提取出来,供后面各个模块使用。

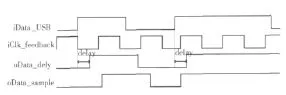

时钟信息提取单元由一个采样电路和一个延时单元组成。USB总线上的数据信号为iData_USB,采样电路对该数据信号采样,输出oData_sample。采样电路由一个边沿触发器构成,采样的时钟来自锁相环中分频器分频后的时钟信号Clk_feeedback。同时,数据信号iData_USB经过一个延时单元,输出信号oData_dely。oData_sample和oData_dely这两个信号将传递给鉴频鉴相器用来比较频率(相位)差。时钟信息提取单元的波形图如图2所示。

图2 时钟信息提取单元的波形

从图2中可以看出,当Clk_feedback时钟频率 (相位)和数据信号iData_USB信号匹配时,oData_dely和oData_sample两个输出信号波形将保持一致;当两个输入信号不匹配时,两个输出信号将在频率 (相位)上产生差别,进而传递给鉴频鉴相器做比较,完成时钟信息提取的功能。

2.2 鉴频鉴相器 (PFD)

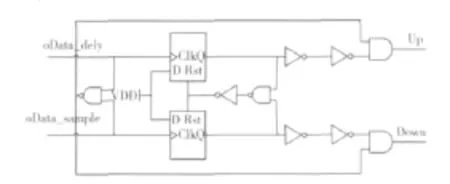

鉴频鉴相器在环路中的作用是检测采样信号oData_sample和USB数据延迟信号oData_dely之间的频率相位差,产生一组与频率相位差成线性比例关系的电压信号,从而实现相位—电压的变化。

常用的鉴相器结构有异或门鉴相器,RS锁存器鉴相器,三态鉴频鉴相器[6]。本文采用三态鉴相器结构来实现鉴频鉴相功能,电路结构如图3所示。三态鉴相器具有鉴频鉴相功能,捕获范围大,捕获时间短,电路结构简单等特点。

图3 鉴频鉴相器电路结构

本文采用的鉴频鉴相器电路比基本的三态鉴频鉴相器[7]多了两个与门和一个与非门,这3个器件组成了鉴频鉴相器的输出电压使能控制。理想状态下当oData_dely和oData_sample两个信号同时为高电平的时候,D触发器复位,电路的两个输出信号Up/Down为低电平。由于实际电路中存在着延时,D触发器经过短暂的时间后才复位,这导致基本的三态鉴频鉴相器的Up/Down两个输出信号在这段时间内会同时为高电平,从而导致电荷泵模块充放电电路同时工作,增加了输出时钟抖动和电路功耗,对于充放电电路的电流匹配要求也更加苛刻。鉴于基本的三态鉴频鉴相器存在着上面的问题,本文采用图3中的鉴频鉴相电路结构,当两输入信号同时为1的情况下,输出电压使能控制端被置“0”,输出被屏蔽,不会存在Up/Down同时为高电平的情况,降低了电路功耗,提高了输出时钟的稳定性。

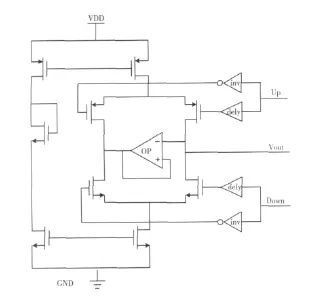

2.3 电荷泵 (CP)

电荷泵电路根据输入的Up/Down信号进行充放电,调节存储在电容上的压控电压。为了确保锁相环电路的锁定频率 (相位)误差较小,要求电荷泵电路的充放电电流需要尽量一致。本文采用的电荷泵电路抑制了电流不匹配、电荷注入和电荷共享效应[6,8],电荷泵的充放电电流为12.39uA,电路结构如图4所示。

图4 电荷泵电路结构

2.4 低通滤波器 (LPF)

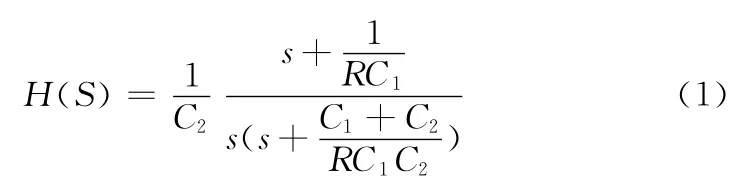

为了抑制压控电压的跳动,本文中低通滤波器采用了常用的RC二阶滤波电路,电阻R和电容C1串联后,再与C2并联组成低通滤波器。电容取值一般C2<<C1[3,9],可近似为一阶滤波器,闭环的时间和频率响应就相对保持不变。本文中C2电容值是C1电容值的1/6。该电路的传递函数可以表示为

2.5 压控振荡器 (VCO)

压控振荡器的功能就是根据压控电压,产生对应频率的振荡信号。电流控制振荡电路的输出频率范围比较宽,差分振荡电路在抑制电源噪声方面效果比较好[7]。本文采用了差分振荡电路结构的压控振荡器,主要包括偏置电路,振荡电路,正弦波转方波电路,结构如图5所示。

图5 压控振荡器电路结构

Vcontrol为滤波电路产生的压控电压,振荡电路采用四级差分延迟单元级联的形式,根据压控电压输出对应频率的振荡信号。差分延迟单元的具体结构如图6所示。

图6 差分延迟单元电路结构

控制信号Ve控制差分延迟单元的尾电流的大小,控制信号Vb调节M1和M2两个MOS管的电阻阻值,Ve和Vb共同调节差分延迟单元的延迟时间。当电路的振荡频率增大时,Vout电压上升,Vout>Vb-Vth的时候,M1和M2将进入饱和区,此时MOS电阻阻值变大,导致振荡频率下降。因此,我们需要在Vout>Vb-Vth的时候对电路进行调整。本设计中进行了电阻补偿来实现。在两个电容外各并联了一个栅漏相连的MOS管,这两个MOS管起到了电压钳位的作用。当Vout<Vthn时,这两个MOS管不工作;当Vout>Vthn时这两个管导通,相当于在原先的RC并联基础上额外并联了一个电阻R,进行了电阻补偿。

2.6 分频器 (FD)

压控振荡器的输出信号是96MHz时钟,而时钟信息提取单元所需要的iClk_feedback是12MHz时钟,因此需要分频器对压控振荡器的输出信号进行分频。经过分频器后产生了48MHz,24MHz,12MHz,6MHz,3MHz的时钟信号以供USB全速设备中其他电路使用。

2.7 低功耗控制模块 (LPC)

锁相环电路中压控振荡器不间断振荡以及电荷泵不断的充放电都会造成比较大的功耗,为了尽可能的降低功耗,本文增加了低功耗控制模块。低功耗控制模块有两个模式,均为高电平有效,电路结构如图7所示。

模式一:选择信号为Sel1,将用6MHz本地时钟来控制时钟信号提取单元、鉴频鉴相器、电荷泵3个模块间歇工作,节省部分功耗,压控振荡器和分频器正常工作。锁相环电路在该模式下还会输出有效的时钟信号。该模式的优点在于当电路对时钟信号的要求不是太高时,可以牺牲时钟信号的稳定性来降低锁相环电路的功耗。

图7 低功耗控制模块电路结构

模式二:选择信号为Sel2,除了关断钟信号提取单元、鉴频鉴相器、电荷泵外,该模式还将关断压控振荡器和分频器。但为了锁相环电路重新上电时能快速锁定信号,模式二下会保存压控电压的值。加入延时和一个与门的目的是为了确保电荷泵比压控振荡器先断电,这样才能防止在掉电过程中对压控电压造成比较大的影响。反之,在上电的过程中压控振荡器要比电荷泵先上电。

2.8 版图实现

根据上述各个模块的电路结构,在Virtuso中完成了锁相环版图,如图8所示。整个锁相环的面积约为274.8μm*332.9μm。

图8 锁相环版

3 实验与性能分析

基于5V电压的0.35μm标准工艺,对本文中的电路结构进行了测试。

压控振荡器可调节的范围为52.68MHz136.78MHz,当输出信号频率为96MHz时,相位噪声为-102.5dBc/Hz@1MHz;为了满足USB协议中规定的时钟抖动要求,压控振荡器的输出频率应该稳定在90MHz到102MHz之间,即对应的压控电压范围为2.73V3.02V。

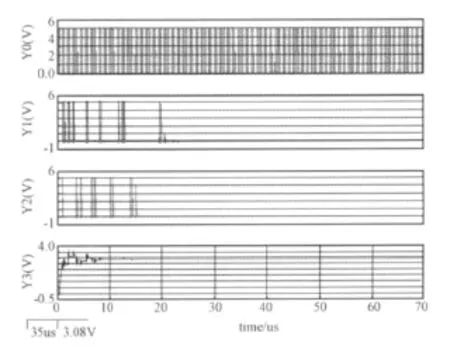

当以6MHz的时钟作为锁相环的输入时,锁相环的锁定时间约为7μs,当以12M/bit的数据作为锁相环的输入时,经过约80个跳变边沿后锁相环锁定频率。48M本地时钟的锁定频率范围为47.829MHz48.175MHz,时钟抖动为143ps。锁相环锁定状态下压控电压为2.87V,电压毛刺不超过20mV。实验波形如图9所示,Y0为12M/bit的输入数据,Y1为电荷泵充电电路的控制电压,Y2为电荷泵放电电路的控制电压,Y3为振荡器的压控电压。

图9 锁相环实验波形

锁相环电路在正常工作时的平均功耗约为12.53mW。当模式一有效时,电路的平均功耗约为11.47mW,压控电压在2.81V2.95V范围波动。当模式二有效时,电流仅为2.746uA,平均功耗约为14uW,此时低通滤波器中保存的压控电压值为2.89V,PLL重新正常上电时能快速锁定振荡频率。

与传统的用于USB设备中的锁相环[10]比较,本文设计的锁相环无需外接晶振就能正常工作,成本节省了近40%,提高了板级电路的面积利用率,降低了板级电路的复杂度。表1列出了主要性能指标的比较,可见本文设计的锁相环在功耗方面有一定的优势,并且抖动和锁定时间都在同类应用锁相环设计的指标之内。

表1 本文锁相环和同类应用的锁相环设计比较

4 结束语

本文提出了一种应用于USB全速设备中的锁相环设计方法,增加了时钟信息提取单元和低功耗控制模块,采用了改进型鉴频鉴相器和差分延迟单元,可以输出不同频率的时钟以供全速设备使用。该锁相环工作时无需外接晶振,根据USB总线上12Mbit/s的数据信号就能实现频率锁定。48MHz本地时钟输出频率范围47.829MHz48.175MHz,时钟抖动143ps,锁定时间为7us,锁相环功耗约为12.53mW,满足USB总线协议要求,节省了成本,避免了现有方法的不足。

:

[1]ZHANG Yanlong.The design and realization of high precision DPLL in USB TT & C system [D].Changsha:National University of Defense Technology,2008 (in Chinese). [张彦龙.USB测控系统中高精度数字锁相环的设计与实现 [D].长沙:国防科学技术大学,2008.]

[2]CHEN Qingsong,WANG Jian.USB data transfer [J].Computer Engineering and Design,2006,27 (11):2077-2079 (in Chinese).[陈青松,王健.通用串行总线数据传输 [J].计算机工程与设计,2006,27 (11):2077-2079.]

[3]Behzad Razavi.Design of analog CMOS integrated circuits[M].CHEN Guican,transl.Xi’an:Xi’an Jiaotong University Publishing,2009:432-472 (in Chinese).[毕查德·拉扎维.模拟CMOS集成电路设计 [M].陈贵灿,译.西安:西安交通大学出版社,2009:432-472.]

[4]Roland E Best.Phase-locked loops design,simulation,and applications [M].Roland E Best. McGraw-Hill Professional Publishing,2007:482.

[5]Nanda Kumar Lakkoju,Sateesh Gudla,Bhanu Sridhar Mantravadi.AVR-USB data acquisition [C]//Kanyakumari,In-dia:3rd International Conference on Electronics Computer Technology April,2011:35-39.

[6]WANG Lei.Design of fully differential ring OSC for the CMOS phase locked loop [D].Shanghai:East China Normal University,2009(in Chinese). [王磊.基于全差分环形振荡器的CMOS锁相环设计 [D].上海:华东师范大学,2009.]

[7]XU Jiang,LIU Yuan,YU Qi.CMOS charge pump phase locked loop design with wide range and quick lock [J].Electronic Component &Device Applications,2010,12 (1):72-76 (in Chinese).[徐江,刘元,于奇.宽范围快锁定CMOS电荷泵锁相环的设计[J].电子元器件应用,2010,12 (1):72-76.]

[8]WEI Jianjun,LI Chunchang, KANG Jichang.Self-biased charge pump PLL with adaptive bandwidth [J].Journal of Sichuan University (Engineering Science Edition),2010,42(2):188-194 (in Chinese).[魏建军,李春昌,康继昌.自偏置自适应电荷泵锁相环 [J].四川大学学报 (工程科学版),2010,42 (2):188-194.]

[9]WANG Jin.The research and design of CMOS charge-pump phase-locked loop [D].Xi’an:Northwest University,2008(in Chinese). [王瑾.CMOS电荷泵锁相环的研究与设计[D].西安:西北大学,2008.]

[10]WANG Ying.Design and application of low jitter phase locked loop [D].Shanghai:Shanghai Jiaotong University,2008(in Chinese).[王颖.低抖动锁相环设计及应用 [D].上海:上海交通大学,2008.]