基于高速D/A AD9739 2.5GSPS的宽带信号源

唐大伟,吴琼之,孙宁霄,金兆健

(北京理工大学 信息与电子学院,北京 100081)

研究宽带雷达信号产生技术对雷达性能提高有重要意义,在目前的宽带雷达中,脉内宽带线性调频信号是一种常用的信号形式。采用数字方式产生宽带线性调频信号主要有两种方式,DDWS:波形数字存储直读方式(基于FPGA软件编程),DDFS:直接数字频率合成(基于DDS芯片)。DDWS通过对存储的波形进行采样,经过DAC编程模拟信号;DDFS通过相位累加、幅度查表和DAC生成模拟信号。DDWS工作频率比较高,但是灵活性不强,而DDFS虽然受限于FPGA的时钟频率,但是具有很强的灵活性,同时FPGA的工作频率随着集成电路技术的发展在不断提高,本文采用DDFS方法,即FPGA和高速D/A结合实现宽带信号源。

1 原理分析

传统DDS输出频率范围受到器件工作时钟影响,导致DDS直接输出频率上限较低,直接产生的中频信号中心频率和带宽都很有限,不能直接满足雷达系统要求。本设计DAC实时采样率为2.2 GSPS,AD9739[1]采集数据使用的是双通道DDR模式,这样每个通道数据的采样时钟频率可以降为D/A芯片时钟的1/4:550 MHz,但是FPGA内部逻辑仍然无法正确工作在550 MHz的时钟下,可以通过多通道合成的并串转换 技 术 来 解 决[2-4]。

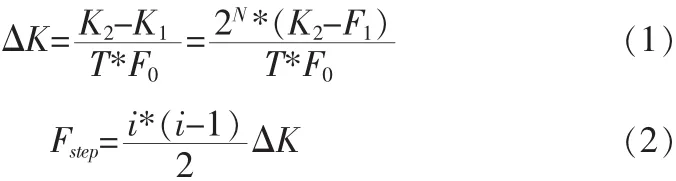

假设线性调频信号起始频率为F1,对应的频率控制字为K1,截止频率为F2,对应的频率控制字为K2,频率控制字位宽N=32,信号时宽为T,FPGA内部16路DDS工作时钟为FS,DAC采样频率为F0,生成DDS IPCORE时设置相位增量和相位起始值均为可编程模式。根据DDS原理可知,假设F1<F2,假设i为实际数据的第i个采样点,i处于[1:T*F0],则每个通道的初始相位控制字分别为K1,2*K1……16*K1,每个F0周期内线性调频信号频率控制字增量和第i个采样点频率控制字增量分别为

在FPGA内部,一共生成16个DDS IPCORE,每个核的参数PINC(相位增量控制字)和POFF(相位初始控制字)的值分别根据上述推导公式(1)(2)进行编程实现。根据线性调频信号的特点,最后通过并串转换将16路并行数据合成1路串行数据输出,得到需求的宽带线性调频信号。

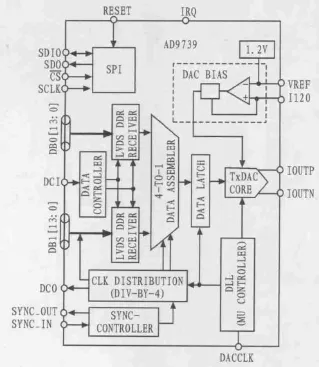

2 数模转换芯片AD9739

文中采用的AD9739具有14位DAC量化,该器件寄存器控制方式采用串行外设接口(SPI),可以通过FPGA对其进行配置,其接口采用低压差分信号(LVDS)接口,可以实现高采样率,本文就是利用AD9739高采样率的特点和FPGA的OSERDES技术来实现宽带信号源。AD9739的结构框图如图1所示。

图1 AD9739的原理结构框图Fig.1 Functional block diagram of the AD9739

如图1所示,该器件主要包括3个部分。

1)配置部分:AD9739内部有多达54个寄存器,用来控制芯片的数据接收,多芯片的同步,Mu clock工作,输出电流等功能,并且有部分寄存器是指示寄存器(只读),用户可以通过读出这些指示器的值来确认芯片目前的工作状态。图1中默认的4线SPI接口线包括时钟 (SCLK)、串行端口使能(CS)、串行数据输入(SDIO),和串行数据输出(SDO)。

2)时钟部分:AD9739芯片所有时钟全部为差分时钟,共5对,分别为:DACCLK:DA芯片的时钟输入;DCO:数据输出时钟,传输给 MCU;DCI:数据输入时钟;SYNC_IN和SYNC_OUT为多片同步时钟。本文中两片AD9739同步工作,需要利用SYNC_IN和SYNC_OUT实现同步。DACCLKC设置TxDAC核的数据更新率,它作为主时钟分配给内部和外部时钟信号。为了简化和主机程序的同步关系,AD9739传输一路LVDS时钟(DCO)给主机,其中DCO和DCI的频率相等。

3)数据部分:AD9739使用了双端口DB0[13:0]和DB1[13:0]同时传输数据,这样可以将数据的传输速率降为芯片时钟的1/2,可以提高数据传输的正确性,然后芯片内部把从两端口收到的数据合成一组。AD9739采集数据使用的是DDR模式,即当DCI的上升沿和下降沿同时采集数据,这样数据时钟的频率就降为芯片时钟的1/4,是数据传输速率的1/2。降低时钟的传输频率就意味着可以提高时钟的质量,这也可以提高高速传输数据的正确率。

3 系统设计与实现

3.1 原理框图

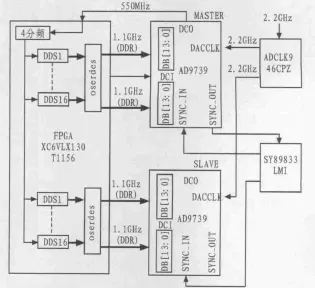

硬件电路的实现主要包括,一片XILINX公司的VIRTEX-6系列的 FPGA XC6VLX130T1156[5],两片 ADI公司的2.5GSPS高速D/A转换AD9739,一片Micrel公司的时钟扇出芯片SY89833L,一片D/A输入时钟芯片ADCLK946CPZ及开关电源芯片等,硬件实现框图如图2所示。

图2 系统原理框图Fig.2 System block diagram

如图2所示,本设计中用到两片AD9739同步工作,2.2 GHz差分时钟经过ADCLK946CPZ之后分别给到两片AD9739的DACCLK,而DCO作为数据输出参考时钟给到FPGA内部的DCM,在FPGA内部将DCO时钟频率进行4分频作为16路DDS的驱动时钟,再由OSERDES进行并串转化合成1路高频信号,FPGA将产生DCI和数据,DCI作为D/A的数据输入时钟,FPGA将保证DCI的采样沿能够采到双端口数据DB0和DB1的有效部分。

3.2 高速DAC与FPGA接口设计

XILINX公司的VIRTEX-6系列的FPGAXC6VLX130T1156具有300个LVDS差分逻辑接收通道,由于DAC的输入和FPGA的输出均设计为LVDS逻辑标准,因此DAC与FPGA可以直接相连[6-7]。本设计需要两片DAC同步工作,多片AD9739同步工作是需要保证所有的设备具有匹配的布线延迟,也就是两片AD9739在相同的时钟驱动下给予相同的数据流,DAC输出数据应该具有相同的相位关系。造成芯片之间相位模糊的主要来源是内部的4分频电路,由于上电之后分频器的状态未知,所以同步工作的方法就是确保具有匹配的布线延迟。本设计中,ADCLK946到两片D/A之间的PCB走线长度要匹配,这是确保时钟信号具有匹配传播延迟。

FPGA和AD9739实现高速信号发生过程如下:为了实现AD9739数据和时钟的时序同步,本设计利用AD9739内部LOOP CLOCK BUFFER和FPGA内部IODELAY实现时钟和数据对齐,其中DAC的环路时钟缓冲器可以通过SPI对寄存器进行配置,而FPGA的IODELAY是专门用来满足高速时序要求而设计的特定资源,假如以200 MHz时钟做参考举例,可以实现步进64ps的时序调整,DAC的时钟缓冲器和FPGA的PLL/DCM结合用于AD9739时钟和数据的同步传输。

3.3 上位机软件设计

上位机软件主要是通过串口和FPGA进行通信,上位机编程是在Visual Studio 2008环境中实现。开启软件可自动连接FPGA板卡,当系统与软件建立连接之后,软件将接管系统控制权,通软件界面选择播放通道以及对相应通道参数进行配置。需要配置的参数如下:Pulse Time(us):脉冲时间;Start Fre(MHz):信号起始频率;Final Fre(MHz):信号终止频率;PRT:信号周期重复时间。软件结构框图如图3所示。

图3 软件结构Fig.3 Software architecture

当信号的起始频率与信号终止频率相同时,系统播放单频信号。当信号的起始频率与信号终止频率不同时,系统播放线性调频信号。

4 实验测试数据

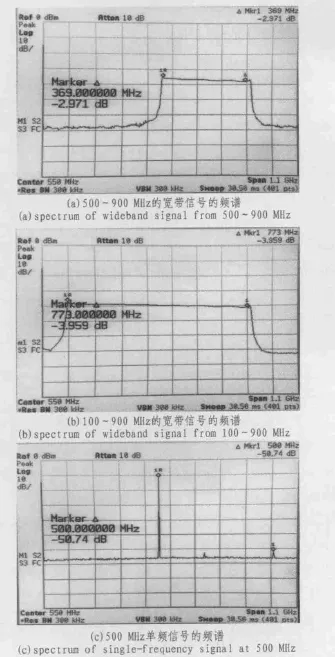

本设计实现了基于FPGA的多路并行DDS合成宽带信号源,系统工作时钟 137.5 MHz,D/A采样率为 2.2 GHz,输出频率范围1 MHz~1.1 GHz,频率分辨率小于0.5 Hz,D/A转换器量化位数为14位。实验测试结果如图4所示。

图4 用频谱仪测试DAC的输出Fig.4 Output waveforms of DAC using the spectrum analyzer to get

从实验截图可知,当信号源播100~900 MHz宽带信号时,带内平坦度约为4dB,当信号源播500~900 MHz时,带内平坦度约为3 dB。图4(c)为500 MHz时测得的无杂散动态范围,小于-50 dB,满足实际工程需要。

5 结束语

介绍了采样速率高达2.5GSPS的D/A AD9739,通过FPGA作为高速D/A的核心控制,实现了2.2GSPS实时采样率、14bit的D/A转换量化位数的双通道同步宽带信号源。通过对输出宽带信号和单频信号频谱的测试,与传统方法相比,结果显示该设计谐波杂散较高,带内平坦度较好,满足设计要求。

[1]ADI Corporation.AD9739 datasheet[EB/OL].[2013-3-21]http://www.analog.com/zh/digital-to-analog-converters/highspeed-da-converters/ad9739/products/product.html.

[2]祝明波.线性调频基带数字产生的关键技术研究[J].国防科技大学学报,1998(2):65-69.

ZHU Ming-bo.The key technology research of the linear frequency modulation baseband signal[J].Journal of National University of Defense Technology,1998(2):65-69.

[3]郭振永.线性调频信号DDS频率合成源的设计与实现[J].现代雷达,2005,27(3):56-59.

GUO Zheng-yong.The design and achievement of the linear frequency signal source that is based on DDS technology[J].Modern Radar,2005,27(3):56-59.

[4]蒋迺倜,江涛.并串转换合成法合成多通道宽带DDS信号[J].雷达与对抗,2009(4):31-33.

JIANG Qiu-ti,JIANG Tao.The multichannel wideband DDS signal based on the parallel-serial conversion[J].Radar and Confrontation,2009(4):31-33.

[5]Xilinx Corporation.Virtex-6 series FPGA data sheets[EB/OL].[2013-3-21]http://www.xilinx.com.

[6]王猛,吕卫祥.基于高速D/A AD9739的宽带信号产生[J].雷达与对抗,2011 31(4):55-58.

WANG Meng,LV Wei-xiang.The generation of the highspeed D/A AD9739-based wideband signal[J].Radar and Confrontation,2011,31(4):55-58.

[7]费元春,苏广川.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.