改进FlexRay总线的设计与实现

何浩洋, 穆建成, 马连川,曹 源

(1.北京交通大学 电子信息工程学院,北京 100044;2.铁道部 科学技术司,北京 100844 )

轨道交通列车运行控制系统(简称列控系统)是典型的安全苛求控制系统,列控系统由多个子系统组成,子系统又由多个分布子设备组成,如地面子系统由RBC、TCC、轨道电路、应答器、GSM-R通信接口设备等组成,车载子系统由车载安全计算机、应答器信息接收模块、轨道电路信息接收单元、测速测距单元、人机界面、列车接口等设备组成。虽然每个子系统和子设备是安全的,但如果系统和设备间的通信不安全会导致行车危险,需要故障安全通信,CTCS-2级、CTCS-3级列控系统通信中都具有故障安全特性。

在铁路、航空等安全理论和国际标准中IEC61508是比较基本和核心的。IEC61508指出,为防护通信中的安全风险引入了时间触发架构。TTP/C、FlexRay、TTEthernet是常用的时间触发总线,其中FlexRay是混合信道结构设计,总线访问静态时间消息采用TDMA方式访问网络,动态事件消息采用柔性时分多址(FTDMA)方式访问网络,具有很好的灵活性,因此是未来现场总线的发展趋势。为保证FlexRay总线能更好地应用于列控系统的故障安全通信中,可借鉴ARINC659的物理层对FlexRay总线进行改进。

1 FlexRay总线的改进设计

ARINC659背板总线采用4条总线冗余,4条总线采用半双工传输和交叉检验的通信方式。每一个BIU接收所有4组总线发送的数据,并进行交叉校验,从而检测出瞬态故障和硬故障,并能解决单个总线的故障,即可容忍一个总线的故障。

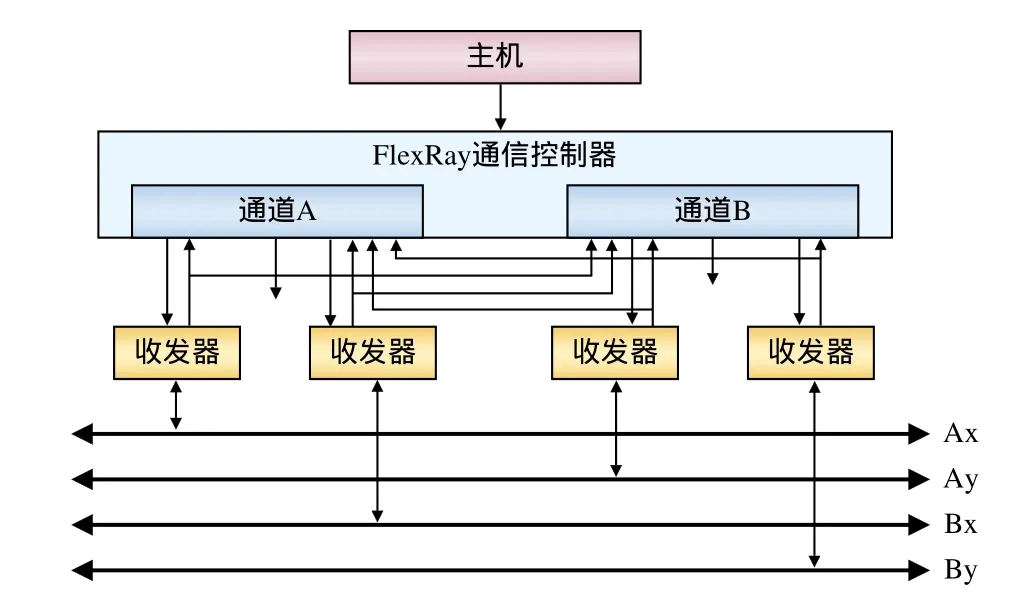

为保证FlexRay总线能够更好用于故障安全通信,一方面可以保留FlexRay总线采用时间触发机制时间确定性,以及灵活性的优势,另一方面可以对FlexRay容错能力不足和总线利用率不高的方面进行改进,通过借鉴ARINC659高可靠度和安全度的物理层,进一步提高总线的可靠性和容错性以及利用率。其具体框架如图1所示。

图1 改进的FlexRay总线节点结构

2 改进FlexRay总线的实现

针对改进的FlexRay总线,在FPGA上进行IP核的设计。首先采用Quartus II实现各个模块的设计,再将各模块统一综合。模块包括时钟模块、协议运行控制状态模块、时钟同步模块、介质访问模块和收发模块。

在FlexRay协议里,通信建立在重复的通信循环中。通信循环按照时间定义的元素分为4个时间层次:微时钟层、宏时钟层、仲裁格层和通信循环层。微时钟层的时钟大小由系统时钟确定,对于不同的节点可以使用不同的时钟。宏时钟层是实现全局时钟同步最小的时间单元。仲裁格层中静态段的时间单位为静态时隙,动态段的时间单位为小时隙(动态时隙)。通信循环层由静态段、动态段、符号窗和网络空闲时间段组成。

FlexRay总线上的节点一共有8个基本的协议运行控制状态,分别是默认配置状态、参数配置状态、就绪状态、唤醒状态、启动状态、正常主动状态、正常被动状态、中止状态,在各不同的状态下执行相应的功能。

介质访问模块主要完成数据帧的组帧与解帧。数据帧根据具体情况,从各状态寄存器和从主机接收到的数据获取所需要的信息,再经过11位的头部CRC计算和帧尾段24位的CRC计算,得到最终的数据帧。反之,解帧时也是先计算数据帧的头部CRC和总的CRC,然后与发送的CRC值进行比较,若一致则接收该数据,并更新状态寄存器的数据。

FlexRay协议采用分布式的时钟同步机制,每个节点通过其他节点发送的同步帧测量时钟计时,从而实现总线上的节点时钟同步。所有节点采用相同的方式进行时钟同步,相位校正在奇数周期的网络空闲时间进行,频率校正则在整个周期中都进行。

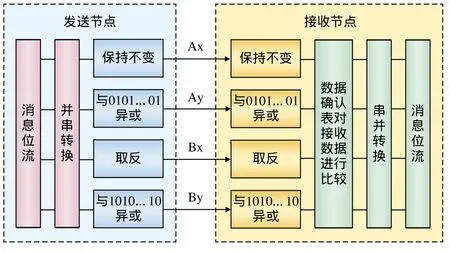

数据按照规范规定的位流进行传输。按照规范中所指出的编码方式得到数据帧或特征符的位流,接着将并行数据转换为串行数据,再根据ARINC659的底层对位流传输进行改进。接收时先仍按上述方式进行处理,对处理后数据根据数据确认表对其进行比较。再对接收到的数据进行串行转并行,得到最后的消息位流。数据位流的发送接收过程如图2所示。

图2 数据位流的收发

对改进FlexRay总线各模块设计完成后,即可根据需要搭建FPGA硬件开发板。开发板芯片为Cyclone的EP1C12Q240C8,采用5个开发板实现通信。

3 改进FlexRay总线的符合性测试

对于通信控制器,FlexRay发布的协议符合性测试规范中指出可以采用基于仿真环境和基于硬件环境的符合性测试。基于仿真环境的测试是采用Modelsim软件对设计的通信控制器进行RTL级的仿真。基于硬件环境的测试被测试对象是基于FPGA的FlexRay通信控制器,处理器采用Cyclone自带的Nios II。

开发板上的晶振是40 M,设置具体的参数:系统时钟为CLK:25 ns;微时钟Microtick:25 ns;宏时钟Macrotick :1 μs;静态段时隙:50 μs;动态段时隙:40 μs;符号窗时隙和网络空闲时间的时钟采用微时钟,即25 ns。对于通信循环,总的周期:5 ms;其中静态段时间:3 ms;动态段时间:1.8 ms;符号窗时间:120 μs;网络空闲时间:80 μs。

3.1 基于仿真的测试

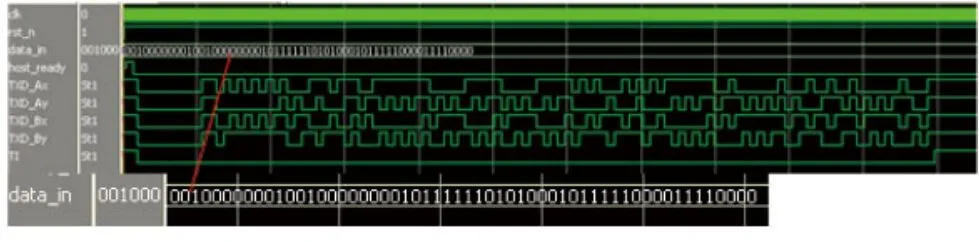

基于仿真环境的测试,通过编写Testbench实现RTL级的仿真。数据的发送仿真如图3所示。

图3 改进FlexRay总线静态段的发送

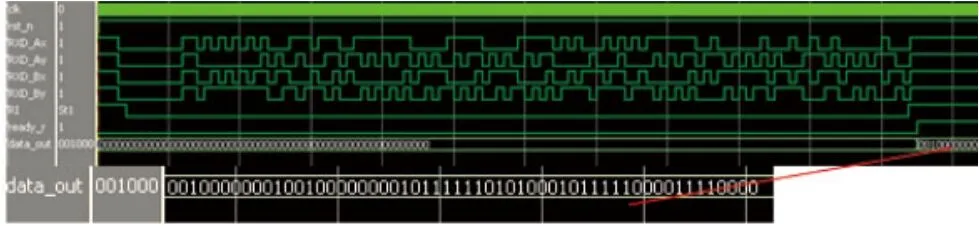

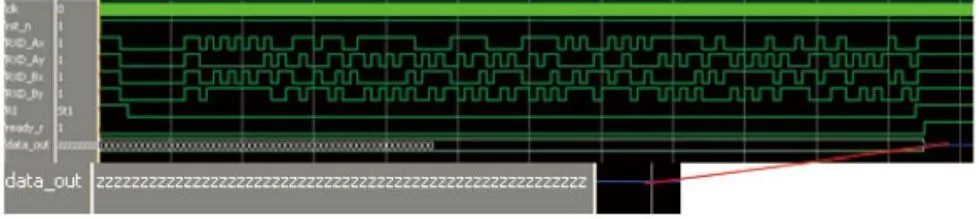

对于数据的接收,若传输未出现错误,则能正确接收到数据。仿真图如图4所示。

图4 改进FlexRay总线静态段的接收

通过对数据帧发送信号线的波形分析,可以看到与规范中的位流编码一致,设计符合要求。

若一个通道传输错误,也能正常接收数据,假定Bx通道传输错误,数据接收仿真如图4所示。若一位数据的传输时发生两处错误,假设Ay和Bx均发生错误,数据接收仿真如图5所示。

图5 两条通道出现错误的帧接收

通过仿真可见,若某位数据的传输过程中出现一个通道错误时,通信控制器仍然能正确接收到数据,改进后的总线具有容错能力。若传输过程中出现两通道同时错误的情况下,通信控制器不能解析收到的数据,输出高阻。

3.2 基于硬件的测试

处理器采用Nios II内核,系统参数与仿真设置参数相同,节点2在静态段时隙为15发送16 bit数据0x0215,节点3在静态段时隙为25发送16 bit数据0x0325,节点4在静态段时隙为35发送16 bit数据0x0435,节点5在静态段时隙为45发送16 bit数据0x0545,节点1接收数据。

测试节点4故障对传输的影响。首先设置Bx通道传输错误,测试数据能否被接收;然后设置Ay和Bx通道均发生错误,测试数据能否被接收。对其他节点仍正确设置。

测试结果表明,对于正确传输的通道,能正确接收到数据。对单通道Bx传输错误,仍能接收到节点4发送的数据,可见单个通道的故障不影响数据的通信,即改进后的FlexRay总线允许单个通道的传输故障。通过对改进后总线容错能力的测试,IP核的设计与要求容错能力一致,即可容忍一条通道的传输错误。

4 结束语

为保证FlexRay总线更好地应用于列控系统的故障安全通信中,可借鉴ARINC659总线对其物理层进行改进。根据FlexRay协议符合性测试规范,首先利用Modelsim对设计的各模块进行RTL级的仿真,以验证设计模块的符合性。然后采用Cyclone自带的Nios II内核作为主机控制通信控制器,进行开发板的通信实验和主要功能的符合性测试。测试结果表明改进的FlexRay总线能够正确完成调度和数据的收发,且有更好的容错能力,能容忍一个通道传输的错误,对两个通道同时故障,可导向安全侧,因此改进后的FlexRay总线能更好地应用于故障安全通信中。

[1] Functional safety of electrical/electronic/programmable electronic safety-related systems German version EN 61508: 2010[S] . 2010, 4.

[2] FlexRay Consortium. FlexRay Communications System Protocol Specifi cation Version 3.0.1 [S] . 2010.

[3] Arinc Specifi cation 659 Backplane Data Bus[C] . The Airlines Electronic Engineering Committee, DEC. 27, 1993.

[4] 刘 欣,杨志家.FlexRay通信控制器收发功能的研究和实现[J] .微计算机信息,2007,23(6):266-268.

[5] FlexRay Consortium. FlexRay Communications System Protocol Conformance Test Specifi cation Version 3.0.1 [S] .2010.