ARM/DSP 双核系统的通信接口设计

李 洋,张 燕,闫学昆,罗 明

(北京市海军核化安全研究所,100077)

DSP 系统与ARM 系统都各有优势,如果将二者进行有效地结合,将其设计为双处理器的嵌入式系统,则二者的优势将得以更好地彰显,从而可以使设计出来的系统能够很好地满足数据处理和传输所要求的实时性和高效性。鉴于此,下面主要针对ARM 和DSP 结合的双核系统的通信接口设计方法进行分析,分别从系统的总体设计、通信接口设计两个方面来进行讨论。

1 ARM/DSP 双核系统总体设计

1.1 系统硬件平台设计

ARM 芯片具有比较良好的控制性能,在嵌入式系统中主要用来进行控制工作或者对一些数据进行处理。为使其发挥更好的性能,对于CPU 有一定的要求,首先要具有较低的功耗,时钟频率要大,这样才能使操作系统很好地运行;另外,要求其接口的种类也要多,从而可以使性能更好地进行扩展和发挥。综合这些要求,在开发平台中可以选择HY7202 作为CUP。

DSP 主要负责数据运算,它比较擅长于对数字信号进行处理。在对DSP 进行选购时,要充分比较其性能,并且综合考虑其性价比。在这里,我们选择的是T1 公司的32位定点DSP,因为它目前的应用较为广泛,主要应用于各类通信设备或者便携式应用中。与同类商品相比,具有很高的性价比。为了满足数字视频和数字图像等数据吞吐量比较大应用场合的处理要求,选择了T1 公司的TMS320DM642(简称 DM642)芯片,它是专门面向多媒体应用的,并且具有比较高的时钟频率,可以满足我们的设计要求。

1.2 系统软件平台设计

系统的软件平台主要是ARM 的设计和DSP 的设计,另外还有二者的接口软件设计。对于ARM 的设计,本文选用了Samsung 公司的S3C6410 芯片,该处理器芯片具有体积小、成本低、功耗低以及性能高等优点,主要是针对移动通信和多媒体处理的应用而设计的。S3C6410 内部集成了很多种具有较高性能的支持多种格式的视频编解码的接口,功能非常强大,并且具有十分丰富的内部资源接口。图形界面的设计选用了图形界面以MicroWindows 0.9 及其控件库FLNX 提供嵌入式图形界面平台。系统平台可以进行网络通信,并且功能很完备,借助WEBSERVER、FTP、TELNET、INETD 等网络工具和应用程序,可以开发基于Internet 的网络终端、远程控制、远程数据采集、远程数据处理产品,并且开发起来很方便。在应用程序层,集成了窗口管理程序、网络浏览器、flash 播放器、文本编辑器、游戏、数字示波器等,并集成了机顶盒上网解决方案。

DSP 部分可以提供完整的HPI 驱动程序和通信协议,可以通过增加相应的数据处理来实现对算法程序的控制,利用HPI 并行接口和主机的ARM 通信实现数据之间的交换,可以用到对实时处理有一定要求或者需要进行相关控制的领域中。

DSP 和ARM 也可以独立开来,分别作为两个独立的系统使用,因为它们都有完整的子系统软件。子系统之间可以进行联系的关键在于DSP 器件拥有自己的HPI 接口。

2 ARM/DSP 的通信接口设计

外部HPI 信号是一个特别方便的接口,对于不同的主机终端设备来说都很有利。ARM 处理器和DSP 芯片之间的通信可以通过HPI 接口来进行,在整个进行通信的过程中,ARM 可以访问DSP 内部或者外部的存储器,对于DSP 所发出的中断申请也能有所响应。DSP 系统对于ARM 而言,类似于它的一个外部设备。

由于S3C6410 中没有一个能够完全符合DM642 HPI 接口时序的外部接口,所以本文的设计中选择的外部存储器接口是SROMController(SROMC),该接口比其他任何接口都更与S3C6410 中时序和DM642 HPI 接口类似。S3C6410 所表现出来的的支持性能很好,对于外部8位/16位NOR Flash、PROM、SRAM 存储器都能很好地匹配。可以将它分为6个bank 存储空间,其中每个bank 空间的容量最多可以达到128MB。

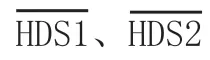

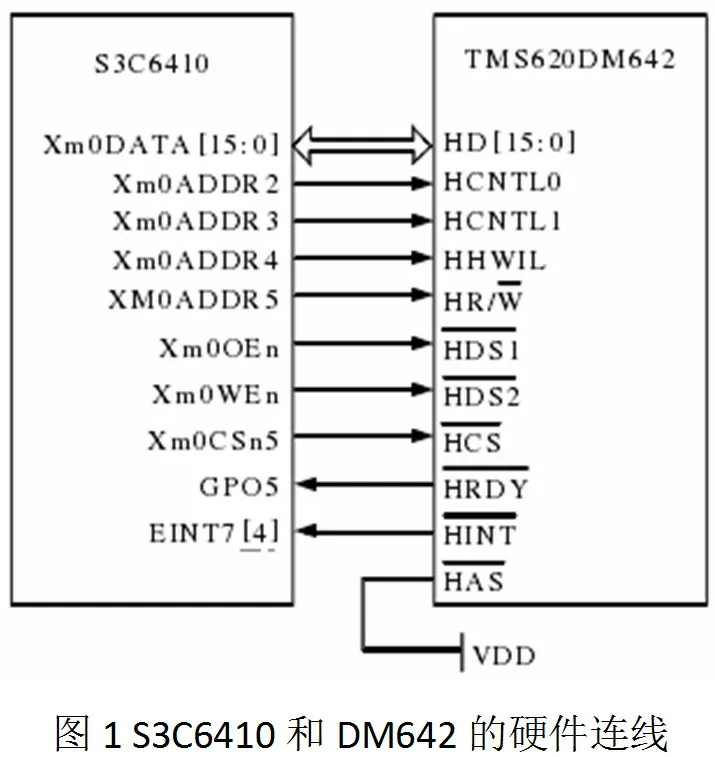

下图1 表示的是S3C6410 和 DM642 的接口电路。系统将HPI 接口所有的控制寄存器、地址寄存器、数据寄存器进行统一编址,将 HPI 的 16位数据总线HD[15:0]与S3C6410 的MemoryPort0 的16位数据总线 Xm0DATA[15:0]相连,通过这种方式来实现数据传输通道与主机之间的信息传输。但是由于该芯片一个字的大小为32位,因此所有和主机之间进行传输都不能直接一次性传输,而是需要由两个连续的16位半字组成。其中控制信号线 HCNTL 与数据总线Xm0ADDR 相连用来控制访问 HPI接口寄存器的类型;HHWIL 与地址线 Xm0ADDR4 相连,用于识别传输的是第1个半字还是第2个半字,若为低则表示第1个半字,为高则表示第2个半字;HR/W 与Xm0ADDR5 相连,进行读写控制;HDS1、HDS2 分别与 Xm0OEn、Xm0WEn 相连,作为主机发出的两路数据选通信号;HCS 与Xm0CSn5 相连,是主机发出的片选信号,通过如图2 所示的内部逻辑运算组成数据选通信号;HRDY 接至S3C6410 的GPO5 脚,用来指示当前 HPI 访问的准备就绪状态;HINT 接至EINT7 引脚,用于DM642 向主机发送中断申请;HAS 为地址选通信号,由于S3C6410 的Memory Port0 具有独立的地址和数据总线,可以不使用HAS,固定接至高电平。

图2 输入选通逻辑

SROMC 控制HPI 接口的读写时序在设计时,要严格按照DM642HPI 接口的时序来进行。访问HPI 接口的正确时序可以对相应的信号端口进行一定的控制来产生,然后按照所产生的时序进行相应的设计。

3 结语

本文主要探讨了DSP/ARM 双核系统的通信接口设计,该设计结合了DSP 和ARM 两种处理器的优点,不仅将ARM 系统在人机交互和网络控制等方面的优势很好地体现了出来,同时还很好地发挥了DSP 系统在音频、视频等多媒体数据处理方面的高性能的优势。再加上HPI 接口的设计,可以使得二者之间很方便地进行通信与数据交换,基于以上这些优点,这种DSP/ARM 双核系统的通信接口设计目前得到了越来越广泛的应用,相关的设计技术也在不断发展。这一设计方法对于现代大多数的嵌入式系统的设计都具有很高的适用性,经过比较长时间的运行测试,发现其具有一定的可靠性和稳定性,并且对于实时性处理也能满足,具有良好的发展前景。

[1]向强.MPC860T 与 DSP 的 HPI 通信设计[J].单片机与嵌入式系统应用,2010(3):22-27.

[2]Texas Instruments Incorporated,卞 红 雨,纪 祥春.TMS320C6000 系列 DSP 的 CPU 与外设 [M].北京:清华大学出版社,2008:206-234.

[3]孙德伟,祁晓磊.基于 HPI 接口实现 DSP 和 ARM 间的通信[J].微处理机,2009(3):61-63.

[4]廖义奎.ARM 与 DSP 综合设计及应用[M].北京:中国电力出版社,2009:363-392.