基于TQ 时序分析器的时序分析和约束

李 珈

(湖北科技职业学院,湖北武汉,430074)

0 引言

一般的FPGA 工程师在进行电路设计的时候更加侧重于代码的编写与硬件测试,若是最高频率没有达到要求,最先想到的也是换一个速度更快的芯片,而不会去关注时序分析和约束的问题。实际上,当设计比较简单,且运行频率比较低的时候,不加任何的时序约束,FPGA 软件都可以综合出来可用且相对较可靠的代码,但当设计比较复杂,运行频率比较高的时候,不做时序分析,不加上一些必要的约束,就很难保证设计能且稳定的运行在所设定的频率上。

所有的FPGA 厂商都提供静态时序分析(STA,Static Timing Analysis)工具,可对设计的时序性能作出评估。TQ(TimeQuest)是Altera 公司的第二代静态时序分析器,它采用业界标准的设计约束文件(SDC 文件,Synopsys Design Contraint File),能够适应FPGA 的密度和速率增长的趋势,完成传统的FPGA 时序分析工具很难分析的设计接口。TQ 提供多种约束命令和图形化的操作界面,简化了生成时序约束文件的方法,提高了时序报告阅读的效率。

1 静态时序分析的概念

静态时序分析是相对于动态时序仿真而言的,由于动态的时序仿真占用的时间非常长,效率低下,因此STA 成为最常用的分析、调试时序性能的方法和工具。那么什么是静态时序分析呢?它可以简单地定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路,通过分析每个时序路径的延时,计算出设计的最高频率,查看系统时序是否满足设计者提出的要求,同时可以发现时序违规。

所谓条条大路通罗马,在实际的电路中,一个信号从起始点传播到终点可能会经过不同的传输路径,所以对于同一组起始点和终点,会存在不同的时序路径(timing path),而由于不同的传输路径的参数会有差异,所以这些时序路径的延迟就不同。举一个简单的例子,假设信号从输入到输出需要在FPGA 内部经过一些逻辑延时和路径延时,系统要求这个信号在FPGA 内部的延时不能超过15ns,而开发工具在执行过程中找到了如图1 所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns 及18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。

图1 静态时序分析模型

STA 工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入时序约束,以便STA 工具能输出正确的时序分析结果。因此静态时序分析的前提是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。

2 基于TQ 时序分析器的时序分析和约束

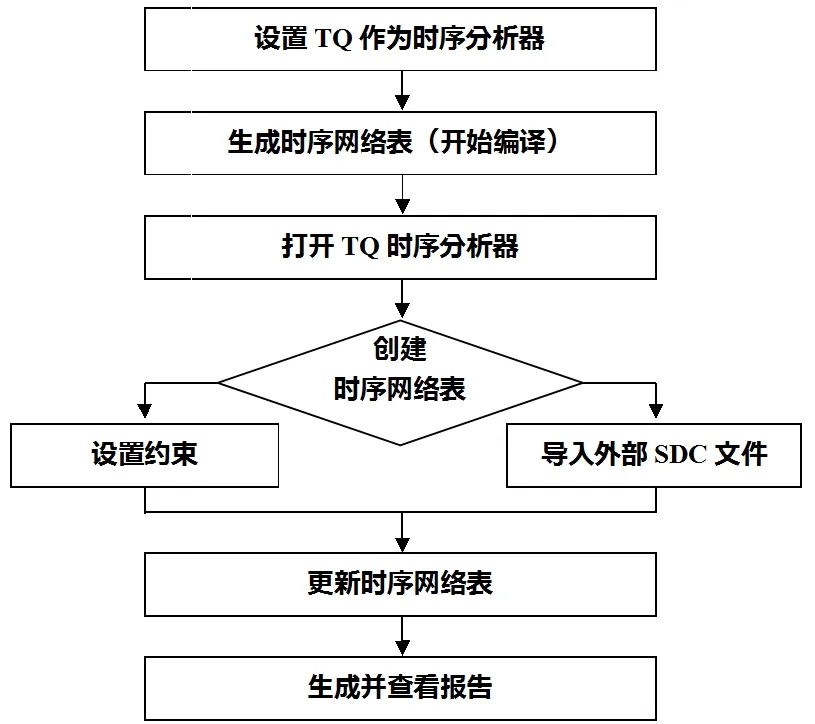

TimeQuest 时序分析器可用于分析设计中所有逻辑,并有助于指导Fitter 达到设计中的时序要求。设计者可以使用时序分析器产生的信息来分析、调试并验证设计的时序性能;还可以使用快速时序模型进行时序分析,验证最佳情况(最快速率等级的最小延时)条件下的时序。TQ 时序分析器采用SDC 文件格式作为时序约束输入,不同于Timing Analyzer采用QSF(Quartus Settings File)约束文件。这正是TQ 的优点:采用行业通用的约束语言而不是专有语言,有利于设计约束从FPGA 向ASIC 设计流程迁移;有利于创建更深入的约束条件。TQ 分析器的操作流程如图2 所示。

由此可见,TQ 时序分析器进行约束和分析的对象是FPGA 器件的底层物理单元,均来自Quartus II 编译流程各阶段的编译结果,因此二者是紧密结合在一起的。Quartus II 编译中的“分析与综合”之后,会进行“映射”,生成的数据库对应FPGA 器件的物理结构,可以供TQ 进行时序约束之用。由于“映射”过程实际是预先布局过程,尚未执行时序驱动的布局和布线工作,也没有读入引脚位置等约束信息,所以在这一步进行的时序分析是时序预估,不能获得准确的时序分析结果;在获得时序约束信息后进入编译中的“适配”环节,对应的操作是布局和布线,这一环节会努力按照时序约束的要求进行布局和布线优化,并生成FPGA 最终实现结果的时序网表,TQ 根据这一网表进行分析,可以反映最终的时序特性,检查适配结果是否满足了时序约束的要求。

好的约束必须以好的设计为前提,没有好的设计,在约束上下再大的功夫也是没有意义的。不过,通过正确的约束也可以检查设计的优劣,通过时序分析报告可以检查出设计上时序考虑不周的地方,从而加以修改。通过几次分析-修改-分析的迭代也可以达到完善设计的目标。因此,设计是约束的根本,约束是设计的保证,二者是相辅相成的关系。

图2 TQ 时序分析器操作流程图

3 结语

对自己的设计实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA 工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

[1] Altera 公司.TimeQuest 时序分析仪为FPGA 设计分析提供自然的SDC 支持[J],半导体技术,2006 :86.

[2]周海斌.静态时序分析在高速FPGA 设计中的应用[J].电子工程师,2005:31(11),41-43.

[3]刘福奇.FPGA 嵌入式项目开发实战[M].北京:电子工业出版社,2009.