新型ECT数据采集系统设计与实现

陈德运, 高明, 李伟, 王莉莉, 王飞虎

(哈尔滨理工大学计算机科学与技术学院,黑龙江哈尔滨150080)

0 引言

电容层析成像技术(ECT)是一项基于电容敏感原理的过程层析成像技术。它具有响应速度快、与被测物流非接触、安装简便及成本低等特点,能提供封闭容器及管道内部物流情况的二维或三维可视化信息[1],在工业过程参数的可视化检测应用中已经成为一种非常有发展潜力的技术。目前,ECT系统主要由多电极电容传感器、数据采集系统以及成像计算机等构成,其中数据采集是最为关键的中间环节[2]。

依目前的技术,ECT探测器系统的最大成像速度大约是100帧/s,难以保证成像系统的实时性。在数据采集系统中使用大量的模拟器件,如模拟解调器以及模拟滤波器因为受到自身精确度的限制以及其他因素的干扰,测量的精确度更加难以保证。以上这些不足都将削弱成像的准确性,因此有必要对现有的ECT数据采集系统进行改进。

1 ECT数据采集系统工作原理

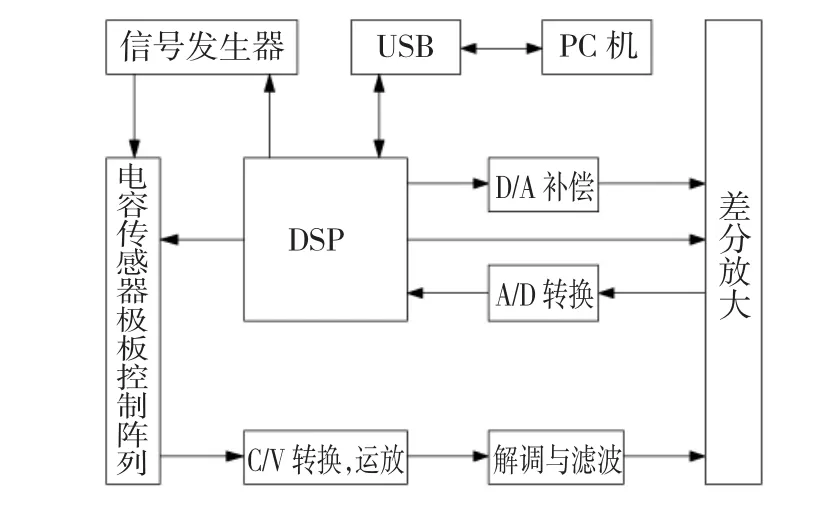

图1 ECT数据采集系统总体框图Fig.1 Structure chart of the date measure and acquisition system

ECT数据采集系统的总体流程如图1所示。目前ECT数据采集系统的工作原理是以DSP作为采集系统的核心控制单元,首先DSP向信号发生器发出指令,使其产生正弦或者余弦的电压激励信号Vi(t)=Asin(ωt)或者 Vi=Acos(ωt),将该激励信号加载到激励电极上,同时该信号也作为模拟乘法器的参考信号。将电极板检测到的数据传至C/V转换电路,当C/V转换电路进入到稳定的状态时,运放器将稳定的电压信号V0(t)=(Cx/Cf)Asin(ωt)或者V0(t)=(Cx/Cf)Acos(ωt)输出,输出信号将与信号发生器输出的参考信号同时进入模拟乘法器进行解调,将解调后的信号传送到低通滤波器,将不需要的高频交流分量过滤掉,最后将得到的直流分量进行模数转换。DSP作为控制单元将模数转换后的数字信号通过USB接口或者SPI串行接口传递给成像计算机。成像计算机接到数据后运用相应图像重建算法对其进行图像重建[3]。

表1给出了当前ECT数据采集系统各个环节所用的时间。由表可知,模拟解调所需时间最多,如何降低ECT数据采集系统运行时间,提高数据检测精确度是目前研究的重点。

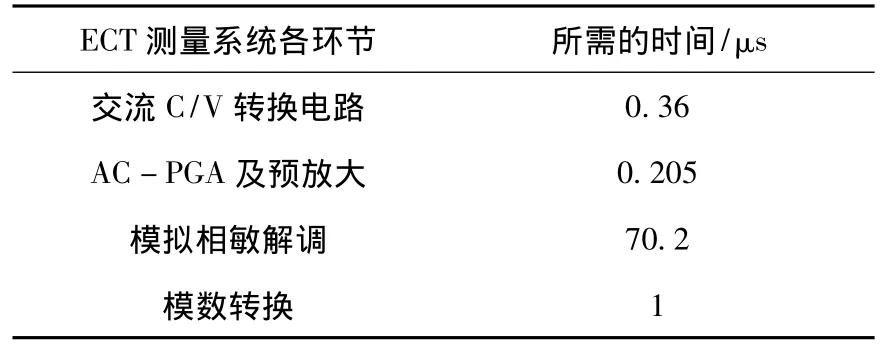

表1 ECT测量系统各环节所用时间Table 1 The time required for each part in ECT measurement system

2 基于FPGA的改进型数据采集系统

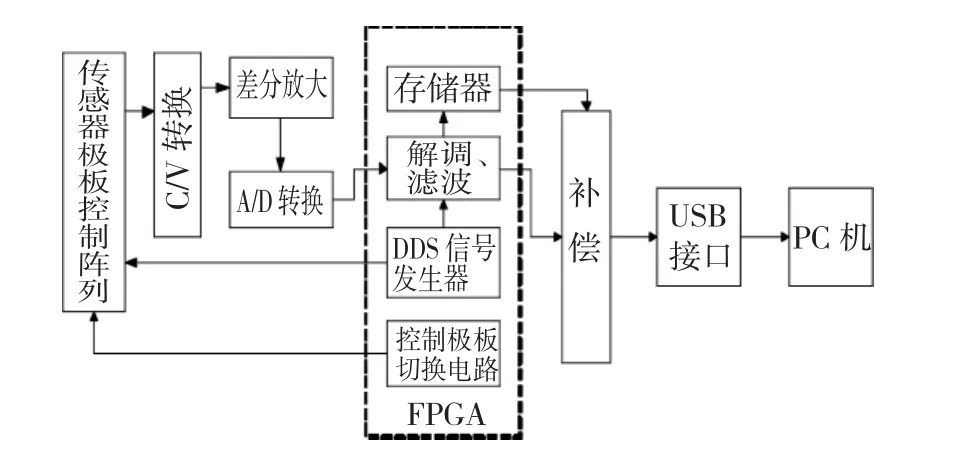

ECT数据采集系统受到模拟器件自身条件的限制,使测量精确度、速度及成像的质量都难以进一步提高。目前,FPGA技术发展迅速,以应用到大量工业化制造业[4]。为了提高ECT数据采集系统的精确度以及成像的速度,本文提出了一种以现场可编程门阵列(FPGA)作为ECT数据采集系统的核心控制单元的改进型数据采集系统。图2为改进型ECT数据采集系统结构图。

图2 改进型ECT数据测量与采集系统Fig.2 Structure chart of the improved date measure and acquisition system

如图2所示流程,FPGA作为系统的控制单元控制着交流激励电压信号的产生;控制每个电极在三个状态(激励、检测和接地)之间的转换;协调A/D转换的采样时钟。在开始一个周期的电路测量时,首先FPGA控制产生交流激励电压加载到激励电极上,然后检测选中电极对之间的电容值,通过C/V转换电路将其转换成电压值,用A/D转换电路将输出的电压值直接模/数转换,然后将数字化的数据在FPGA内部进行数字解调,解调完成之后,将结果送入FIFO缓存中,最后通过USB并行接口将所需数据传送到成像计算机进行图像的重建。

2.1 基于FPGA的信号发生器设计

在ECT数据采集系统中交流的正弦或余弦信号发生器是整个系统设计上重要环节之一,标准的交流正弦或余弦信号发生器要求具备波形的失真要小和波形幅值要稳定这两个基本要素。目前,主要有模拟信号发生器和数字信号发生器这两种信号发生器类型。

由于生产成本比较低,并且电路结构简单,输出信号失真比较小,模拟信号发生器使用的范围要广一些。但模拟信号发生器对输出信号的幅度值和信号的频率调整存在难度,研究人员逐渐把注意力转向数字信号发生器的相关设备[5]。

DDS技术的工作原理是:在参考时钟的驱动下,相位累加器对频率控制字进行线性的累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,经过模/数转换器得到相应的阶梯波,最后利用低通滤波器对这个阶梯波进行平滑处理,最后得出所需要的频率平滑、波形连续的信号。它为应用系统提供远高于模拟信号的信号。

目前所说的知识产权核就是IP Core,它在使用之前就已经设计好了,并且进行了比较严格的测试,使电路功能模块得到了最大的优化。Xilinx公司的FPGA的DDS模块IP Core能输出正弦函数、余弦函数和正交函数三种信号形式,它的旁瓣抑制比的范围是18 dB~115 dB,最小的频率分辨率是0.02 Hz,并且可同一时间支持16个通道。

ECT电容传感器激励信号频率的选取对ECT探测器系统的整体精度有着很重要的影响,根据现有实验得出的数据在激励频率为500 kHz时,整个系统会具有很好的线性和稳定性。在IP Core用户界面设置相关参数,可生成符合要求的500kHz正弦或余弦激励信号。这样不仅提高了激励信号的精度而且降低了ECT系统的成本。

2.2 ECT电容传感器极板控制电路设计

目前对ECT探测器系统激励电路与检测电路的设计,大多数实验都采用所有的电极板都使用一个激励电路的电路结构方式,而检测电路有两种方式比较流行。一种是每个电极板都独立的占用一个检测电路,互不干扰,也称作是并行模式。另一种是所有的电极板都使用唯一的一个检测电路,相互联系,也称作是串行模式[7-8]。

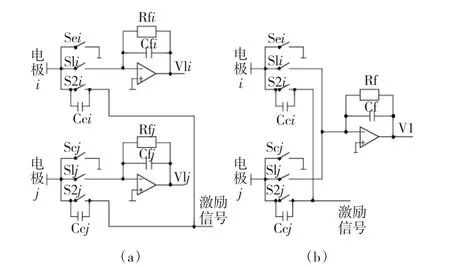

如图3所示,为电极板控制电路。在图中左侧的(a)图是每个电极单独使用一个C/V转换电路;图中右侧的(b)图是所有的电极共同使用一个C/V转换电路。

图3 电极控制电路Fig.3 Electrode control circuit

由图中的电路结构可知,当激励电压加载到电极i,检测电路接到电极j时,则电子开关S2i,S1j闭合,电子开关 S1i,S2j,Sei,Sej断开。当激励电压加载到电极j,而检测电路连接到电极i上时,电子开关 S2j,S1i闭合,电子开关 S1j,S2i,Sej,Sei断开。

论文对实验环境以及实验的开销等方面进行了综合的考虑,设计的ECT数据采集系统极板控制电路采用串行的检测模式进行。当采用三电极激励双电极检测的方式对电容传感器进行测量时,即当电极组合1为激励时,激励电压加载到电极1、2、3这三个极板上,检测电路连接到极板4、5上面,其余的那些电极板则接地。按照排列组合原理对其它电极进行循环采样,一直到192个不同值都被测量出来,就完成一个周期的测量[9]。电容传感器的每一块电极板都有三种工作模式,分别是作为激励的电极板、作为检测的电极板,以及电极板接地[10]。这样就需要设计一个电极板控制电路来对电极板不同工作方式进行切换。

采用16电极的ECT电容传感器,由于每个极板有三个控制开关,因此总共有48个电子开关对极板进行控制。选取FPGA上的48个引脚分别对这48个电子开关进行控制。FPGA内部,在时钟的控制下,不同时刻不同引脚或为高电平或为低电平,从而控制电子开关的闭合与断开,以达到极板工作方式的切换。采用这种控制方式可以降低系统组建的成本,并且节约占用空间,提高ECT的系统实时性。

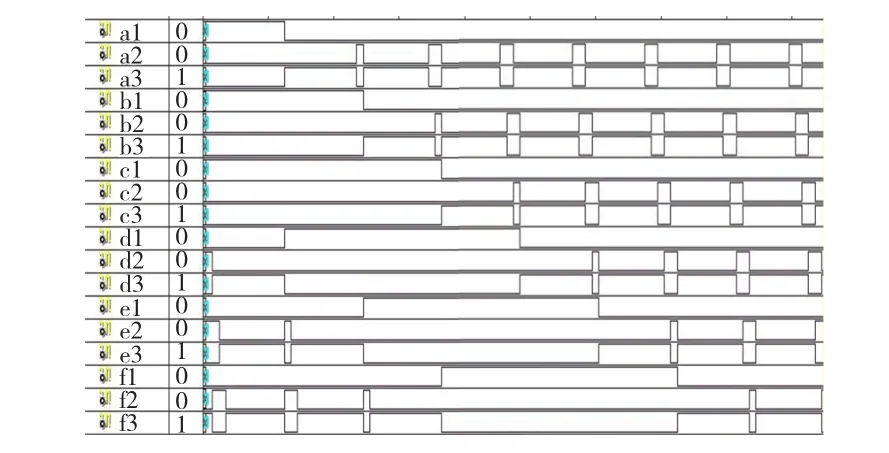

对所编写的电极板控制程序进行仿真,仿真的过程是在Xilinx公司的ISE仿真软件下进行的。如图4所示,为电极板控制程序的功能仿真的结果(部分)。从功能仿真的结果来看,所编写的程序是正确的,同一时刻一个电极板上只有一个电子开关闭合,也就是处于一种工作状态。在时序上每个电子开关都保持顺序连接与断开,保证了测量的准确性。与模拟器件相比较,减少了所用器件,简化了电路结构,整体系统的体积也变得精巧实用。

图4 功能仿真结果Fig.4 Results of functional simulation

2.3 数字解调电路设计

在ECT数据采集系统中,数字解调是指由模/数(A/D)转换器对经过C/V转换电路的信号进行采样,然后将数字化的信号传送至高性能的数字信号处理器,在处理器内部利用数值计算的算法计算出被测信号的幅度数值和相应的相位信息[11-12]。

ECT探测器系统数字解调模块一般是采用正交序列解调的方法,该解调方法是将匹配滤波器的相关理论运用到里面。匹配滤波器在原理上是属于线性滤波器,在白噪声的影响下使输出的信噪比达到最大值。

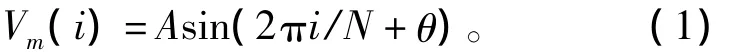

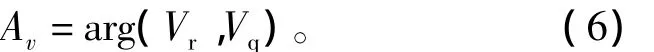

正交序列的算法如下:

设Vm(i)为被解调的信号,即

令r(i)为被解调信号同相参考信号,q(i)为被解调信号正交参考信号,有

在以上的3个式子里,N代表着每个激励信号在一个周期内的采样点数,θ是介质引起的相位移,设Vr为Vm的实部、Vq为Vm的虚部,则由数学上三角函数的正交性可得

则可得Vm的幅值为

以上式子中的参考信号是经过事先的计算出来并且存储在ROM内部的正弦和余弦函数数值的表。因而,FPGA的数字解调过程就是在ROM内查表来求取离散的正弦、余弦函数参考值。然后将这些参考值与采样得到的离散信号进行成累加,接下来就可以用这些乘累加得到的实部信息Vr和虚部信息Vq来计算出被测信号的幅度值。

在ECT系统中,运用数字正交解调方法具有非常明显的优点:

首先,数字正交解调方法的计算量相对来说是较小的,如当对有N个采样点来进行采样时,由原理图可知正交解调法进行乘法的次数是2N次,累加运算的次数是2(N-1)。

其次,数字相敏解调比起模拟解调执行的效率要高一些,并且占用的内存资源相对来说要少。正交解调法的计算过程是不需要等待着下一个采样点到来才开始运算的,并且所采集的数据在计算完成之后也不需要在继续保存。

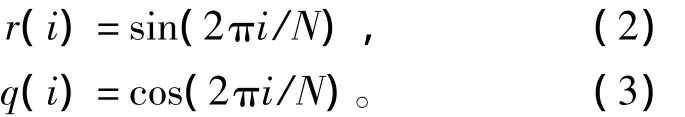

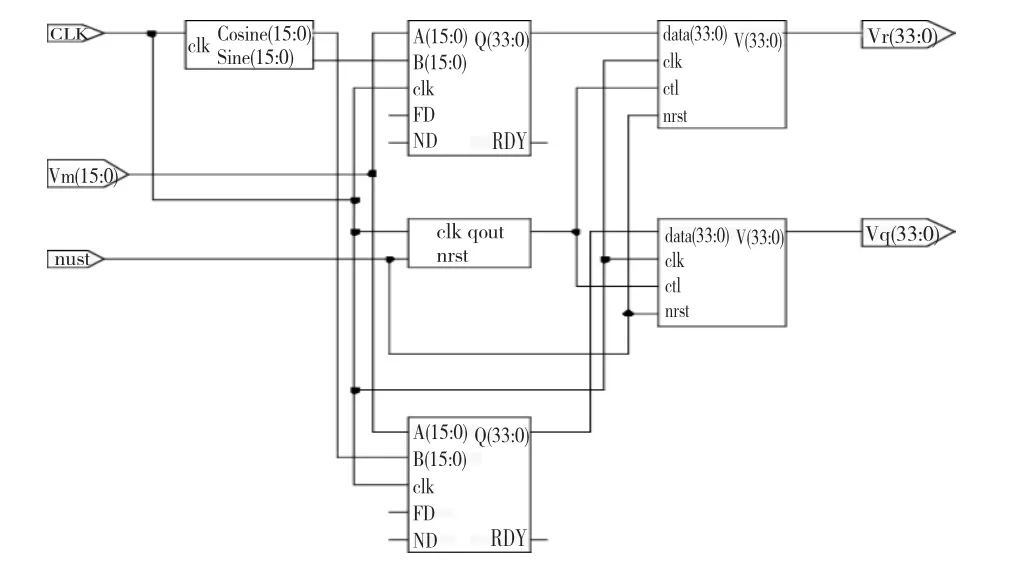

将数字相敏解调器的算法用Verilog语言进行编程,运用相关仿真软件进行仿真,最后用FPGA实现数字相敏解调的功能。图5为运用ISE仿真软件实现的数字相敏解调器RTL逻辑原理图。

图5 数字相敏解调器RTL逻辑原理图Fig.5 Digital phase-sensitive modem RTL logic diagram

3 仿真与实验结果分析

基于FPGA的ECT数据采集系统是将经过C/V转换电路的模拟电压值直接数字化,在FPGA内部对信号进行解调。这样省去了传统的模拟解调与滤波,差分放大等过程,大大降低了噪声,提高了精确度。下面对基于FPGA的数据采集系统性能进行实验仿真测试和分析。

首先在传统的ECT数据采集系统的条件下进行测试,取激励信号频率和参考信号频率均为500 kHz。根据图1所示的流程可知,在运行时,首先要经过C/V转换及信号放大,根据测试,这个过程需要0.565 μs微秒。然后进行模拟信号解调及模数转换,需用时间71 μs左右。每幅图的采样点数为192个,采集一幅图所用时间大约是0.01 s。

接下来在基于FPGA的改进型ECT数据采集系统条件下进行测试,取激励信号频率和参考信号频率均为500 kHz。由图5所示的采集流程可知,在数字相敏解调器内部,ADC的工作频率为1 MHz,是输出模拟电压信号频率的二倍。采用10位×10位的乘累加器(MAC)的工作频率可达10 MHz。MAC的工作频率高于ADC的工作频率,因此数字相敏解调时间(100 ns)可以忽略不计,在下一个时钟周期就可得到解调结果。根据图2的工作流程,采集一幅图像所用的时间大约是0.001 2 s。表2为两种检测条件下采集时间的对比。

表2 数据采集时间对比Table 2 Comparison of data acquisition time

由表2实验对比分析,基于FPGA的改进型ECT数据采集系统与传统的ECT数据采集系统相比,数据采集速度明显提升。这主要因为在基于FPGA的改进型ECT数据采集系统中信号解调这一环节省去了大量时间,从而降低了每幅图采集所需的时间。

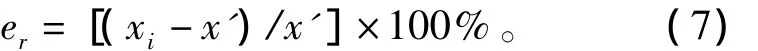

然后对两种方法的精确度进行检测,取激励信号频率和参考信号频率均为500 kHz,分别采用本文的方法和传统的ECT数据采集系统进行测试,连续测量20幅图像,当采集好数据后,分别计算它们的相对误差。

相对误差公式为

式中:xi代表第 i个测量数据,x′代表数据的平均值。

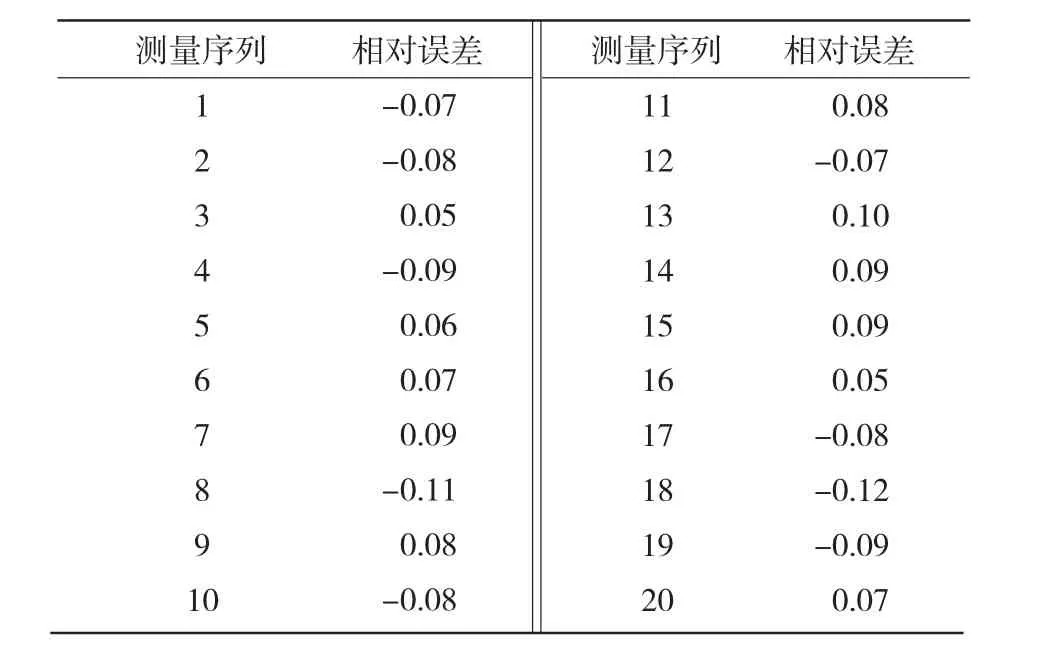

表3为采用基于FPGA改进型ECT数据采集系统采集数据的相对误差。

表3 基于FPGA的ECT采集系统采集数据相对误差Table 3 FPGA-based ECT acquisition system to collect data relative error

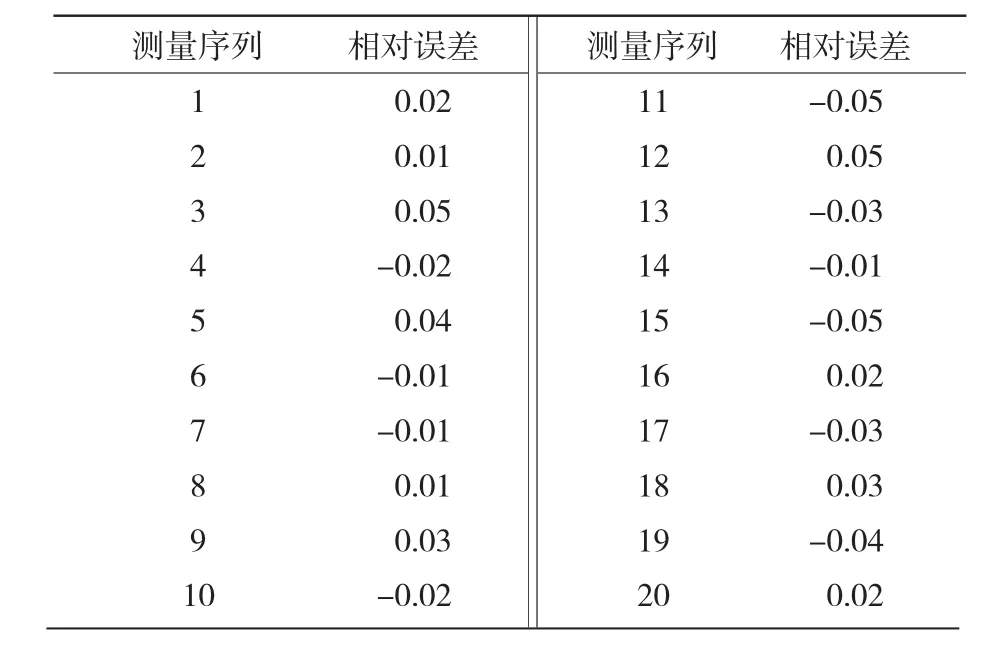

表4为传统ECT数据采集系统采集数据的相对误差。

表4 传统ECT采集系统采集数据相对误差Table 4 Relative error of the traditional ECT acquisition system to collect data

由表3和表4数据可知,由于采用数字信号发生装置,并且由FPGA控制传感器基板电路电子开关的切换,基于FPGA的ECT数据采集系统所采集的数据相对误差要远小于传统ECT数据采集系统采集的数据相对误差,这说明基于FPGA的ECT数据采集系统采集数据的精确度要高于传统ECT数据采集系统。

4 结论

在ECT数据采集系统中,传统的模拟解调方法无法解决模拟器件的电压漂移、噪声漂移和温度漂移等问题,低通滤波器的稳定时间也限制了数据采集的速度。采用基于FPGA的ECT数据采集系统可以有效地对输出信号幅值与频率进行调整,通过FPGA来控制电容传感器极板切换电路,在节约空间的同时降低系统组件成本,并且通过数字解调可以减少低通滤波等环节时间开销。由于MAC工作频率高于ADC采样频率,在A/D转换完成之后的下一个周期就可得到解调结果,提高了数据采集的速度和精确度。在实际的工业环境中,将FPGA引入到ECT数据采集系统,依据现场条件,FPGA的实际性能可能会有所改变,如何改进FPGA稳定性是提高数据采集效率的关键。

[1] 赵玉磊,郭宝龙,闫允一.电容层析成像技术的研究进展与分析[J].仪器仪表学报,2012,(33)8:1909-1920.

ZHAO Yulei,GUO Baolong,YAN Yunyi.Latest development and analysis of electrical capacitance tomography technology[J].Chinese Journal of Scientific Instrument,2012,(33)8:1909 -1920.

[2] 周云龙,衣得武,高云鹏.用于气液两相流流型识别的ECT传感器的优化设计[J].电机与控制学报,2011,(15)6:62-66.

ZHOU Yunlong,YI Dewu,GAO Yunpeng.Optimal design of ECT sensor for gas- liquid two - phase flow pattern identification[J].Electric Machines and Control,2011,(15)6:62 -66.

[3] 王莉莉,陈宇,陈德运,等.基于改进信赖域的电容层析成像图像重建算法[J].仪器仪表学报,2010,(31)5:1076 -1081.

WANG Lili,CHENyu,CHEN Deyun,et al.An improve trust region image reconstruction algorithm for electrical capacitance tomography system[J].Chinese Journal of Scientific Instrument,2010,(31)5:1076-1081.

[4] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,(32)3:714 -727.

YANG Haigang,SUN Jiabin,WANG Wei.An overview to FPGA device design technologies[J].Journal of Electronics & Information Technology,2010,(32)3:714 -727.

[5] 雷元武,窦勇,郭松.基于FPGA的高精度科学计算加速器研究[J].计算机学报,2012,(35)1:112-122.

LEI Yuanwu,DOU Yong,GUO Song.High precision scientific computation accumulator on FPGA[J].Chinese Journal of Computers,2012,(35)1:112 -122.

[6] 邓耀华,吴黎明,张力锴,等.基于FPGA的双DDS任意波发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,30(11):2255-2261.

DENG Yaohua,WU Liming,ZHANG Likai.Design of dual DDS arbitrary wave generator based on FPGA and denoising of spur noise[J].Chinese Journal of Scientific Instrument,2009,30(11):2255-2261.

[7] KJRSGAARD-RASMUSSEN J,MEYER K E.Inside-out electrical capacitance tomography[J].Flow Measurement and Instrumentation,2011,22(2):104 -109.

[8] OLMOS A M,CARVAIAL M A,MORALES D P.Development of an electrical capacitance tomography system using four rotating electrodes[J].Sensors and Actuators A:Physical,2008,148(2):366-375.

[9] 李兰英,高明,陈德运.一种电容层析成像系统多电极激励方法[J].电机与控制学报,2011,(15)9:99-104.

LI Lanying,GAO Ming,CHEN Deyun.A novel multiple-electrodes excitation method for electrical capacitance tomography system[J].Electric Machines and Control,2011,(15)9:99 -104.

[10] 李楠.相邻电容传感器设计及ECT技术研究[D].西安:西安电子科技大学,2010.

[11] MOHAMAD E J,MARWAH O M F,RAHIM R A,et al.Electronic design for portable electrical capacitance sensor:A multiphase flow measurement[C].4th Int.Con.on Mecaha.,2011:1-8.

[12] YANG W Q,PENG L H.Image reconstruction algorithms for electrical capacitance tomography[J].Measurement Science and Technology,2003,14(1):1 -13.