非接触式测速系统的FPGA开发

李 玲,李洋涛

(1.同济大学铁道与城市轨道交通研究院,上海201804;2.河南建筑职业技术学院,郑州450007)

1 引言

DE2开发板是Altera公司针对大学教学及研究机构推出的FPGA多媒体开发平台,为用户提供了丰富的外设及多媒体特性,并具有灵活可靠的外围接口设计。Terasic公司提供的针对DE2平台的CCD摄像头模块以及彩色LCD模块,可通过接口接入DE2开发板。

利用DE2开发板上的硬件资源,通过数字图像的采集、压缩、预处理、有用信息提取、图像匹配和输出结果等一系列信息处理,研制开发了一套非接触式测速系统,包括系统构成、方案实现以及如何在FPGA中实现相关运算等等,并运用Quartus II软件对Verilog代码进行编译和调试,实现了代码的优化和处理。

2 系统构成及设计

系统设计是在Altera公司的现场可编程门阵列(FPGA)开发环境Quartus II中完成的。Quartus II软件提供完整的多平台设计环境,能够直接满足特定设计需要,为可编程芯片系统(SOPC)提供全面的设计环境。

系统构成如图1所示,图像传感器将采集到的数据通过接口传送到DE2开发板,DE2实现数字图像的压缩、保存、识别及相关运算,最后通过VGA模块显示图像效果并用DE2数码管显示计算结果。

图1 系统的构成示意图

下面对部分模块做详细介绍,并附录Verilog程序代码。

2.1 摄像头采集模块

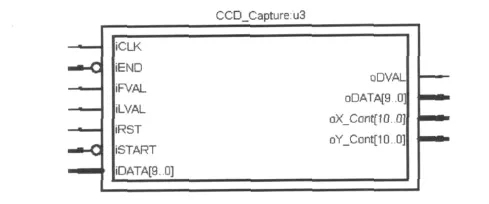

摄像头通过DE2上的GPIO接口与开发板相连接,采用片上I2C总线的控制方式,设计I2C总线CCD控制模块,通过片上时钟控制,循环发送控制信号,将摄像头采样大小设置为1280×1024,曝光时间则通过DE2上的拨码开关手动调节,显示模式设置为镜像模式,保证摄像头拍摄的内容与显示的内容同一方向,为后续处理提供了方便。模块的RTL图如图2所示。

图2 采集模块的RTL图

2.2 图像数据压缩模块

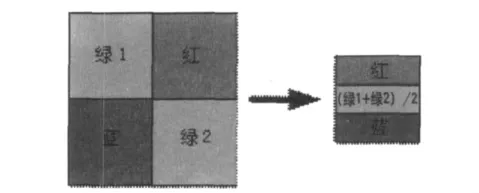

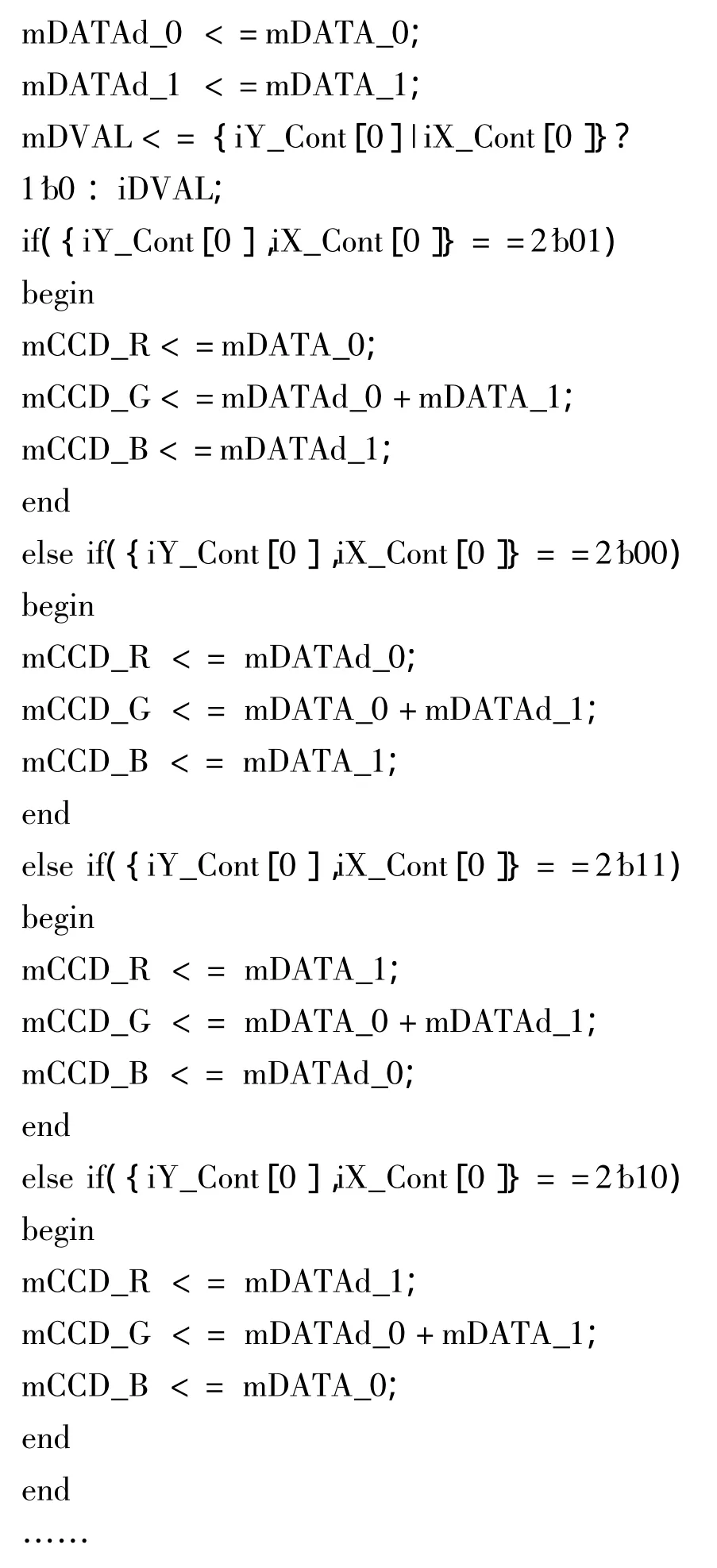

摄像头采用的是 Bayer型 CFA(Color Filter Array,颜色滤波阵列),实际显示一个图像点的颜色需要四个10bit数据来表示,一帧图像的数据为1280×1024×10bit,数据量极大。为了后续处理和显示需要,必须对数据进行压缩,并转换为RGB格式,以满足传输带宽和后续处理的需要。采用插值算法,将每四个采样象素合并为一个RGB象素点,象素值的变化如图3所示。

图3 象素值的变化图

这样经过该模块压缩处理后,RGB分量各使用10bit表示,图像的分辨率变为原来的一半,即640×512,而数据量则减少到原先的四分之一。

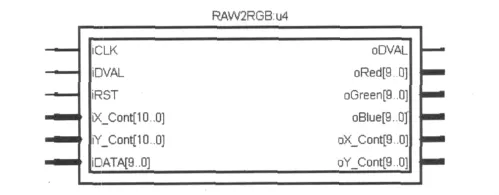

因该模块的输出数据,既需要量化后进行相关处理,又需要在VGA上显示,所以需要将数据分为两路输出到M4KRam和SDRam端口。Cyclone II的高扇出特性,保证了扇出数据的时延和电平强度都可以直接满足下一级处理的需要。最后设计的压缩模块RTL功能图如图4所示。

图4 压缩模块的RTL功能图

2.3 片上M4K存储模块

要实现相关处理需要的多次读写前后两帧数据,需要使用寄存器来存放图像的每一帧数据。由于DE2开发板上Cyclone II EP2C35的逻辑单元个数为35000个,如采用Verilog编程实现寄存器数组,如果要存放256×256×4bit的背景图像数据,所消耗的内存逻辑单元个数过多,无法满足需求。故必须利用片上嵌入的存储空间来存放所需要的背景数据。

由于DE2平台上的EP2C35仅内嵌了M4K RAM单元,所以需要通过配置级连多个M4K存储单元,来实现背景图像数据和检测区间数据的存储。EP2C35提供了104个M4K存储单元,考虑检测精度和算法耗时,需要配置一个256×256×4bit=256Kbit的背景寄存器来存放每一帧中背景区间的图像。

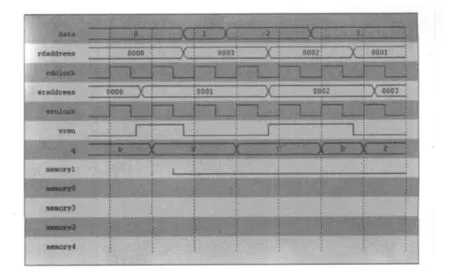

系统生成的波形图如图5所示。

图5 系统生成的波形图

完成了对256K背景寄存器的设计,只需要在设计文件中引入该.v文件,并相应在程序中使用接口,Quartus II会自动调用其内部的寄存器预设文件对程序中使用的片上内存单元进行配置。

3 实验结果

在测试中采用的背景大小为15cm×15cm,距离检测面40cm,测速的最大值可达到24.80cm/s。实际测量时可以设定参数来调整测量范围,只要前后两帧的搜索区域在速度范围内,就可以找到最大相关,测量的速度可以成倍提高。

4 结束语

总之,针对Altera公司的DE2开发板及其第三方Terasic公司提供的针对DE2平台的CCD摄像头模块,开发研究了基于FPGA的非接触式测速系统,运用Quartus II软件对Verilog代码进行编译和调试,通过试验验证了相关算法在FPGA上实现的可能。并部分实现了代码的优化和处理,给出了算法实现的具体方式,达到了速度测量的目的。Verilog编程的灵活性,使得整个测速系统可以根据实际应用调整搜索区域,具有很宽的测速范围。

[1]谢维达,王春辉,邵德荣.基于FPGA的二维相关测速方法研究[J].测控技术,2004,23(1):66 -68.

[2]张志刚.FPGA与SOPC设计教程-DE2实践[M].西安:西安电子科技大学出版社,2007.

[3]王诚,吴继华,范丽珍.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005.

[4]李洪伟.基于 Quartus II的 FPGA/CPLD设计[M].北京:电子工业出版社,2006.