一种简单快速的GPS信号捕获方法❋

陈迅,袁星星❋❋

(江苏科技大学电子信息学院,江苏镇江212003)

一种简单快速的GPS信号捕获方法❋

陈迅,袁星星❋❋

(江苏科技大学电子信息学院,江苏镇江212003)

结合一般的GPS信号捕获算法,提出了一种更为简单快速的GPS信号捕获方法。此方法在1 023个码片时间约1ms,可以完成一颗卫星在一个多普勒频移下的全码捕获检测。FPGA仿真表明,与传统的捕获方法相比,所提方法减少了资源消耗与时间消耗,同时保证了能在一个C/A码周期内获取一个多普勒频移下的C/A码相位,捕获更简单快速。

GPS信号捕获;全码捕获;串行搜索捕获;并行搜索捕获

1 引言

GPS(Global Positioning System),即全球定位系统,又称全球卫星定位系统,是20世纪70年代由美国海陆空三军联合研制的新一代卫星导航定位系统,主要用于为海、陆、空三大领域提供实时、全天候和全球性的导航服务。经过20余年的发展,卫星导航技术对于世界各国家的政治、军事、经济等方面产生了重大影响,卫星导航系统已经成为我国安全和经济不可或缺的基础信息设施,在国防建设、经济建设以及社会发展中都有应用[1]。

GPS接收机的研制是GPS技术研究的一个重要组成部分[2],GPS接收机的核心技术之一就是对信号的捕获与跟踪技术的研究,这也是影响接收机性能的主要因素。因此,掌握GPS信号捕获的核心技术,研发高性能GPS信号捕获方法,进一步提高GPS接收机的快捕特性,为我国“北斗”二代导航系统等接收机核心芯片的研发奠定基础,具有十分重大的现实意义和深远的历史意义[2]。

传统的基于软件定义的3种GPS信号捕获方法,即串行搜索捕获、并行频率空间搜索捕获和并行码相位搜索捕获耗时,电路复杂,且运算量大,资源消耗多。针对简单快速捕获这一目的,本文提出了一种新的捕获方法,利用传统串行捕获方法的思想,与传统并行捕获方法相结合,采用多个相关器同时将GPS信号与本地信号做相关运算,在一个码周期时间内得到1 023个码相关值。本文对该方法使用Verilog HDL语言进行编程和具体算法的实现,给出时序仿真图形。该方法中既省去了串行搜索捕获的繁复操作,又省去了并行搜索捕获方法中的傅里叶变换与傅里叶逆变换,不增加耗时的同时减少了功耗。

2 传统的3种GPS信号捕获方法原理

2.1 串行搜索捕获

串行搜索捕获算法包括两个不同的扫描过程:步长500 Hz、载波频率范围为1F±10 kHz(F为中频频率)的频率搜索过程,和遍历1 023个不同码相位的码相位搜索过程,搜索总共需要经过的次数为[3]

显然,搜索范围非常大。在一个C/A码周期内,即1ms的时间内,只能得到一个多普勒频移下的一个码相位的相关值,要得到所有多普勒频移下的1 023个码相关值需要的时间是

可见,耗时太长。

对串行搜索捕获的一个通道进行FPGA仿真时,存储器部分占用约11 018 b。

2.2 并行频率空间搜索捕获

与串行搜索捕获不同的是,并行频率空间搜索捕获只对1 023个不同的C/A码相位进行搜索,但需要对每一个码相位进行频域的变换。在一个C/A码周期内,只能得到一个C/A码相位的输出,对一颗卫星进行搜索捕获所需的时间最大为1 023ms,且进行傅里叶变换时资源消耗量大。

对并行频率空间搜索捕获的一个通道进行FPGA仿真时,存储器部分占用约45 056 b[4]。

2.3 并行码相位搜索捕获

与并行频率空间搜索捕获方法所不同的是,并行码相位搜索捕获对码相位采用并行方式,省去了对1 023个码片的逐一搜索及相关运算,只需改变41个可能频点即可对一颗卫星进行搜索捕获。在一个C/A码周期内,对一颗卫星进行搜索捕获所需的时间最大为41ms。虽然捕获时间有所减少,但捕获中需要进行两次傅里叶变换和一次逆傅里叶变换,资源消耗量更大。

对并行码相位搜索捕获的一个通道进行FPGA仿真时,存储器部分占用约135 168 b[4]。

3 一种简单快速的GPS信号捕获方法

3.1 方法简介

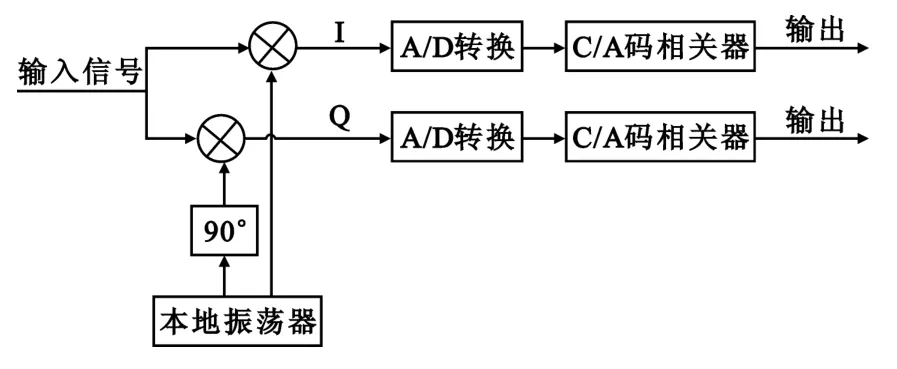

鉴于上述传统的3种GPS信号捕获方法存在的不足,本文提出了一种将串行搜索捕获与并行搜索捕获相结合的捕获方法,原理框图如图1所示。

图1 原理框图Fig.1 Block diagram of proposed acquisitionmethod

如图1所示,该方法与并行码相位搜索捕获方法的第一部分类似,接收信号与本地产生的载波相乘,产生I支路信号,与本地产生载波的90°相移信号相乘之后产生正交Q支路信号。两路信号分别经A/D转换后送入C/A码相关器进行C/A码相关运算后输出[5]。与并行码相位搜索所不同的是,该方法省去了两次傅里叶变换和一次逆傅里叶变换,在运算上大大简化,且资源消耗量小。

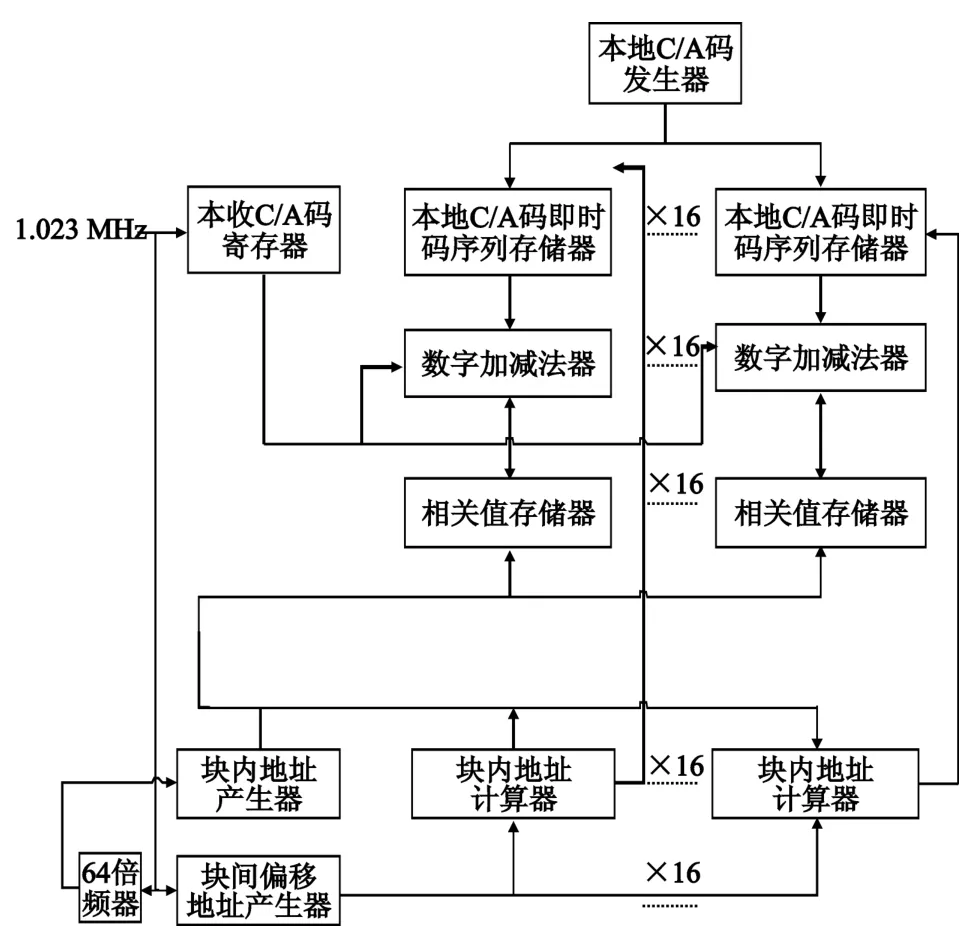

其中,C/A码相关器模块原理框图如图2所示。

图2 C/A码相关器模块原理框图Fig.2 Block diagram of C/A code correlationmodule

如图2所示,该模块包括以下几个部分:

(1)1个本地C/A码发生器,用来产生本地C/A码;

(2)1个接收C/A码寄存器,用来存储经A/D转换后的接收信号;

(3)16个本地C/A码即时码序列存储器,每个存储器有1 023个存储单元,用来存储本地C/A码的1 023个码片信号,每个存储器中的内容相同;

(4)16个数字加减法器,用来对接收信号与本地码进行相关运算;

(5)16个相关值存储器,相关值存储器都是一个双口RAM,有64个存储单元;每一个时钟脉冲下将接收到的C/A码、本地产生的C/A码数据送入数字加减法器进行相关运算后与相关值存储器中的数值累加后,将得到的数据再存回到相关值存储器;

(6)1个块内地址产生器,用来同时对每个相关值存储器的64个存储单元进行寻址;

(7)1个块间偏移地址产生器,用来产生0~1 022的偏移量;

(8)16个块内地址计算器,用来将块内地址产生器的输出和块间偏移地址产生器的输出作相关运算后对16个C/A码序列存储器的1 023个存储单元进行寻址,具体所做相关运算如下:

其中,R为块内地址计算器输出,X为块内地址计算器输出,Y为块间偏移地址产生器输出,n=0,1,2,…,15。

3.2 方法实现及步骤

流程图如图3所示。

图3 GPS信号捕获流程图Fig.3 Flow chart of GPSsignal acquisition

该方法包括以下几个步骤。

步骤一:设置多普勒频移搜索次序及产生本地C/A码。

由卫星与接收机相对运动情况,设置多普勒频移的搜索次序,多普勒频移搜索次数。搜索次数最多包括41个多普勒频点,搜索次序为i={-5,5,-4.5,4.5,…,-0.5,0.5,0,-5.5,5.5,…,-9.5,9.5,-10,10};在相对运动速度较慢的情况下,可设置21个多普勒频点,搜索次序为i={-2.5,2.5,-2,2,…,-0.5,0.5,0,-3,3,…,-4.5,4.5,-5,5},搜索步长为0.5,单位为kHz[6]。

步骤二:对GPS信号进行捕获,针对不同的多普勒频移搜索得到多组C/A码相位及多普勒频移。

具体包括以下几个步骤。

(1)将接收C/A码寄存器2中的C/A码的每个码片信号记为dx,将本地C/A码发生器产生本地C/A码同时存入16个C/A码即时码序列存储器中,每个码片信号记为Dy,16个相关值存储器记为Rz。其中,x,y=0,1,2,3,…,1 022;z=0,1,2,3,…,63。

图4为第一个相关值存储器的寻址及存储情况。

图4 第一个相关值存储器的寻址及存储情况(n=0)Fig.4 Addressing and storage of the first correlation valuememory(n=0)

对于第一个相关值存储器中的64个单元,由块内地址产生器对其进行寻址,存储情况如下。

1)在第一个时钟脉冲下存入接收C/A码寄存器的信号d0,此时,块间偏移地址产生器输出为0。

当块内地址产生器输出为0时,选中本地C/A码即时码序列存储器中的第1个码片信号D0,及第一个相关值存储器的第1个单元R0,将数据d0、D0、R0送入数字加减法器进行相关运算后再存入R0中;

当块内地址产生器输出为1时,选中本地C/A码即时码序列存储器中的第2个码片信号D1,及第一个相关值存储器的第2个单元R1,将数据d0、D1、R1送入数字加减法器进行相关运算后再存入R1中;

依此类推,当块内地址产生器输出为63时,选中本地C/A码即时码序列存储器中的第64个码片信号D63,及第一个相关值存储器的第64个单元R63,将数据d0、D63、R63送入数字加减法器进行相关运算后再存入R63中。

2)在第二个时钟脉冲下存入接收C/A码寄存器的信号d1,此时块内地址产生器输出重新归0,块间偏移地址产生器输出为1。

当块内地址产生器输出为0时,选中本地C/A码即时码序列存储器中的第2个码片信号D1,及第一个相关值存储器的第1个单元R0,将数据d1、D1、R0送入数字加减法器进行相关运算后再存入R0中;

当块内地址产生器输出为1时,选中本地C/A码即时码序列存储器中的第3个码片信号D2,及第一个相关值存储器的第2个单元R1,将数据d1、D2、R1送入数字加减法器进行相关运算后再分别存入R1中;

依此类推,当块间偏移地址产生器输出为63时,与块间偏移地址产生器输出相加为64,选中本地C/A码即时码序列存储器中的第65个码片信号D64,及第一个相关值存储器的第64个单元R63,将数据d1、D64、R63送入数字加减法器进行相关运算后再存入R63中。

3)依上类推,在第1 022个时钟脉冲下存入接收C/A码寄存器的信号d1022,此时块内地址产生器输出重新归0,块间偏移地址产生器输出为1 022。

当块内地址产生器输出为0时,选中本地C/A码即时码序列存储器中的第1 023个码片信号D1022,及第一个相关值存储器的第1个单元R0,将数据d1022、D1022、R0送入数字加减法器进行相关运算后再存入R0中;

当块内地址产生器输出为1时,选中本地C/A码即时码序列存储器中的第1个码片信号D0,及第一个相关值存储器的第2个单元R1,将数据d1022、 D0、R1送入数字加减法器进行相关运算后再存入R1中;

依此类推,当块间偏移地址产生器输出为63时,选中本地C/A码即时码序列存储器中的第63个码片信号D62,及第一个相关值存储器的第64个单元R63,将数据d1022、D62、R63送入数字加减法器进行相关运算后再存入R63中。

对于第2~16个相关值存储器,每个存储器中的64个存储单元都同样存有64个不同C/A码相位的相关值,每个相关值对应的C/A码相位为D64~

D127,D128~D191,D192~D255,D256~D319,D320~

D383,D384~D447,D448~D511,D512~D575,D576~D639,D640~D703,D704~D767,D768~D831,D832~D895,D896~D959,D960~D1022。当输入信号的一个C/A码周期结束后,将1 023个码相关值中的最大相关值记为P1,及其对应的码相位,记为P1Nj,j=1,2,3,…,1 023。

(2)获取i多普勒频移i处C/A码中不同码相位的最大相关值Pi及Pi所对应的C/A码相位PiNj,其中i=1,2,…,41。

步骤三:对每组结果进行比较分析,得到最终的C/A码相位和多普勒频移。

具体包括以下几个步骤:

首先,将41个多普勒频移下的C/A码相关值Pi进行比较,看是否能得到一个明显的峰值,如果得到明显峰值,峰值所对应的多普勒频移和码相位都已知,说明卫星被捕获,此后返回步骤一,依以上3个步骤进行对下一颗卫星的捕获;

其次,若比较分析后没有一个明显的峰值,则说明此卫星不可见。

4 仿真实现

采用Verilog HDL语言进行编程实现,输入信号使用1位二进制C/A码,输出信号为每个相关值存储器中的最大值及最大值所对应的码相位,实验图如图5所示。图5中,对15号卫星的前1 024个码片进行了该方法的相关实验,由图5可得到一个最大的C/A码相关值R12-COUT和该值所对应的码相位R12-B。

图5 Verilog HDL仿真实验图Fig.5 Verilog HDL simulation diagram

实验结果表明,每一次的搜索捕获都能得到一个最大相位值及该相位值所对应的本地码相位。C/A码频率为1.023 MHz,由1 023个码片组成,一个周期为1ms,本方法中,在一个C/A码周期内,即1 ms的时间就能得到一个多普勒频移下的最大码相关值及其对应的码相位。由此表明该方法的可行性与其优势。

对本方法搜索捕获的一个通道进行FPGA仿真时,存储器部分占用约16 368 b。

将本文中所提方法与传统的3种搜索捕获方法进行对比,结果如表1所示。

表1 几种捕获方法的比较Table 1 Comparison between several acquisitio nmethods

与传统串行搜索捕获方法相比,该方法的重复次数为41次,且每次对一个C/A码周期的1 023个码片相关运算并得到最大相关值的时间为1ms,重复41次所耗时间为41ms;与并行频率空间搜索捕获及并行码相位搜索捕获方法相比,在电路复杂度上有所改进,该方法省去了两种并行搜索捕获中的傅里叶变换与逆傅里叶变换,在一个多普勒频率下就能得到一个码相关的最大值,并且如果有需要,能够监控每个C/A码相位下的码相关值。同时,在同种仿真软件下存储器所占用资源最小。此外,在乘法器、加法器的应用上也最合理,能够很好地做到缩短时间的同时减少了资源消耗。

本文所提方法在工程中具有较高的实用性,将DSP与FPGA相结合能够实现一套完整的GPS信号捕获系统。对于GPS信号而言捕获并不是最终目的,它只是一个必不可少的重要环节,最终目的是要准确跟踪后获得GPS信号中的有效信息。因此,在该方法的仿真实现之后还需解决在此捕获方法之上能够准确有效地跟踪卫星信号,获取有效信息,这是之后要竭力解决的难题。

5 结束语

本文介绍了3种传统的GPS信号捕获方法,提出一种在原有方法基础上的一种改进方法,该方法将串行搜索捕获与并行码相位搜索捕获相结合,对该方法进行实验仿真所得结果表明该方法具有较强的实用性及准确性,同时证明了该方法既省去了传统串行搜索捕获中对1 023个码片进行依次相关运算所用的时间,也省去了传统并行码相位搜索捕获中的两次傅里叶变换与一次逆傅里叶变换所消耗的大量资源,在串行捕获与并行捕获的原理的基础上进行电路改进,实现了对GPS信号的简单快速捕获。

本文旨在提出一种新的捕获方法,重在并通过实验仿真验证该方法的可行性与准确性,及其在电路复杂度及时间、资源消耗上的优势,是对于GPS信号的捕获又一改进,这一方法的提出对于我国“北斗”二代卫星导航系统的研究也是一种促进。然而,对于不同信噪比下的捕获精度尚需进行验证及测试,所以,在此基础上如何能够在较低信噪比情况下有效捕获到卫星信号是下一步研究的方向。

[1]严岳品.基于FPGA的GPS相关器设计[D].南京:南京理工大学,2009:42-51. YAN Yue-pin.The Design on FPGA-based GPS correlator[D].Nanjing:Nanjing University of Science and Technology,2009:42-51.(in Chinese)

[2]王晓东.基于FPGA的GPS接收机16通道快捕相关器设计[D].南京:南京理工大学,2010:48-54. WANGXiao-dong.The Design on 16 channel Rapid acquisition of FPGA-based Correlator in GPSReceiver[D].Nanjing:Nanjing University of Science and Technology,2010:48-54.(in Chinese)

[3]Borre K,Akos DM,Bertelsen N,et al.A Software-Defined GPSAnd Galileo Receiver[M].Beijing:National Defense Industry Press,2009.

[4]袁帅.基于FFT的GPS信号并行捕获的研究及其FPGA实现[D].哈尔滨:哈尔滨工程大学,2008:43-45. YUAN Shuai.Study and FPGA Implementation ofGPSSignal Parallel Acquisition Based on FFTAlgorithm[D].Harbin:Harbin Engineering University,2008:43-45.(in Chinese)

[5]HuiHu,Chao Yuan.The Design on FPGA-based Correlator in GPSReceiver Using ISE[J].International Journal of Intelligent Information Technology Application,2010,3(2):92-97.

[6]北京航空航天大学.一种GPS接收机的信号捕获方法:中国,CN 101819278 A[P].2010-09-01. Beijing University of Aeronautics and Astronautics.A signal acquisitionmethod of GPS receiver:China,CN 101819278 A[P].2010-09-01.(in Chinese)

陈迅(1976—),男,江苏镇江人,2008年于上海复旦大学获博士学位,现为副教授、硕士生导师,主要研究方向为控制理论与控制工程、智能控制、自动化监测装置、嵌入式系统;

CHEN Xun was born in Zhenjiang,Jiangsu Province,in 1976.He received the Ph.D.degree from Fudan University in 2008.He is now an associate professor and also the instructor of graduate students.His research concerns control theory and engineering,intelligent control,automatedmonitoring devices,embedded systems.

袁星星(1986—),女,江苏南京人,硕士研究生,主要从事基于FPGA的GPS基带信号处理电路的研究。

YUAN Xing-xing was born in Nanjing,Jiangsu Province,in 1986.She is now a graduate student.Her research concerns FPGA-based GPSbaseband signal processing circuit.

Email:yuan1986xing@sina.com

A Sim ple and Fast M ethod for GPS Signal Acquisition

CHEN Xun,YUAN Xing-xing

(Academy of Electronics and Information,Jiangsu University of Science and Technology,Zhenjiang 212003,China)

Based on popular GPS signal acquisition methods,a simple and fastmethod is proposed.In about 1ms,themethod can complete a whole-code detection and acquisition of one satellite in a Doppler frequency shift.FPGA simulation shows in comparison with the traditional acquisitionmethods thismethod notonly reduces the consumption of resources and time,but also ensures thata Doppler frequency shift of the C/A code phase is obtained in a C/A code period.The acquisition ismore simple and fast.

GPS signal acquisition;whole-code acquisition;serial search acquisition;parallel search acquisition

TN911;TN96

A

1001-893X(2013)02-0182-06

10.3969/j.issn.1001-893x.2013.02.014

2012-06-21;

2012-10-08 Received date:2012-06-21;Revised date:2012-10-08

“北斗”二代卫星接收机双频基带芯片研制项目(BE2009121)

Foundation Item:Dual-band Baseband Chip Development of Beidou Second Generation Satellite Receiver(BE2009121)

❋❋通讯作者:yuan1986xing@sina.com Corresponding author:yuan1986xing@sina.com