一种新型超宽共模输入范围放大器设计*

余国义,张 乐,郑梅军,钟建福

(华中科技大学电子科学与技术系,武汉430074)

近年来随着物联网的推广,传感器的应用越来越广泛,对低压低功耗的信号处理系统要求也越来越高。在物联网中,同一款传感器可能分布在不同环境中,传感器输出信号的共模电平会有较大变化范围,在低电源电压下,迫切要求信号提取电路能够处理宽共模信号[1]。一般放大器在宽共模输入时,它的一些重要性能会变差,如增益、带宽、失调电压、稳定性等[2-5],而采用 BiCMOS 工艺[1,7-8]或 BCD 工艺[6,9]固然可以扩大输入共模范围,但其工艺价格比CMOS工艺要昂贵许多。

本文分析了CMOS工艺的传统的宽动态共模运放输入级的一般电路形式和其带来的问题,然后提出一种新的方法来设计宽共模输入运放。本文采用TSMC 0.13 μm CMOS工艺设计了一个新型宽共模动态范围运算放大器,通过稳定输入共模电平方法,在3.3 V电源电压时实现-1.5 V~4.8 V的共模输入范围。

1 传统的宽共模运放输入级

运算放大器的输入级一般采用差分输入结构;差分输入结构具有高的电源噪声抑制、较大的输出摆幅的优点,而且同单端的同类电路相比差动电路偏置电路的设计更加简单,而且具有更高的线性度。

CMOS工艺的传统宽共模运放输入级电路如图1所示。采用NMOS和PMOS互补作为放大管,利用NMOS可以有较高共模电平和PMOS可以有较低共模电平的特点相结合实现宽的共模输入范围[10-12]。

图1 传统的宽共模运放输入级电路

各MOS管工作状态为:

当VCM>Vdd-(VIp+Vt)时,NMOS 管 M1、M2工作,PMOS管M3、M4截止(Vt为MOS管阈值电压);

当VCM<VIn+Vt时,PMOS 管 M3、M4工作,NMOS管 M1、M2截止;

当Vdd-(VIp+Vt)>VCM>VIn+Vt时,M1、M2、M3、M4均工作。

在各状态交替时电路的总跨导Gm无法恒定,变化可能达到100%,使极点补偿不容易确定,对增益和带宽都有很大影响。为了稳定总跨导,必须非常仔细确定两个尾电流和放大管的尺寸,设计难度很大,在文献[12-14]对此类型电路有进一步说明和改进。

2 一种宽输入共模范围运放的设计

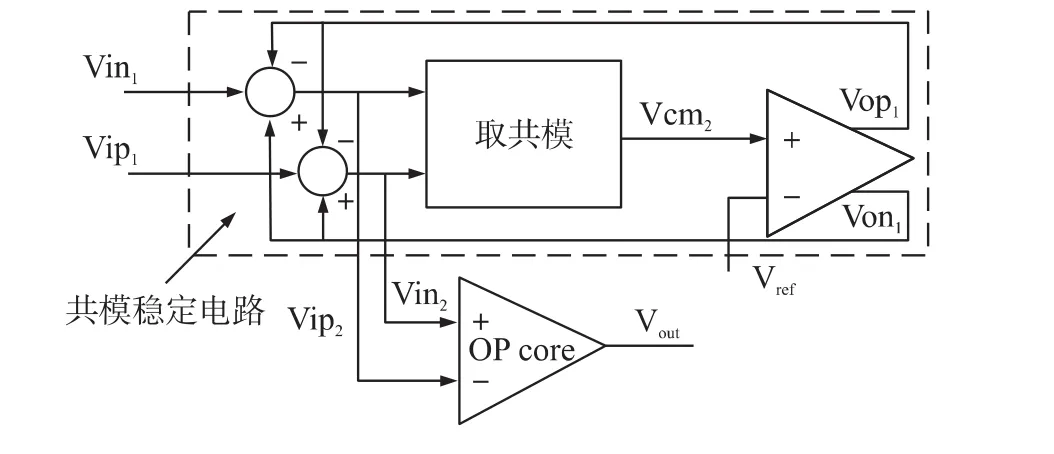

本设计通过将输入共模电平稳定到所需固定电平附近,再将稳定后信号和差分小信号提供给放大器处理来实现超宽输入共模范围。整体结构如图2所示。

图2中Vref为参考共模电平,通过反馈输入信号共模电平与Vref差值放大电压到输入端可以得到接近Vref的共模信号,而且此过程中小信号几乎不受影响(反馈网络中器件产生噪声同时加在输入端,可等效到共模电平上,因此可以忽略噪声对小信号的影响),将调整后信号输入到放大器中可以避免共模信号对运放造成的各种影响。

图2 宽共模运放系统框图

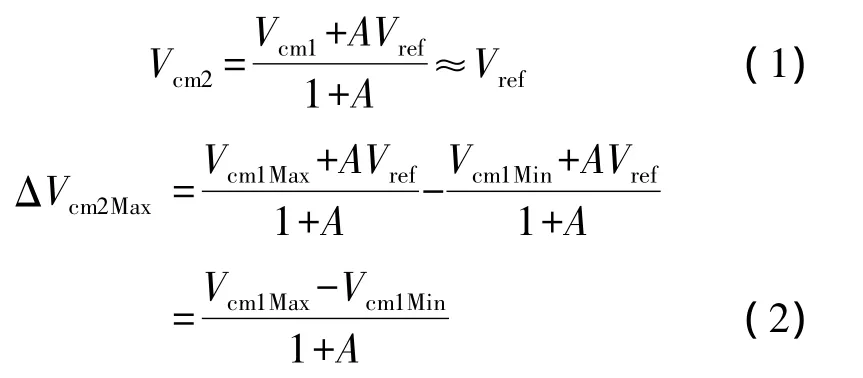

对图2进行推导可得到式(1)、式(2),式中Vcm1为输入共模电平,A为共模放大电路的双端增益,Max和Min为对应量的最大值和最小值。此二式成立是假设反馈共模电平范围可以达到足够大共模放大电路输出摆幅范围直接影响到最大共模反馈量,因此会影响到可以接受输入的共模范围,所以需要注意共模放大电路输出级的设计。由式(1)式(2)可知,此增益影响共模反馈程度,增益越大反馈补偿后信号共模电平越接近Vref(OP core的理想共模电平)。将OP core的输入信号共模范围变化限制在ΔVcm2Max之内,可以减小对OP core的共模范围设计要求。

图3 整体电路图

此宽共模运放的整体电路图如图3所示,各模块对应虚框中电路,采用3.3 V电源。为了方便设计,可以对各模块单独进行设计,保证各模块稳定和带宽匹配。电路中各模块引入的零极点均会影响整个电路的幅频响应,设计电路时,让OP core引入主极点,与电路中次极点拉开,避免次极点过多影响主极点。

根据运放同端输入相加异端输入相减规律,加/减法器可通过一个运放将求和与求差合为一体,加/减法器中的运算放大器采用两级运放,有利于极点补偿和宽的输出摆幅范围。由于加/减法器的负载电容为下级模块中MOS管的栅极电容,电容很小,在此模块仿真中发现不需要进行密勒补偿,拥有足够宽的带宽和增益。在整体电路中,我们可以发现,Vin和Vip通过两对R1、R2构成回路,为了减小此回路对输入信号的影响,应该使R1、R2得阻抗值很大,同时R1、R2高阻抗也有利于消弱共模放大电路模块的输出阻抗的影响,在此电路中R1、R2均取值100 kΩ。

共模放大电路包含取共模和放大两个功能。M16n和M16p并联得到Vin2和Vip2的共模信号,将此共模信号与Vref比较放大反馈到输入端,与Vin、Vip相加减;通过M19和M20来构成共模放大第2级,获得大的宽的输出摆幅范围和增益。在此模块中引入了密勒补偿,增加此模块的稳定性,此极点应设计较大,避免影响OP core的主极点。

运放模块的设计可采用一般设计方法,由于前面对共模信号已做过处理,此模块对共模的性能的要求可以很低,有利于其他各方面性能的提高。采用两级运放结构实现高增益和宽输出摆幅,在高增益下为了避免相位裕度过小,利用密勒补偿拉开主极点和次极点。次极点包含各模块引入的极点。

3 电路的仿真结果

采用TSMC 0.13 μm CMOS工艺库搭建出图3中具体电路,使用3.3 V的单电源,1 pF电容负载对输入共模进行扫描仿真,仿真结果如图4所示由此图知:输入共模范围可达到-1.5 V~4.6 V,其范围大于0~3.3 V。

对OP Core与整体电路的频率特性分别进行仿真,仿真结果如图5所示。

由图知,此整体电路开环直流增益为74 dB,单位增益带宽为11.4 MHz,相位裕度为74°,与 OP core的频率特性相近。与其他文献性能相比较如表1。

图4 扫描输入共模仿真图

图5 OP core与整体电路各自频率特性仿真结果

表1 本文设计和其他文献设计性能对比

由表1可以看出:在单电源设计中,本文设计不但输入共模最大值超过电源电压Vdd,而且输入共模电平低于参考地(0 V);在表中其他单电源设计中最低输入共模电平为0 V。

表1中文献[1]通过类似蝴蝶结结构的输入级电路解决了共模电平超过电源后出现的输入偏置电流过大和信号反相问题,该输入级电路还具有输出摆幅大、差模输入电压范围大、输入阻抗大频率特性好的特点。文献[6]提出的共基极输入级电路可在有效地控制输入偏置电流的情况下实现与电源电压无关的ICMR.该电路的ICMR上限仅与器件参数有关。文献[7]设计了一种浮动输出的输入信号适配器,将输入信号的电压调整到差分放大级正常工作的输入共模电压范围内,从而消除了电源电压对共模输电压的限制。文献[8]利用耐高压的BiMOS工艺,采用共基极结构,使用耐高压MOS管作为电流源,其耐高压的特性Vds可以很大(45 V)实现宽共模输入,较之普通的共基放大器能承受更高的共模电压,有更高、更稳定的增益,并且减小了系统失调。文献[9]设计一个共模输入电压估计电路和负反馈电路来控制输入端基极电流来得到一个稳定的输入环路实现宽输入共模。文献[10-11]采用比较传统的互补MOS作为输入级实现轨对轨共模输入范围,其电路结构比较简单,对输入共模范围要求相对不太高,满足自身设计要求。

在上面几种设计中除了轨对轨设计采用了CMOS工艺,其他要实现超出电源电压范围的输入共模范围均采用特殊工艺(BiMOS或BCD)并且没能实现最低输入电平低于电源低电位的性能。此外本设计虽增加设计的复杂度,但可以将OP core单独设计而对自身输入共模性能几乎可以不加考虑,有利于提高运放其他性能,增加设计的灵活性。本设计其他各方面性能几乎都达到或超过表中文献设计的性能。本文设计运放电路性能可以满足大多数应用需要。

4 结束语

本文提出了一种超过电源电压的超宽共模输入范围运算放大器设计方法,通过提取输入共模电平与参考共模电平比较放大,反馈到输入信号,使输入共模信号在OP core处趋近于参考共模电平,实现宽输入共模范围,并有利于OP core其他性能的提高。经过仿真所设计超宽输入范围运算放大器,结果表明:在Vdd=3.3 V时,输入共模电平范围可达到-1.5 V~4.6 V。此设计方法解决了一般运放输入共模范围受限和电源电压对输入共模范围限制的问题。对电路中OP core的进一步优化可以得到整体性能更优电路。

[1]陈卫洁,邹雪城,程帅,等.一种超宽共模输入范围高性能运算放大器的设计[J].微电子学与计算机,2007,24:79-81.

[2]Crain E A,Perrott M H.A 3.125 Gb/s Limit Amplifier in CMOS with 42 dB Gain and 1 μs Offset Compensation[J].IEEE,Journa of Solid-State Circuits,2006.41:443-451.

[3]Razavi B.Design of Analog CMOS Integreted Circuits[M].西安西安交通大学出版社,2003:101-103.

[4]Willy M C Sansen.Analog Design Essentials[M].北京:清华大学出版社,2008:159-160.

[5]Li T W,Jiang J G,Ye B.An Offset Cancellation CMOS VGA for GPS Receiver[C]//Integrated Circuits,ISIC.2009:441-444.

[6]江力,吴晓波,严晓浪.宽输入共模电压范围电流检测放大器的研究与设计[J].半导体学报,2007,28:1289-1294.

[7]杨宁,成立,王改,等.采用输入信号适配技术的BiCMOS运放[J].半导体技术,2009,11:1122-1126.

[8]陆佳颖,吴晓波.用于HBWLED驱动电路的宽共模电压误差放大器[J].微电子学,2009,3:352-356.

[9]Yang Y,Wu X B.Design of High-Side Current Sense Amplifier with Ultra-Wide ICMR[C]//Circuits and Systems,MWSCAS.2009:5-8.

[10]Wan I,Wan F,Abdul H A.Analysis of CMOS Differential Input to Increase ICMR of Folded Cascode Operational Amplifier[C]//IEEE,ISIEA.2010:711-715.

[11]S Rahul,A Yves,G Yves,et al.A Laser-Trimmed Rail-to-Rail Precision CMOS Operational Amplifier[J].IEEE,Transactions on Circuits and Systems,2011,58:75-79.

[12]朱莹,李丽,杨盛光,等.一种高共模抑制比恒定跨导运算放大器[J].微电子学,2007,2:242-245.

[13]东振中,邹雪城,朱全庆,等.一种恒定跨导输入放大器[J].微电子学与计算机,2002,5:37-38.

[14]路延,姚若河.一种低电压恒定跨导Rail-to-Rail的CMOS运放输入级[J].电子器件,2008,5:1479-1482.