一种基于功能复用的容错扫描链电路结构

黄正峰, 刘彦斌, 易茂祥, 梁华国

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230009)

未来高性能计算机系统的发展面临四大挑战,第1项就是可靠性问题[1]。从集成电路的自身发展来看,自始至终,高可靠性都是集成电路设计的制高点[2]。集成电路已经在银行、通信、医疗、工业控制、航空航天及军事等安全关键领域得到广泛应用,因此,集成电路的高可靠性设计成为研究的新热点[3]。由于目前80%~90% 的芯片失效都是软错误引起的[4],因此容忍软错误技术成为集成电路高可靠性设计中十分关键的环节。

按照软错误的诱因进行分类:在时序逻辑中发生的软错误统称为单事件翻转(SEU),在组合逻辑中发生的软错误统称为单事件瞬态(SET)[2]。Intel公司的芯片实际测试数据显示,SEU引起的软错误比例高达89%,SET引起的软错误比例仅占11%[5],因此,容忍软错误的高可靠性设计通常是针对SEU进行加固设计的[6]。加固设计需要用户专门定制容忍软错误的标准单元库,在逻辑综合完成后进行替换,将普通标准单元替换为加固设计的标准单元。加固设计的优点是不需要改变前端设计流程,加固设计的缺点是面积开销和性能开销较大。

内建自测试(BIST)是目前VLSI芯片最为通用的测试方法。BIST不但减少了对自动测试仪(ATE)的依赖,有效降低测试成本,而且能够进行全速测试,有效提高测试速度。BIST按照测试原理分为按扫描测试和按时钟测试2类。按时钟测试需要使用并发内建逻辑块观察器(CBILBO,简称 TMR-CBILBO)。CBILBO包括伪随机模式生成器(PRPG)和多输入特征寄存器(MISR)。PRPG在正常模式下和BIST模式下均工作。MISR在正常模式下不工作,仅在BIST模式下工作。

本文提出一种基于功能复用的容错扫描链结构,即TMR-CBILBO(Triple Modular Redundancy CBILBO,简称 TMR-CBILBO)。TMR-CBILBO在容错模式下,对传统CBILBO中的MISR进行容错功能复用,将MISR和PRPG改造成三模冗余(简称TMR)的容错电路结构。由于对MISR进行了功能复用,可以有效降低硬件开销。TMR-CBILBO在容错触发器结构的输出端插入表决器,有效针对SEU引发的软错误进行防护。

1 CBILBO相关概念

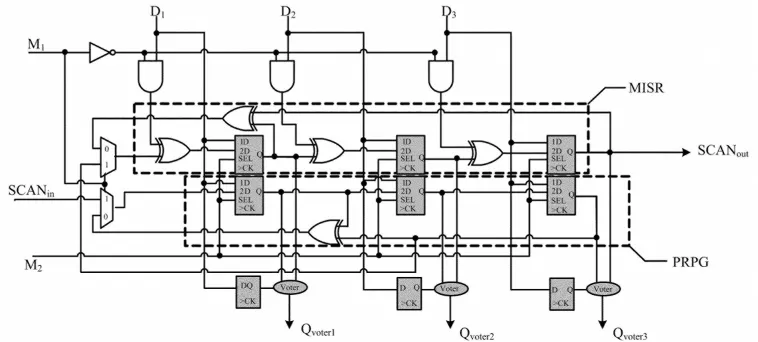

CBILBO的BIST测试结构[7]如图1所示。传统CBILBO可以在扫描模式、BIST模式和正常模式之间进行切换。在对被测电路(DUT)进行测试时,由于环绕CBILBO形成了自循环回路,为了确保故障覆盖率,CBILBO需要同时作为MISR和PRPG来使用。如果CBILBO仅作为MISR,其输出是随机向量,会降低故障覆盖率,并且MISR中的差错会引起更多的错误。图1中基于CBILBO的BIST结构中,响应分析器和模式生成器在电路结构上是独立的,可以将PRPG作为伪穷举模式生成器,针对单固定型故障产生100%的故障覆盖率。基于CBILBO的BIST结构具有在正常模式下MISR不工作的特性。本文针对该特性对MISR进行容错功能复用,将MISR和PRPG改造成三模冗余的容错结构,由于对MISR进行了容错功能复用,可以有效降低容错设计的硬件开销。

图1 CBILBO的BIST测试结构

2 三模冗余的背景知识

三模冗余技术是容错领域较为经典的容错技术,目前已经在系统级、芯核级、寄存器传输级得到广泛的应用。文献[8]在Xilinx XQVR600上实现了可配置的三模冗余容错处理器,可以支持辐射环境下的在轨升级、重配置以及修改处理器的体系结构。欧洲航天局设计实现了基于SPARC V8指令集的32位LEON-FT容错处理器[9],LEON-FT使用三模冗余寄存器进行容错。文献[10-11]在寄存器传输级采用三模冗余容错技术,但是硬件开销较大。本文提出的TMRCBILBO对MISR进行功能复用,将MISR和PRPG改造成基于三模冗余的容错结构,有效容忍软错误,并且TMR-BILBO通过功能复用,可以有效降低容错设计的硬件开销。

本文主要在寄存器传输级使用三模冗余技术。寄存器传输级三模冗余技术基于多数表决思想,如图2所示。

图2 三模冗余的原理和电路结构

逻辑值同时存储在3个同构的寄存器Q1、Q2、Q3中,输出Qvoter通过多数表决器(Voter)对数据进行选择以实现容错的目的。当Q1、Q2、Q3中任何一位寄存器发生软错误时,输出Qvoter都可以有效容错,如果Q1、Q2、Q3中有2位寄存器同时发生软错误,输出Qvoter将无法容错。但是,Q1、Q2、Q3中发生2位寄存器同时出错的概率极低。

3 容软错误的扫描链结构

本文提出的TMR-CBILBO结构如图3所示(以 3 位 TMR-CBILBO 结 构 为 例 )。TMRCBILBO通过模式控制位(M1,M2)可以在容错模式、扫描模式、BIST模式之间进行切换。TMR-CBILBO电路结构包括 MISR、PRPG和表决器(Voter)3部分。来自组合逻辑的数据同时进入MISR、PRPG和额外增加的一路寄存器,并送入表决器进行运算。

图3 TMR-CBILBO的电路结构

TMR-CBILBO的工作模式如下:

(1)容错模式(M1=1,M2=0)。将 MISR、PRPG和另外一路寄存器并联构成TMR容错结构,在输出端连接表决器,有效容忍SEU导致的软错误。

(2)扫描模式(M1=1,M2=1)。数据由SCANin串行输入,由SCANout串行输出,需要提供3种功能:① 内建自测试之前将测试向量的种子装载入PRPG;② 对MISR进行初始化;③ 内建自测试之后将MISR中的响应结果串行输出。

(3)BIST模式(M1=0,M2=1)。MISR和PRPG独立工作,MISR充当响应分析器,PRPG充当模式生成器。

与图1中传统的CBILBO结构比较,TMRCBILBO结构以MISR的容错功能复用为切入点,将MISR和PRPG改造成三模冗余的容错结构。通过功能复用,不但有效容忍SEU引发的软错误,而且大大降低了容错设计的硬件开销。容错设计必然会带来一定的硬件开销和性能开销。本文将通过实验数据来分析TMR-CBILBO结构的硬件开销和性能开销。

4 实验结果与分析

TMR-CBILBO结构在寄存器传输级构建三模冗余的容错结构,针对SEU引发的软错误进行防护,需要对TMR-CBILBO结构的可靠性、面积开销、性能开销进行定量评估。本文采用的基准电路是ISCAS-89标准电路,实验使用的工艺库是UMC 0.18μm的工艺库,综合工具是Synopsys公司的Design Compiler,电路可靠性评估工具是美国U.C.Berkeley大学开发的BFIT。

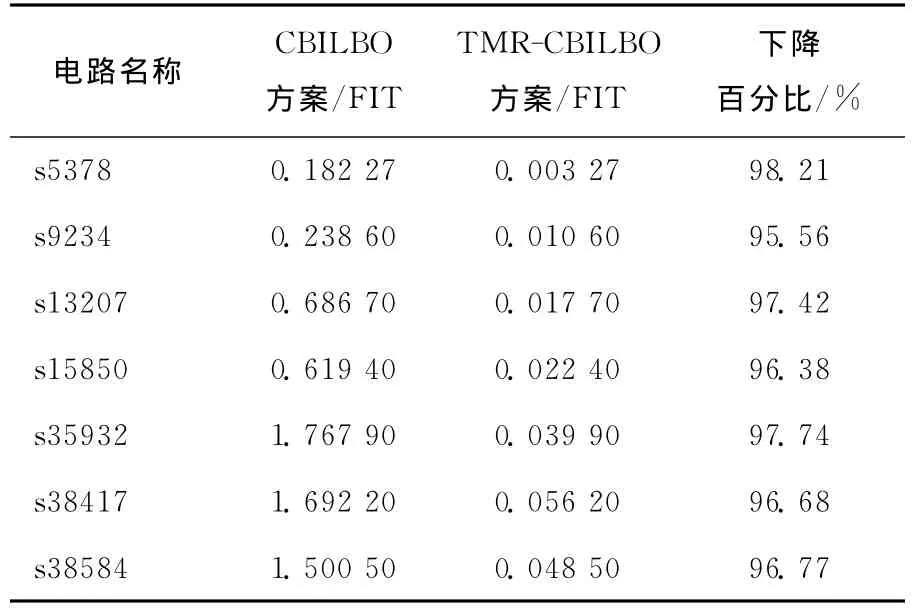

原始CBILBO方案和TMR-CBILBO方案的软错误率比较见表1所列。软错误率是衡量电路可靠性的重要指标,软错误率越低,说明电路的可靠性越高。由表1可以看出,TMR-BILBO方案将软错误率降低了95.56% ~98.21%,有效提高了电路可靠性。

表1 TMR-CBILBO方案和CBILBO方案的软错误率比较

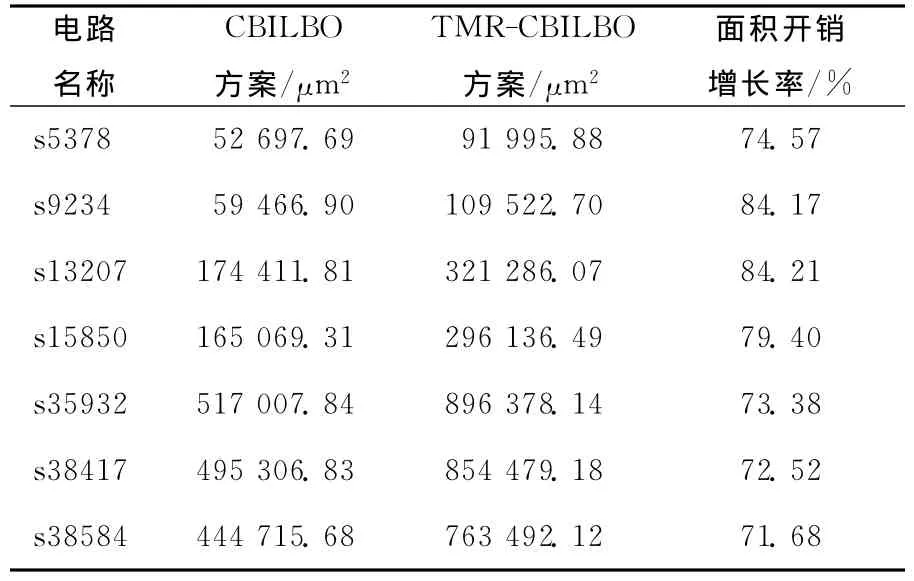

原始CBILBO方案和TMR-CBILBO方案的面积开销比较见表2所列。由表2可知,TMR-BILBO方案的面积开销增长了71.68%~84.21%。

表2 TMR-CBILBO方案与CBILBO方案的面积开销比较

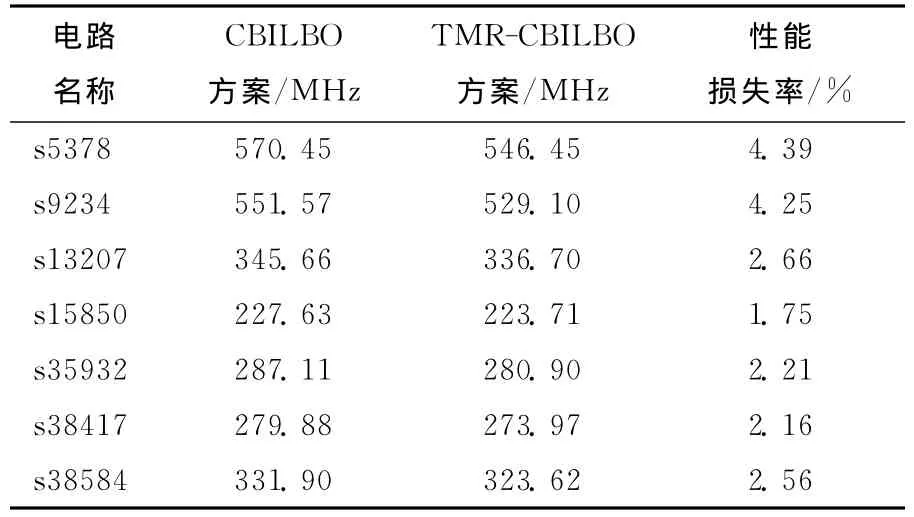

原始CBILBO方案和TMR-CBILBO方案的性能比较见表3所列。由表3可知,由于在数据通路上引入表决器,导致关键路径上的延迟增加,TMRBILBO的性能开销增加了1.75%~4.39%。

表3 TMR-CBILBO方案与CBILBO方案的主频比较

综合表1~表3可以看出,相对于传统的CBILBO方案,TMR-CBILBO方案具有较高的可靠性。TMR-CBILBO通过对MISR的容错功能复用,有效地将面积开销控制在能够接受的范围之内。

5 结束语

随着软错误成为影响集成电路可靠性的主导原因,容忍软错误的高可靠性设计成为研究的重点。本文构建低开销的TMR-CBILBO容错结构,该结构将MISR和PRPG改造成三模冗余的容错扫描链,在输出端通过表决器有效容忍SEU引发的软错误。实验结果证明,本文提出的TMR-CBILBO是一种低开销、高可靠性的容忍扫描链结构。

[1] 孙凝晖.计算机系统的技术挑战[J].中国计算机学会通讯,2011,7(1):33-38.

[2] Baumann R.Soft errors in advanced computer systems[J].IEEE Transactions on Design & Test of Computers,2005,22(3):258-266.

[3] Rao Wenjing,Yang Chengmo,Karri R,et al.Toward future systems with nanoscale devices:overcoming the reliability challenge[J].IEEE Transactions on Computer,2011,44(2):46-53.

[4] Mitra S,Zhang Ming,Waqas S,et al.Combinational logic soft error correction [C]//Proceedings of IEEE International Test Conference,Santa Clara,CA,USA,2006:1-9.

[5] Karnik T,Hazucha P.Characterization of soft errors caused by single event upsets in CMOS processes[J].IEEE Transactions on Dependable and Secure Computing,2004,1(2):128-143.

[6] Huang Zhengfeng,Liang Huaguo.A novel radiation hardened by design latch[J].Journal of Semiconductors,2009,30(3):0350071-0350074.

[7] Wang L T,Wu C W,Wen X Q.VLSI test principles and architectures:design for testability[M].Boston:Elsevier Morgan Kaufmann Publishers,2006:300-302.

[8] Hulme C A,Loomis H H,Ross A A,et al.Configurable fault-tolerant processor (CFTP)for spacecraft onboard processing [C]//Proceedings of IEEE Aerospace Conference,Big Sky,MT,USA,2004:2269-2276.

[9] Gaisler J.A portable and fault-tolerant microprocessor based on the SPARC V8architecture[C]//Proceedings of International Dependable Systems and Networks,Washington,DC,USA,2002:409-415.

[10] Mavis D G,Eaton P H.SEU and SET modeling and mitigation in deep submicron technologies [C]//Proceedings of 45th Annual IEEE International Reliability Physics Symposium,Phoenix,Arizona,USA,2007:293-305.

[11] Chen Mingjing,Orailoglu A.Improving circuit robustness with cost-effective soft-error-tolerant sequential elements[C]//Proceedings of 16th IEEE Asian Test Symposium,Beijing,China,2007:307-312.