基于FPGA的数据采集系统设计

张 博,段哲民

(西北工业大学 电子信息学院,陕西 西安 710072)

常用的数据采集方案[1]往往采用单片机或DSP(数字信号处理器)[2]作为控制器,控制ADC(模数转换器)、存储器和其他外围电路的工作。但由于单片机本身的指令周期以及处理速度的影响,难以达到多通道高速数据采集系统的要求,DSP虽然可以实现较高速的数据采集,但其速度提高的同时,也提高了系统的成本;并且单片机和DSP的各种功能要靠软件的运行来实现,执行的速度和效率较低,软件运行时间在整个采样时间中占很大的比例。而FPGA(现场可编程门阵列)在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。因此,本文以FPGA作为核心处理器件,进行了数据采集的过程。

1 数据采集系统原理

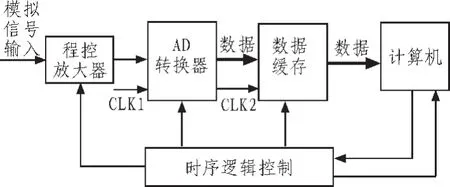

图1是一个模拟信号的数据采集系统框图。

由图可知,系统主要由以下5个部分组成:

图1 模拟信号数据采集系统框图Fig.1 Structure diagram of the analog signal data acquisition system

第1部分是放大器电路。程控放大器的作用是将传感器产生微弱的模拟信号进行放大处理。放大器把信号放大到与A/D转换器满量程电压相应的电平值,以便充分利用A/D转换器的分辨率,放大器的放大倍数可以通过设计放大电路来进行实时控制[3]。

第2部分是A/D模数转换电路。其功能是将放大后的模拟信号转换为计算机能够识别的数字信号。A/D转换器是采样通道的核心,所以A/D转换器是影响数据采集系统采样速率和精度的主要因素之一。

第3部分是数据缓存电路。A/D转换后的数据信息一般不能直接传送到计算机,所以在读入计算机或其他处理设备之前应该增加数据缓存模块,这样能有利于将数据连续的送入计算机。

第4部分是时序逻辑控制电路。它可以控制程控放大器、A/D模数转换器、数据缓存等单元,并实现与计算机的通信。

第5部分是接口电路。接口电路是数据缓存区的数据传输至计算机等设备的纽带[4]。

2 系统硬件设计

本系统主要研究对模拟信号的数据采集,根据系统的要求与功能的实现,FPGA数据采集系统的总体方案设计结构框图如图2所示。

图2 总体硬件框图Fig.2 Structure diagram of the hardware system

在模拟信号采集的过程中,模拟信号输入给A/D转换器,然后经模数转换之后将8bit的数字信号直接输出给FPGA进行处理。在FPGA中设计了数据缓冲器FIFO和数据存储器RAM以及和各级电路对应的的时钟信号,以保证能够实时的将ADC转换过来的数据进行处理。其中,液晶屏可用于显示被采集的波形,串口通信用于FPGA的在线调试与配置程序的加载,键盘用于控制操作[5]。

2.1 数据采集模块

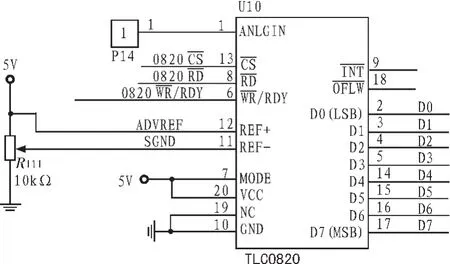

根据本系统对数据采集精度以及速度方面的要求,采用Texas Instruments改进快闪技术的先进的LinCMOS高速8位A/D转换芯片TLC0820AC来完成采集过程。它由2个4位快闪转换器,一个4位数模转换器,一个加法(误差)放大器,控制逻辑及一个结果锁定电路构成。改进的快闪技术可使低功率集成电路在整个温度范围内(0~70℃)以1.18 μs(转换率>1 M)完成8位转换。该芯片内部采样和保持电路具有100 ns采样窗,允许这些器件以高达100 mV/μs的斜升速率转换连续模拟信号而无须外部采样器件。TTL兼容的3态输出驱动器及两种工作方式允许与不同微处理器接口[6]。单一5 V电源,无须外部时钟或振荡器,最大功耗75 mV,两种工作方式可选。具有差分基准输入,数据转化及存取时间为2.5个时钟周期(MCU晶振选用12 M),最高采样率20 M。其工作方式连接图如图3所示。

图3 ADC电路设计Fig.3 ADC circuit design

2.2 数据处理模块

FPGA在高速数据采集处理方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。因此我们选择使用FPGA来进行数据的处理与控制。市场上FPGA的型号与类型非常多,根据本系统的要求,我们这里选择Xilinx公司生产的Spartan-3系列XC3S400型号的芯片[7]。Spartan-3系列是基于Virtex-II FPGA构架,采用90 nm技术,8层金属工艺,系统门数超过500万,内嵌了硬核乘法器和数字时钟管理模块。从结构上看,Spartan-3系列将逻辑、存储器、数学运算、数字处理器、I/O以及系统管理资源完美地集合在一起,使之有更高层次、更广泛的应用[8]。其主要特性为:采用90 nm工艺,密度高达74880逻辑单元;最高系统时钟为 340 MHz;具有 18×18的专用乘法器;核电压为 1.2 V,端口电压为3.3 V、2.5 V、1.2 V,支持24种I/O标准;高达520 kB的分布式RAM和18 972 kB的块RAM;有片上时钟管理模块(DCM);具有嵌入式XtremeDSP功能,每秒可执行3 300亿次乘加。

2.3 输出模块

输出模块主要负责利用液晶显示器显示采集到的数据以便进入后续的处理,因此,需要连接有显示模块。液晶显示屏常常采用12864,本系统选用了HS12864_15系列中文图形液晶模块,文字图形可混合显示且带有字库,其特征主要由其控制器ST7920决定,ST7920同时作为控制器和驱动器,它可提供33路com输出和64路seg输出。在驱动器ST7921的配合下,最多可以驱动256×32点阵液晶。

3 系统软件设计

3.1 总体方案设计

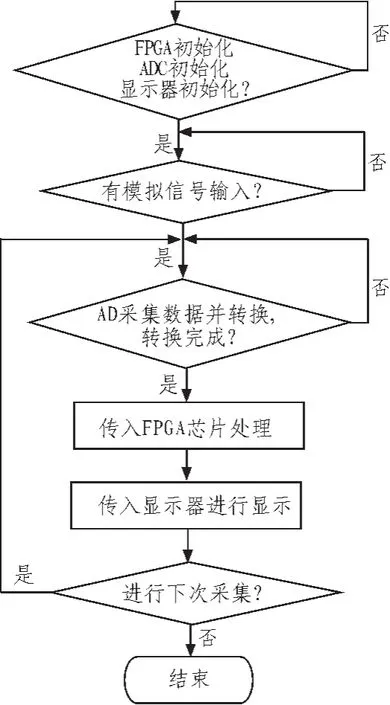

FPGA数据采集系统的软件总体方案设计流程图如图4所示。当FPGA、ADC以及12864显示器初始化完毕之后,判断是否有模拟信号输入到ADC器件中,如果没有,则等待信号的输入;如果有,则ADC开始采集数据并转换。转换完成之后,送到FPGA芯片进行数据处理。然后,传送到12864显示器中进行波形的显示。最后,再次判断有无信号输入到ADC中,如果有,则继续进行下次的采集流程;如果没有,则结束程序。

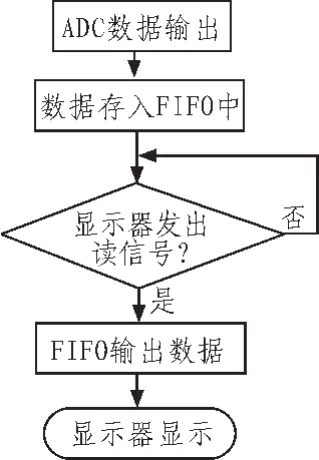

3.2 FIFO缓存设计

由于A/D转换器、FPGA以及12864显示器之间处理数据的速度不同,为了消除不必要的数据丢失与毛刺现象或者重复读取,可以将处理后的数据暂时存入FIFO中。FIFO是一个先入先出的堆栈,利用FPGA内部强大的寄存器功能,设计了一个FIFO的数据缓冲器。

如图5所示,A/D转换器将转换好的数据存入FIFO缓存中,FPGA检测显示器12864有无读信号,如果有读信号,则FIFO输出信号给显示器;如果没有,则数据继续存储在FIFO中,等待被取走。

图4 总体方案设计流程图Fig.4 Flow chart of the software design

图5 FIFO缓存设计流程图Fig.5 Flow chart of the FIFO cache design

4 结束语

基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。因此,本文研究并开发了一个基于FPGA的数据采集系统。本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

[1]孙航.Xilinx可编程逻辑器件的高级应用与设计技巧[M].北京:电子工业出版社,2004.

[2]杨颂华,孙万蓉,冯毛官,等.数字电子技术基础[M].西安:西安电子科技大学出版社,2000.

[3]史林,赵树杰.数字信号处理[M].北京:科学出版社,2007.

[4]黄志强.Xilinx可编程逻辑器件的应用与设计[M].北京:机械工业出版社,2007.

[5]杜慧敏,李宥谋,赵全良.基于Verilog的FPGA设计基础[M].西安:西安电子科技大学出版社,2006.

[6]张义,陈敌北,周金圣.例说Protel 2004[M].北京:人民邮电出版社,2006.

[7]褚振勇,齐亮,田红心,等.FPGA设计及应用[M].2版.西安:西安电子科技大学出版社,2006.

[8]Wayne W.基于FPGA的系统设计[M].英文版.北京:机械工业出版社,2005.