一种基于FPGA的并入并检AOS帧同步检测方法

潘成胜,韩 睿,刘春玲

(大连大学辽宁省高校通信与信号处理重点实验室,辽宁大连 116622)

随着航天技术的不断发展,航天器在整个空间链路之间传输的数据类型越来越复杂,数传速率越来越高。AOS(高级在轨系统)是CCSDS(空间数据系统咨询委员会)提出的一种数据通信和传输体制,它满足了高速率、大容量的数据处理和传输要求[1]。

帧同步技术是实现大容量数据传输的关键技术之一,该技术主要采用在接收端重新定位识别发送端发送的特定码组来解决帧的界限问题,是接收端后续数据处理的前提和基础,直接影响着通信系统的性能[2]。

传统的帧同步检测,数据输入和处理方式都是串行的[3-4],但某些情况下,帧同步检测能力受限:一是高速串行码流的帧同步检测,采用串检方法对芯片处理速度提出较高要求;二是在某些数字系统中需对并行码流进行帧同步检测,需要进行并串转换后才能采用串检方法,方法繁琐且处理时延提高。文献[5]解决了同步状态判断时间过短的问题,但该方法针对串行码流且会带来帧同步码的相位变化。文献[6]解决了高速数据吞吐率与芯片处理速度之间的矛盾,但该方法针对串行码流且使用的芯片资源较多。因此,本文提出一种基于FPGA的并入并检AOS帧同步检测方法,并对其性能进行了仿真分析与测试,结果表明该方法实现了高速串行码流或并行码流的同步搜索,在处理时钟频率、误锁概率、平均同步时间和芯片资源使用方面的性能优于串行检测。

1 AOS帧同步检测过程

AOS帧同步检测过程分为以下4种状态,即搜索态、校核态、同步态和失步态,如图1所示。数据接收的起始时刻或失步时刻,需进入搜索态。当检测到一组ASM(帧同步码)后,随即进入校核态。在校核态中,为降低虚假同步,若连续检测到ASM的次数等于后方保护时间a时,则进入同步态,否则重新回到搜索态,重复上述过程。同步态下,若在规定的字节数内仍能连续检测到ASM,则一直保持同步态。此时,输出去掉ASM的数据,并给出帧同步指示信号。失步态中,若连续未检测到ASM的次数等于前方保护时间b时,则进入搜索态,否则当检测到ASM时,重新回到同步态。

图1 帧同步检测过程状态图

衡量AOS帧同步系统的性能指标有很多,本文主要从漏检概率、误锁概率、平均同步时间和平均同步保持时间等指标考虑[2]。

帧同步系统漏检有误码的ASM称为漏检概率PL,记为

式中:J为误码容限;i为比特数;为M中取i的组合数;M为ASM的长度;Pe为信道误码率。

帧同步系统错误地识别一帧的开始称为虚警概率PA,记为

帧同步系统在a帧内错误的进入同步态称为误锁概率 Pws,记为

式中:L为帧长;a为后方保护时间。

帧同步系统开始工作到进入同步状态所经历的时间称为平均同步时间Tw,忽略漏检概率和虚警概率[7],记为

式中:CP为帧同步检测处理时钟。

帧同步系统从进入同步态到失步态所经历的时间称为平均同步保持时间,记为

式中:b为前方保护时间。

2 并行帧同步码检测器的设计

2.1 并入并检AOS帧同步检测方法

传统的帧同步码检测是把接收到的串行码流逐位送入串行移位寄存器,其中,移位寄存器的级数与给定的帧同步码组的长度相等,当移位寄存器内存储的码组X与要检测的帧同步码组Y相等时,即认为检测到一个帧同步码组[3]。

AOS协议中规定的ASM与交织深度有关,以ASM字节数N为例,并行帧同步码检测器需要N+1级并入并出移位寄存器。其目的在于允许待检并行码流有一个字节的滑动,这样无须考虑数据串并转换的开始,均可正确检出ASM,调整数据输出。并行码流按时钟节拍逐字节地送入并行帧同步码检测器,与此同时,在该时钟频率下,从存储字节的高位依次滑动取出各路待检ASM。每一路待检ASM都与给定的ASM按位进行异或运算。运算后的结果累加求和,若小于预先设置的误码容错范围,即判定为一个有效的ASM。最后,将所有帧同步检测的结果进行或运算,得到最终的同步状态。并行帧同步检测的原理框图如图2所示。

图2 并入并检帧同步检测的原理框图

2.2 设计方案

FPGA实现并行帧同步码检测的顶层原理图如图3所示。该系统是由PLL模块,帧同步码检测器,帧同步码计数控制器,前、后方保护计数器,帧同步计数器,数据RAM控制器,数据输出控制器和双RAM组成。

图3 并行帧同步码检测的顶层原理图

帧同步码检测器检测数据中的ASM,若该ASM在误码容限范围内,则向帧同步码计数控制器输出已检测到ASM的使能信号。帧同步码计数控制器接收已检测到ASM的使能信号,将帧同步的状态分成前方保护时间、后方保护时间和帧同步时间,分别送入与之相连接的计数器,数据输出控制器根据上述计数器的不同数值来控制帧同步码检测后的数据输出和帧同步状态的使能输出。整个处理过程,采用双RAM进行数据的存储。

3 仿真验证与分析

并行帧同步检测的功能验证在ISE 12.2和Modelsim SE6.5的环境下完成,验证所采用的芯片是Xilinx Virtex-5系列的XC5VSX50T。实验测试在光纤系统中完成,其中光纤传输的码速率为1.25 Gbit/s,物理层8B/10B解码后的8 bit并行数据时钟为125 MHz,FPGA芯片处理时钟的最小值为125 MHz。

3.1 性能仿真

3.1.1 检测速率

针对并行码流,设其字节宽度为P(单位bit),那么采用并入并检方法,其处理时钟频率是传统方法的1/P。针对串行码流,需在并行帧同步码检测器的前端增加串并转换,这样芯片只在串并转换部分采用高速时钟,剩余部分均采用低速时钟,降低芯片的性能要求。

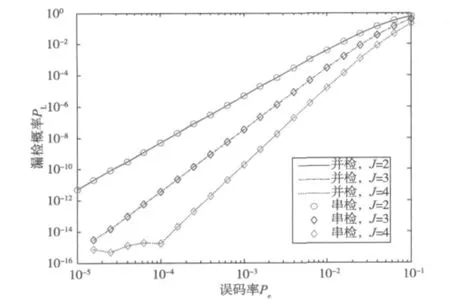

3.1.2 漏检概率

仿真参数设置如下:M=32 bit;误码率Pe的范围是10-5~10-1;误码容限J的范围是2~4;字节宽度P=8 bit;帧同步检测方式为并检和串检,仿真结果如图4所示。从图中分析可得,漏检概率随误码率的增加而增加,随误码容限的增加而降低。在不同帧同步检测方式下,误码率与漏检概率的关系曲线重合,说明二者性能一致。

图4 不同误码率下串检和并检的漏检概率

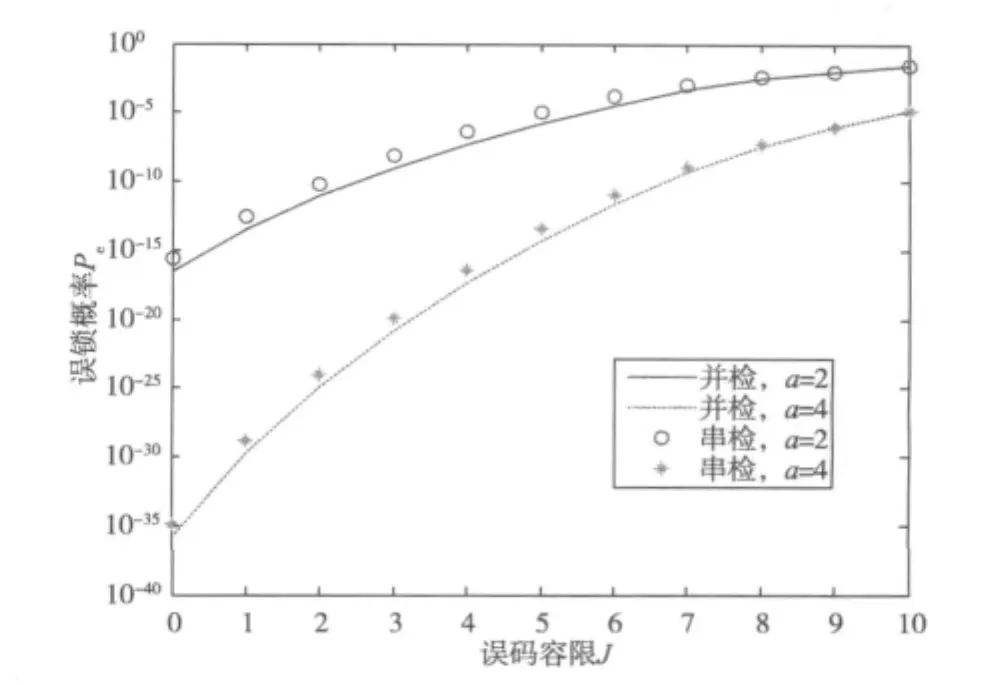

3.1.3 误锁概率

仿真参数设置如下:M=32 bit;帧长L=1 024 byte;误码容限J的范围是0~10;误码率Pe的范围是10-5~10-1;后方保护时间a的取值1~6;字节宽度P=8 bit;帧同步检测方式为并检和串检。仿真结果只给出a=2和a=4两种情况,如图5所示。从图中分析可得,误锁概率随误码容限的增加而增加,随后方保护时间的增加而减小。在J=2,a=2时,并行检测的误锁概率Pws=7.766 9×10-12,而串行检测的误锁概率Pws=6.212 2×10-11。说明在相同误码容限和后方保护时间的前提下,并检方式比串检方式的误锁概率小。

图5 不同误码容限下串检和并检的误锁概率

3.1.4 平均同步时间

仿真参数设置如下:M=32 bit;后方保护时间a的范围是1~2,L=1 024 byte;字节宽度为P=8 bit;帧同步检测方式为并检和串检,仿真结果如图6所示。从图6分析可得,平均同步时间随CP的增加而减小,随后方保护时间的增加而增加。在a=2时,CP=200 MHz,并行检测的平均同步时间Tw=76.8 μs,而串行检测的平均同步时间Tw=614.4 μs;CP=400 MHz,并行检测的平均同步时间Tw=38.4 μs,而串行检测的平均同步时间 Tw=307.2 μs。说明在相同的后方保护时间下,并检方式比串检方式的平均同步时间小。

图6 不同时钟频率下串检和并检的平均同步时间

3.1.5 平均同步保持时间

仿真参数设置如下:M=32 bit;误码容限J的范围是2~4;误码率Pe的范围是10-5~10-1;前方保护时间b的范围是1~4;字节宽度P=8 bit;帧同步检测方式为并检和串检。仿真结果只给出b=1和b=3两种情况,如图7所示。从图中分析可得,平均同步保持时间随误码率的增加而较小,随前方保护时间的增加而增加。在不同帧同步检测方式下,误码率与平均同步保持时间的关系曲线重合,说明二者性能一致。

图7 不同误码率的平均同步保持时间

上述仿真,并行检测的数据输入均为并行码流,而串行检测的数据输入均为串行码流。

3.1.6 资源使用

本文分别对帧同步码的串行检测和并行检测进行功能仿真,每种检测的输入又分为串行码流和并行码流两种。考虑的芯片资源参数包括Slice数目、LUTs、触发器、输入输出组件和全局缓冲5部分。从表1分析可得,并入并检方法虽使用过多的输入输出组件和LUTs,但在重要资源的使用上,如Slice数目、触发器和全局缓冲的使用最少。

表1 4种检测方法的资源使用情况

3.2 结果分析

在选择帧同步检测方法及系统参数时,总是希望处理时钟频率越低越好,漏检概率越小越好,误锁概率越小越好,平均同步时间越短越好,平均同步保持时间越长越好,使用芯片资源越少越好。综上分析可得:并行检测方法在漏检概率和平均同步保持时间方面的性能与串行检测一致;而在处理时钟频率、误锁概率、平均同步时间和芯片资源使用方面的性能优于串行检测。

4 小结

并入并检AOS帧同步检测方法采用待检数据并行输入,帧同步检测并行处理,解决了传统的串行检测方法的帧同步检测能力受限问题,适用于高速串行码流或并行码流的同步搜索。从性能上分析,该方法在处理时钟频率、误锁概率、平均同步时间方面优于串行检测。在芯片资源使用方面,虽使用了较多的输入输出组件,但重要资源的使用最少。

:

[1]Advanced orbiting systems,networks and data links:summary of concept,rationale,and performance[EB/OL].[2012-01-05].http://webapp1.dlib.indiana.edu/cgi-bin/virtcdlib/index.cgi/4278621/FID2/CCSDS/700X0G3.PDF.

[2]肖志东,李帅.AOS系统中的帧同步技术性能分析与仿真[J].沈阳理工大学学报,2010,29(3):20-25.

[3]王兰勋,张锁良.一种帧同步码检测方案及实现[J].河北大学学报:自然科学版,2004,24(2):180-183.

[4]范寒柏,谷力伟,赵冉.帧同步系统的FPGA设计与实现[J].电子设计工程,2009,17(8):36-38.

[5]单宝堂,王华,张健,等.一种并行帧同步设计方案的提出、设计与应用[J].电子技术应用,2005(6):61-64.

[6]陈燕.基于FPGA高速帧同步设计及性能分析[J].无线电工程,2010,40(5):25-26.

[7]孙玉.数字复接技术[M].北京:人民邮电出版社,1983.