基于EDA技术的数字频率计设计方法

范燕

(常州信息职业技术学院电子与电气工程学院 江苏常州 213164)

基于EDA技术的数字频率计设计方法

范燕

(常州信息职业技术学院电子与电气工程学院 江苏常州 213164)

介绍一种基于大规模可编程逻辑器件的频率计设计,该设计采用“自顶向下”的设计方法,先进行顶层原理图设计,再进行底层各模块VHDL程序设计,并通过波形仿真和实验箱下载验证设计结果。

频率计;VHDL;可编程逻辑器件

0 引言

随着微电子技术、大规模可编程逻辑器件、新型显示器件和计算机技术的飞速发展,电子仪器也得到了进一步的发展,如功能单一的传统测量仪器逐步向智能仪器发展。数字频率计是一种基本的测量仪器。它被广泛应用于航天、电子、测控等领域[1]。数字频率计可实现的方法,可选用的器件是多种多样的。可以运用传统模拟电路的手段如响应测频法、比较测频法测量,但是模拟信号由于其自身的特点没有数字信号稳定,因此数字电路出现后,马上就出现了数字频率计[2]。但是数字电路的方法使用大量的数字元器件,电路原理复杂,硬件调试麻烦。以EDA技术为核心的设计方法,使用的元器件少,原理电路简单,调试方便,只需要修改源程序即可。

1 EDA技术和VHDL语言的特点

EDA(电子设计自动化)代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”(Top-Down)的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终目标器件。EDA技术可以通过软件编程对目标器件的结构和工作方式进行重构,能随时对设计进行调整,具有集成度高、结构灵活、开发周期短、快速可靠性高等特点,数字设计在其中快速发展,应用这种技术可使设计过程大大简化。VHDL语言最大的特点是描述能力极强,可以覆盖逻辑设计的诸多领域和层次,并支持众多的硬件模型。其特点包括:①设计技术齐全,方法灵活,支持广泛;②系统硬件描述能力强;③VHDL语言可以与工艺无关地进行编程;④ VHDL语言标准、规范,易于共享和重用。

本设计运用Altera公司提供的一种通用电子设计软件MAX+plusII。采用原理图和VHDL语言相结合的方法设计数字系统,对所设计的数字系统进行功能仿真和时序仿真,能对设计进行逻辑优化,并将逻辑映射到器件中去,自动完成预布线,生成编程所需的熔丝图文件,通过下载电缆下载到FPGA器件来实现。FPGA器件的型号是EPF10K20TC144-4。

2 频率计工作原理

数字频率计的主要功能是测量周期信号的频率。频率是单位时间(1 s)内信号发生周期变化的次数[3]。

频率计又称为频率计数器,是一种专门对信号频率进行测量的电子测量仪器,不论频率计技术指标如何定义,其基本工作原理:当被测信号在特定时间段T内的周期个数为N时,则被测信号的频率:

其中:F为频率,单位为Hz;N为计数器计数值,计数器计数定时时间为T。

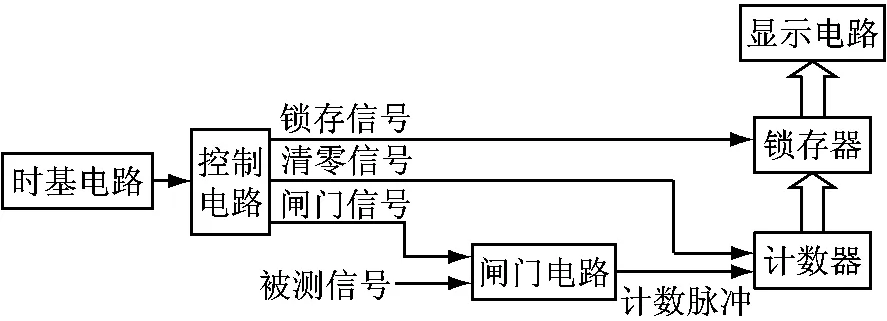

一般的数字频率计主要由4个部分构成:输入电路、闸门电路,计数显示电路和控制电路,号调理器、闸门电路,计数、译码、显示、清零、时基和逻辑控制电路等组成,原理框图如图1。

图1 简易数字式频率计方框图

3 数字频率计的设计过程

本设计是一个6位的数字频率计,测量范围为0~999 999 Hz,假设被测信号为标准的方波信号。设计采用“自顶向下”的设计方法,先进行顶层原理图设计,再进行底层各模块设计。

3.1 硬件电路设计

时钟产生电路由振荡器和分频电路构成,这部分电路实验板上已经提供。时钟的作用:①为频率计的控制电路提供基准时钟信号;②为频率计提供频率可变的被测信号。

LED数码管显示电路原理图如图2所示,FPGA直接驱动共阴极数码管,通过电阻调节数码管的电流,实现数码管的显示亮度控制,同时防止FPGA I/ O引脚的输出电流过大。

图2 LED数码管显示电路

3.2 顶层原理图设计

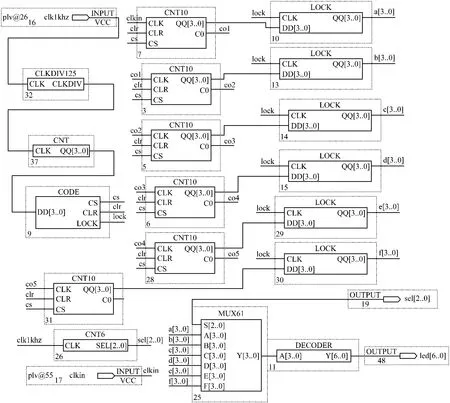

顶层原理图设计(如图3),原理图中总共有7个功能模块,每个模块功能如下。

1)分频器模块CLKDIV通过输入信号1 kHz的125分频得到输出8 Hz的信号。

2)控制器模块CODE通过CNT计数器产生三个控制信号,计数器的第一个8 Hz的信号对应输出清零信号(CLR)置高电平,第一个8 Hz的信号至第八个8 Hz的信号,闸门信号(CS)置高电平,因此脉冲宽度为1 s,第十二个8 Hz的信号,锁存信号(LOCK)置高电平。

3)计数器模块CNT10,该模块设置了计数、异步清零、使能、进位功能。异步清零是为了闸门信号开通时计数器先清零,使能就是闸门信号,进位输出是为了计数器之间的级联。

4)锁存器模块LOCK,在锁存信号的高电平期间,输出随输入变化,低电平时,输入值锁存,输出值不变。

5)多选一模块MUX61、动态扫描CNT6和显示译码器模块DECODER,是将6位频率计的数值通过动态扫描及七段译码,显示在共阴极七段数码管上。

图3 顶层原理图

3.3 底层功能模块的设计及仿真

以控制器模块CODE为例,根据CODE模块的功能,其VHDL程序编写如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity code is

port(dd:in std_logic_vector(3 downto 0);

cs,clr,lock:out std_logic);

end code;

architecture one of code is

begin

process(dd)

begin

if(dd=0)then clr<='1';

else clr<='0';

end if;

if(dd=11)then lock<='1';

else lock<='0';

end if;

if((dd>0)and(dd<9))then

cs<='1';

else cs<='0';

end if;

end process;

end one;

各模块经编译通过以后,必须进行仿真测试。其中CNT10和CODE模块的仿真结果如图4、图5所示:

图4 CNT10的波形仿真结果

图5 CODE的波形仿真结果

CNT10的波形仿真结果正确,在闸门信号CS有效,清零信号clr无效,有时钟脉冲的前提下,十进制计数信号qq开始0~9的计数。十进制计数结束产生进位信号C0。

CODE的波形仿真结果正确,当输入端dd从1计数到8时,闸门信号CS为高电平。计数到11时,锁存信号为高电平,计数到0时,清零信号为高电平。

3.4 硬件测试

各模块仿真测试正确后,经过引脚锁定,通过Byte Blaster MV并口下载电缆下载到实验箱。当输入脉冲源为 500 kHz,数码管正确显示出频率500 kHz,实验结果验证了频率计的正确性(如图6所示)。

图6 硬件测试结果

4 结束语

在介绍频率计的基本原理的基础上,阐述如何基于FPGA设计频率计,并给出完整的设计过程。此外,如果使用更高频率的FPGA芯片,频率计的量程上限可以进一步地提高[4]。

[1] 王凤英.基于FPGA的数字频率计设计与仿真[J].科技资讯,2008(33):19.

[2] 张建新.基于通用集成电路的数字频率计设计与实现[D].天津:天津大学,2008:11-12.

[3] 贾立新,王涌.电子系统设计与实践[M].北京:清华大学出版社,2011:99-107.

[4] 嵇碧波.基于FPGA数字频率计[J].电子测量技术,2005,29(4):84-85.

Design Method of Digital Frequency Meter Based on EDA Technology

FAN Yan

(School of Electronic and Electrical Engineering,Changzhou College of Information Technology,Changzhou 213164,China)

This paper describes the design of frequency meter based on large-scale programmable logic devices,which adopts the“topdown“design method.Firstly,the top-level schematic is designed,and then the VHDL program of each underlying module is designed.The design result is verified by experimental box download and Waveform simulation.

frequency meter;VHDL;PLD

book=118,ebook=118

TM 935.13

B

1672-2434(2012)03-0019-04

2012-04-10

范 燕(1981-),女,讲师,从事研究方向:EDA技术