高速SPI 接口在OSD 中的应用

施根勇,黄世震

(福州大学福建省微电子集成电路重点实验室,福州 350002)

字符叠加的全称是视频字符叠加,英文简称OSD(On Screen Display),是一种在视频信号中叠加字符信息,使得电视图像中叠加有字符或汉字图形的技术。视频字符叠加技术的应用领域非常广泛,尤其是在闭路电视安防监控中[1],视频字符叠加的作用更为明显。

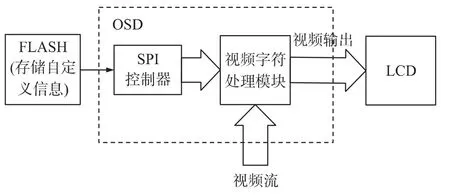

设计将SPI 串行总线接口应用到OSD 显示中,公司标识,自定义图片,时间与日期等符号信息存放在闪存(FLASH)里面,通过SPI 串行接口预加载OSD 信息,然后在LCD 上显示出来,如图1所示。

图1 高速SPI 接口在系统中的位置

由于LCD 控制器的显示格式YUV、RGB 通常是24 bit或更多,所以SPI 控制器需要很高的带宽来满足LCD 的实时显示。

1 设计任务

本文设计一个高速串行接口,连接闪存(FLASH)和屏幕显示(OSD)控制模块,在水平和垂直同步信号作用下,OSD 控制器通过高速串行接口从闪存(FLASH)中读取响应的图形和字符点阵数据,然后与输入视频叠加合成到输出到LCD 显示屏幕。

OSD 控制器如果采用320×240 的全屏显示,需要的数据传输速率约320×240×30(帧)×8(bit)≈20 Mbit/s,综合总线余量等因素的考虑,设计的SPI 串行接口速率至少应该达到30 Mbit/s。

2 串行接口比较

UART(Universal Asynchronous Receiver/Transmitter)是一种通用串行数据总线,用于异步通信,该总线双向通信,可以实现全双工传输和接收。在嵌入式设计中,UART 用来与PC 进行通信,包括监控调试器和其他器件,比如EEPROM。

I2C(Inter-Integrated Circuit)总线[2]是由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备,具有接口少,器件封装形式小等优点。

SPI(Serial Peripheral Interface)总线是Motorola公司提出的一种同步串行外设接口,主要应用在EEPROM[3],FLASH,实时时钟,AD 转换器[4],还有数字信号处理器和数字信号解码器之间。它是一种同步的高速、全双工的数据通信总线,并且在芯片的管脚上只采用四根线,节约了芯片的管数,同时为PCB 的布局上节省空间,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

I2C 连线比SPI 少,但是技术实现上更加麻烦,而且I2C 使用上拉电阻,抗干扰能力较弱,I2C 的速度也比SPI 慢。

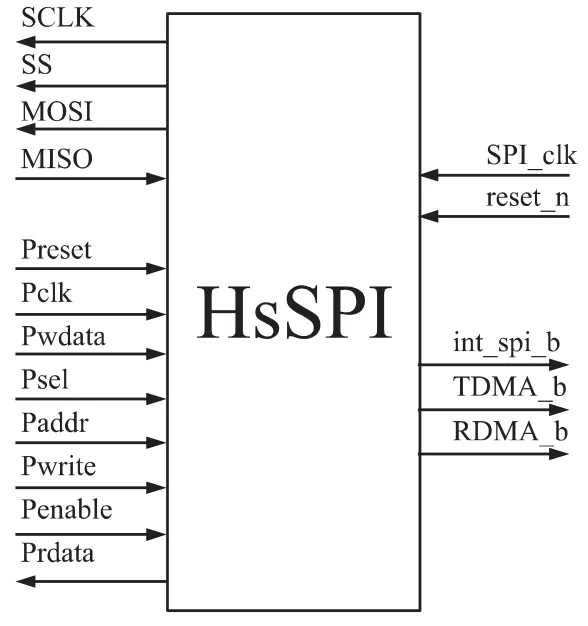

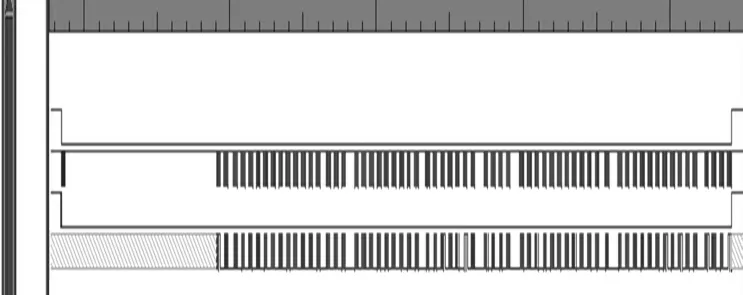

3 高速SPI模块的接口信号和时序

本设计内部接口采用AMBA 总线协议[5],增加模块的可移植性和可复用性。SPI模块挂在APB 总线上,通过APB 总线对SPI模块进行状态控制、数据读写、中断处理等操作。此外,支持DMA 操作,另外还有1 根中断请求信号线,通过配置内部寄存器来控制中断请求的输出。SPI 结构是由四条线组成[6]:串行时钟线(SCLK)、主机输出从机输入线(MOSI)、主机输入从机输出线(MISO)和从机选择线(SS)。SPI 是串行通讯协议模式,SCLK 提供时钟脉冲,MOSI、MISO 则基于此脉冲完成数据传输。上升沿到来的时候,MOSI 上的电平将被发送到从设备的寄存器中。下降沿到来的时候,MISO 上的电平将被接收到主设备的寄存器中。设计的高速SPI模块的接口信号如图2所示。

图2 高速SPI模块的接口信号图

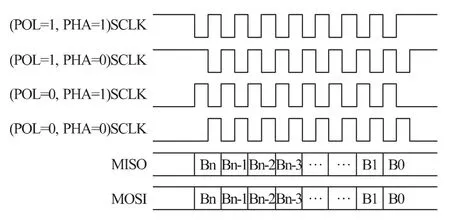

协议规定了4种传输时序,4种时序由时钟极性CPOL和时钟相位CPHA 的不同值来区分。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=“0”,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI 主模块和与之通信的外设时钟相位和极性应该一致。

图3 SPI 传输时序

4 高速SPI模块功能设计

4.1 模块划分

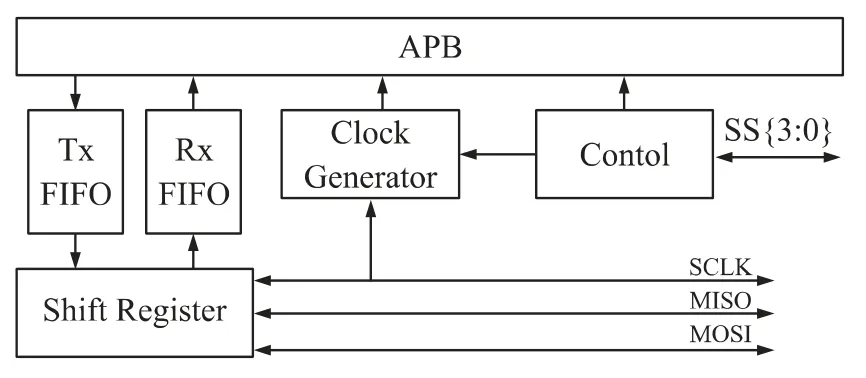

根据定义及SPI 的工作原理,将整个SPI IP 划分为6个子模块:传输控制模块、时钟分频模块、时钟同步模块、FIFO模块、APB 接口模块、SPI模式选择模块。整个SPI 控制模块的结构划分如图4所示。

图4 高速SPI模块架构

4.2 各模块设计

4.2.1 APB 接口模块

APB 接口模块的主要功能是地址译码,读取和写入内部寄存器以及FIFO 控制,当需要读取或写入寄存器的时候,将Paddr 的地址信息与寄存器的地址常量做比较,若Paddr 等于某个寄存器的地址常量,则是要对响应寄存器进行操作。当片选信号Psel 有效且写入信号Pwrite,写使能信号Penable 均有效时,将Pwdata 赋值给相应的内部寄存器。FIFO控制通过读指针和写指针来了解FIFO 内部的状态。为了支持ARM 的突发传输,对FIFO 的地址做了扩展。为了满足高速设计,SPI FLASH 中要求命令和数据的传输必须在一个SPI burst(一个CS 拉低的传输过程)里面,设计中加长了SPI burst 的最大长度(最大27个word),这样可以一次从FLASH 中尽可能的多读数据。

4.2.2 时钟分频模块

时钟分频模块将时钟spi_clk 分频,产生内部时钟信号sys_clk,设计采用了两级分频,第一级用来n分频,第二级用来2n分频。

4.2.3 时钟同步模块

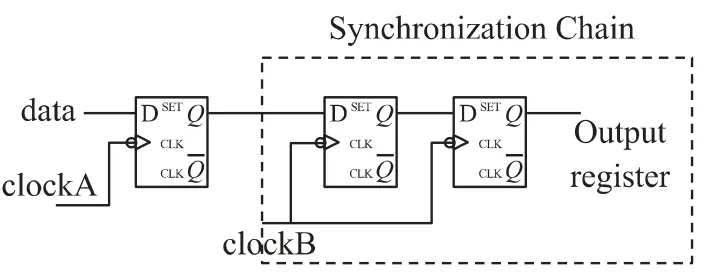

模块中有两个异步时钟域,Pclk和SPI_clk,为了尽可能减少异步信号传输中由于亚稳态引发的问题,设计采用两级同步寄存器将信号同步到新的时钟域中,如图5所示。

图5 同步寄存器链

4.2.4 FIFO模块

FIFO模块主要用作数据缓冲,以确保数据读写速度的匹配和时序的一致。由于本设计中数据吞吐量较大,为了满足高速设计,所以定义了一个64×32的TXFIFO和一个64×32 的RXFIFO。另外采用DMA 方式传输,当TXFIFO 的数据小于阈值或RXFIFO 的数据大于阈值的时候,触发DMA 请求。由DMA模块控制数据在内存和SPI 间的交换,而不需要处理器核的参与,有效提高了总线的利用率。

4.2.5 传输控制模块的设计

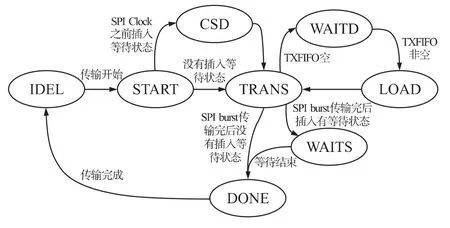

传输控制模块是SPI 实现的核心,控制整个SPI 总线的传输时序,通过计数产生数据传输使能信号以及系统需要的状态标志位,通过一个状态机来控制数据流的传输(图6)。

图6 传输控制模块状态机

初始状态为空闲状态,当CONREOLREG 寄存器中XCH 置1 的时候,开始数据传输,若传输过程中检测到TXFIFO为空,则停下来等待数据填入,当所有的数据传输完毕后,返回空闲状态。

5 高速SPI模块的仿真验证

用Verilog HDL 语言编写模块代码,为了保证RTL 代码的正确性,对IP 的功能进行全面的仿真验证,仿真包括功能验证和门级仿真,功能仿真不涉及任何时序上的延时,只是单纯地验证代码所实现的功能是否符合要求。门级仿真是布局布线后仿真,包含了精确的时延参数。

系统使用的w25x32[7]是Winbond 公司生产的总容量为32 Mbit 的SPI FLASH,一个扇区(Sector)为4 kbyte,一个块(Block)为64 kbyte,支持扇区擦除(Sector Erase),块擦除(Block Erase)和整片擦除(Chip Erase),支 持 页 写 入(Page Program,256 byte),最高时钟可达75 MHz。

为了测试设计的正确性,我们用HDL 语言编写了该SPI FLASH 的模型挂在验证平台上,编写了Testbench模块,包括产生时钟信号,控制寄存器的配置,收发的数据和产生中断等。

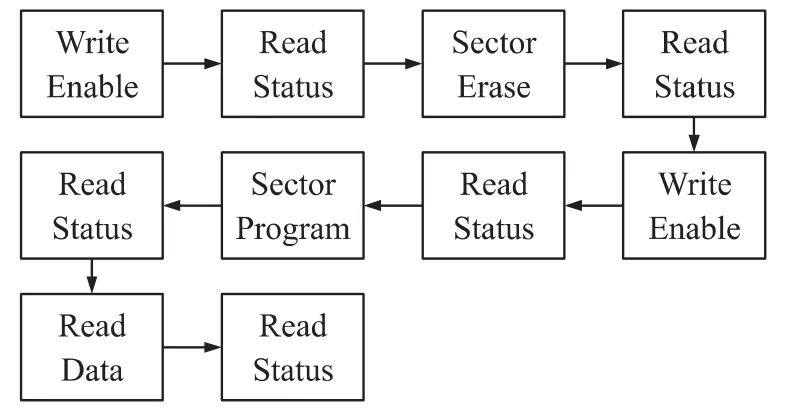

本设计测试的思路是将采用一次完整的FLASH 读写来验证SPI 控制器的功能的完整性,FLASH 要求在页写入之前必须对将要写入的扇区进行擦除,在执行页写入和擦除命令之前必须执行Write Enable,在执行命令之前,先判断FLAH 是否忙,FLASH 的读写顺序如图7所示。

图7 FLASH 读写顺序

主要的测试任务有:

(1)数据传输测试 测试启动后寄存器的初值是否正确,对FLASH 进行擦除,页写入和读测试。以及在不同的时钟分频数值下数据传输是否正确,还有不同模式下的数据发送和接收是否正确。

(2)DMA 测试,将高速SPI模块挂入系统进行DMA 测试;中断响应测试,测试各种情况下的中断输出。

①数据传输测试

图8~图11 是功能仿真的局部图。

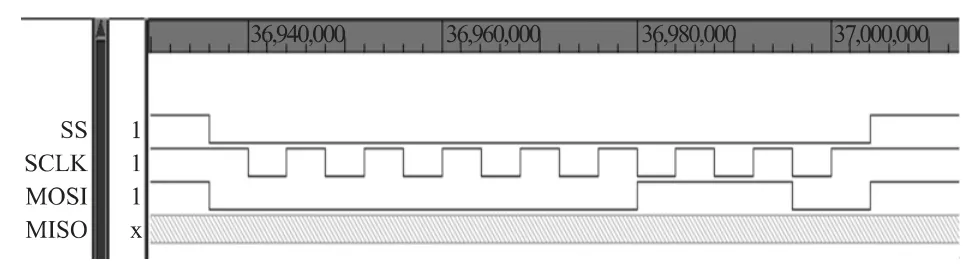

在页写入,擦除和Write Status 之前必须执行命令Write Enable,SPI 控制器将发送命令Write Enable(06h)到FLASH。

图8 高速SPI模块发送Write Enable 命令波形图

图9 高速SPI模块发送Sector Erase 命令波形图

擦除有Block Erase(D8h),Sector Erase(20h)和Chip Erase(C7h),图9 是Sector Erase 的波形图,前8 bit 传输的是命令20 h,后24 bit 传输的是地址。

图10 高速SPI模块页写入波形图

Page program 前8 bit 发送的是命令02h,然后24 bit 发送的是地址,接下来的256个byte 发送的是将要写入FLASH 的内容。

图11 高速SPI模块读数据波形图

Read data 只要发送了命令(03h)和地址后,地址会自动的跳到下一个地址,这就意味着只要发送一次命令和地址,就可以一直往下读。控制器设置的最大SPI burst 的长度为128个word。

②DMA 测试和中断响应测试

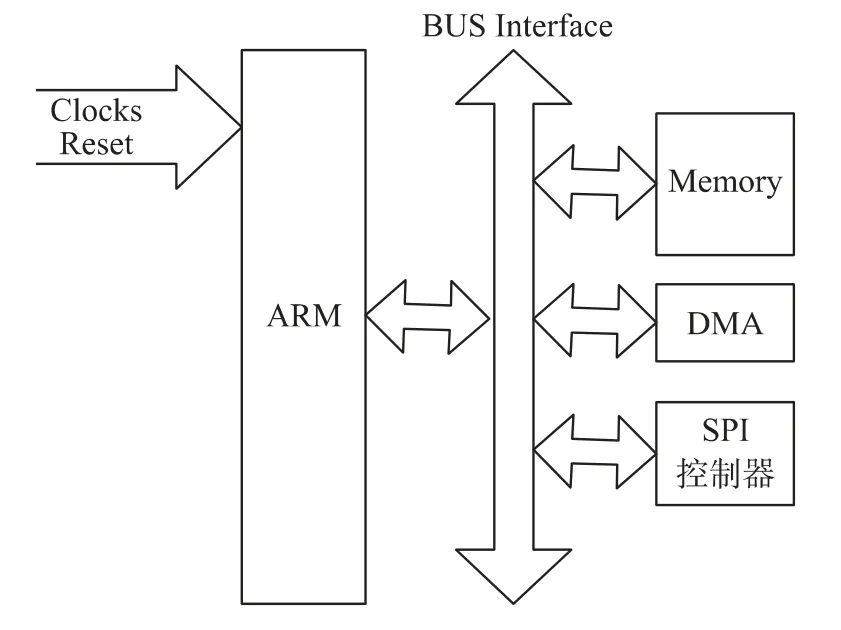

完成了高速SPI IP 的验证后,接着将高速SPI IP 与ARM11 及DMA模块进行整合,如图12,验证DMA和中断响应。

顺利通过了功能测试,利用综合工具Design Compiler 对RTL 代码进行综合,经过对脚本约束的设定,通过DC 将控制器的时序和面积进行优化。

图12 验证测试系统结构

最后采用Xilinx 公司的Virtex-5 系列[8]的XC5VLX330FF1760-1 芯片进行FPGA 验证,测试的SPI模块的传输时钟为66 MHz,测试结果表明数据传输的带宽达到了我们做OSD 的要求,最大数据传输速率可达35 Mbit/s,速度比遵循SPI 协议的同类设计得到了相当大的改观。

表1 SPI模块设计比较

6 结论

实现了高速SPI IP 核的设计和FPGA 仿真验证。本设计着重于高速传输设计,数据传输采用了简洁的并串互转结构,扩展了FIFO 的容量,一次可最大传输27个word,最大传输速率可达35 Mbit/s,在遵守SPI 协议的同类设计中是较快的了,满足了OSD 控制模块的高速要求,因此可以实现对叠加内容的动态更新,在OSD 上做非常华丽的效果。而且是基于APB 接口的设计,更加方便灵活,便于集成。

[1]张薇.大型云镜摄像机控制系统设计及实现[D].南京:南京理工大学,2007.

[2]The I2C-BUS Specification Version2.1[S].2000.7.

[3]M95M01-R,1 Mbit Serial SPI Bus EEPROM with High Speed Clock[R].2008.7.

[4]ANALOG DEVICE 应用笔记AN-877,通过SPI 与高速ADC 接口[R].2007.4.

[5]AMBA Specification Revision 2.0[S].ARM Limited,1999.

[6]SPI Block Guide V04.01[S].Freescale Semiconductor,Inc,2000.6.

[7]W225X16,W25X32,W25X64,SPI Flash 16M-BIT,32M-bit,and 64M-BIT Serial Flash Memory with 4KB Sectors and Dual Output SPI[S].Winbond,2007.12.

[8]Virtex-5 User Guide,XILINX[S].2007年9 月.

[9]张桂友,戴庆元.串行外围接口SPI 功能模块设计[J].微处理器,2009,(4):15-20.

[10]王二萍.高速可复用SPI 总线的设计与Verilog HDL 实现[D].河南大学,2007.