虚拟数字音频扫频仪的设计

周 涛 杨景常 郝明刚

(西华大学电气信息学院,四川 成都 610039)

0 引言

在电子测量中,经常涉及到对网络的阻抗特性和传输特性进行测量的问题,其中,传输特性包括增益特性、衰减特性、幅频特性和相频特性等。用于测量上述特性的仪器被称为频率特性测试仪,简称扫频仪,它为被测网络的调整、校准和故障的排除提供了极大的方便[1]。

传统的、使用较多的仪器如BT-4型扫频仪,大多是采用不同的电子元器件构成的振荡器,这种仪器存在价格高、体积大、精度低等缺陷,不便于用户实际使用。随着电子技术的飞速发展,越来越多的电子电路要求集中在音频范围内工作,所以电路的音频特性就显得非常重要。

在此,本文提出了一种简易的数字化扫频仪的设计方法,能够实现对待测网络的音频特性进行测试的功能。

1 扫频信号产生原理

直接数字频率合成(direct digital frequency synthesis,DDS)原理框图如图1所示。

图1 DDS原理框图Fig.1 Block diagram of DDS

DDS技术的工作原理介绍如下[2]。

相位累加器是由1个N位加法器和1个N位寄存器组成,其作用是对频率控制字φ进行线性累加,正弦查找表中对应的是一张函数波形查寻表。对不同的相位码址输出不同的幅度编码,相位累加器根据累加输出的序列对查找表进行寻址,得到一系列离散的幅度编码。该幅度编码经D/A转化器转化后得到对应的阶梯波,最后经低通滤波器平滑滤波后得到所需的模拟波形。相位累加器在基准时钟fclk作用下进行线性相位累加,当相位累加器加满时就会产生一次溢出。这就完成了DDS信号的一个频率周期。

输出信号的频率为:

式中:fclk为参考时钟频率,Hz;φ为频率控制字,rad;N为相位累加器的位数,bit。由式(1)可知,直接数字频率合成(DDS)的频率分辨率即最低频率为:

所以,只要N足够大,DDS就可得到很小的频率间隔。要改变DDS的输出信号的频率,只要改变频率控制字φ即可。

本设计根据上述DDS原理,利用DSP芯片通过软件编程的方式来产生扫频信号。软件实现DDS的基本思路为:相位累加器由几条语句来实现,正弦查找表采用DSP芯片内部ROM中固化的正弦表,数模转换器的功能用脉宽可变的脉冲宽度调制波与低通滤波器来实现。其中扫频信号产生的关键在于将所查到的正弦值映射成脉宽可变的脉冲宽度调制波。

2 幅频特性测试原理

系统利用DSP内部的ADC模块对EV模块产生的单频信号进行高速采样,并通过比较求最大值的方法计算出待测网络输出端的单频信号峰值。

本设计的幅频特性测试编程思路为:用ePWM中断子程序产生单频扫频信号,并通过置位标志位的方式通知主程序,主程序记录当前待测网络输出端的频率;然后启动模数转换器,并对当前待测网络输出端的信号进行高速采样,获得该频率的幅值;最后将该频率与幅值一起发送到PC机。

3 系统硬件设计

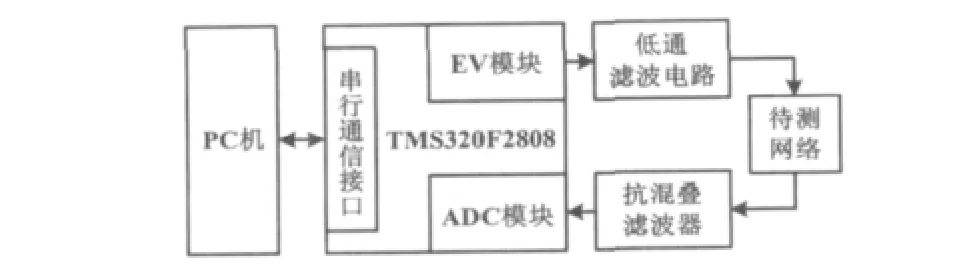

系统硬件主要包括PC机、串门通信接口模块、EV模块、ADC模块、滤波电路、待测网络等模块,其整体框图如图2所示。

图2 系统硬件框图Fig.2 Block diagram of system hardware

3.1 DSP 最小系统

系统选择DSP芯片TMS320F2808作为本设计的核心处理芯片。TMS320F2808含有丰富的片上外设资源,如 PIE、EV、ADC、串行通信接口(serial communication interface,SCI)、SPI等。本设计只涉及了其片上的EV、ADC和SCI等模块。

最小系统由DSP芯片、复位电路、JTAG调试接口和时钟电路组成[5]。复位电路采用容阻式的复位电路,其中RC回路充电时间常数为30 ms,能够确保复位成功。JTAG调试接口可以方便程序的调试和烧写。本设计的时钟采用20 MHz无源晶振,经TMS320F2808内部的锁相环倍频后获得100 MHz的CPU时钟。

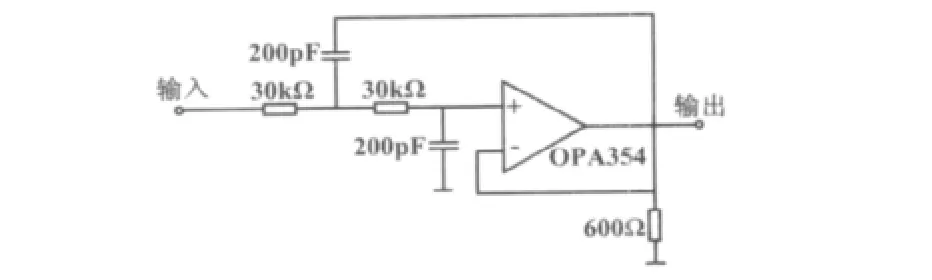

3.2 低通滤波电路

以OPA354运放芯片为核心芯片,设计了二阶有源低通滤波器[6]。该滤波电路如图3所示,其截止频率为24 kHz,具有性能稳定、增益易调整、输入阻抗高以及输出阻抗低的特点。TMS320F2808输出占空比可变的PWM信号,经该滤波电路处理后,输出幅度为0~3 V的正弦信号,即扫频信号。

图3 低通滤波电路Fig.3 Circuitry of low-pass filter

3.3 抗混叠滤波电路

抗混叠滤波电路的结构亦采用上述低通滤波电路的设计方法。该电路的截止频率是ADC采样频率的一半,可实现抗混叠的作用。待测网络的输出信号通过该电路进行抗混叠处理之后,输入到TMS320F2808的ADCINA0引脚,由ADC进行高速采样。

4 系统软件设计

系统的软件设计采用模块化设计方案,即将实现特定功能的每个子程序组成一个功能模块,最后由主程序统一调用。系统软件包含的主要功能模块包括初始化模块、主程序控制模块和中断模块。

4.1 初始化模块

初始化模块主要包括 PIE、PWM、ADC、SCI、GPIO模块的初始化。

系统初始化将CPU时钟通过TMS320F2808内部锁相环倍频后配置为100 MHz,禁止看门狗;并配置外设高速时钟为系统时钟的2分频,外设低速时钟为系统时钟的4分频,使能PWM、ADC、SCI时钟。

PIE初始化首先将12组外设中断寄存器和外设中断标志寄存器清除,然后再初始化中断向量表并使能PIE中断。

GPIO初始化将所用的GPIO口根据系统的功能要求配置为相应的功能,其中GPIO28、GPIO29配置为SCI发送和接收,GPIO0配置为EPWM1A。

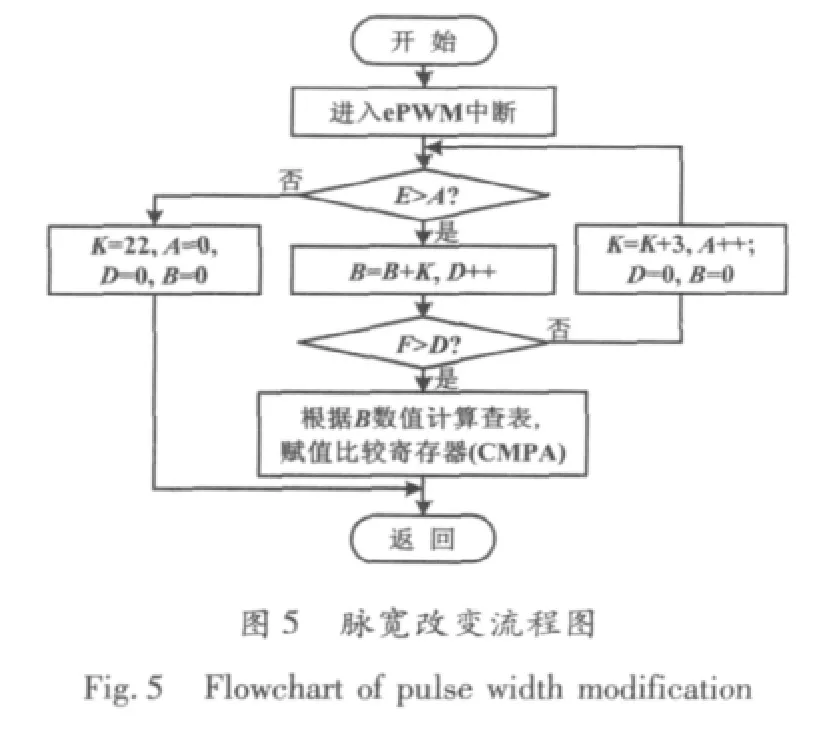

4.2 中断模块

中断模块含有ePWM中断、ADC中断和 SCI中断。ePWM中断负责产生脉宽可变的PWM波,ADC中断负责获得单频信号的幅值,SCI中断负责发送单频信号频率与幅值到PC机和接收PC机下发来的命令。系统软件总体流程图如图4所示。脉宽改变的具体程序流程如图5所示。

图5中:A为当前累计的频率点数;B为相位累加器的值;K为频率控制字;D为每种单频信号的采样点数;E为音频范围内总的频率点数;F为各单频信号的采样点数,即为相位累加器的位数。

5 测试结果

对系统的性能进行测试,本设计制作了1个双T带阻滤波器。本设计使用TDS1002示波器进行测试,示波器的频率范围为60 MHz,满足本设计的测试要求。在选取的各频率点处,首先用示波器测量该带阻滤波器的输入、输出信号的幅度值;然后计算出扫频信号通过该带阻滤波器后在各频率点处的幅度增益;最后将计算结果与PC机界面显示的结果进行比较。带阻滤波器的频率特性测试结果如表1所示。由表1所示数据可知,本设计的测量误差控制在4%以内,说明系统具有较高的测量精度,满足系统要求。

表1 带阻滤波器的频率特性测试数据Tab.1 Test data of frequency characteristics of band-stop filter

6 结束语

本文设计的扫频仪具有外围电路少、系统参数软件可调、运算速度快、精度高和结果数据可存储等特点,测试误差控制在4%以内,能够直观地测试被测网络的音频频率特性,并绘制出相应的幅频特性曲线。同时,它可以作为通用测试仪器,在电子产品开发中对音频范围内的被测网络进行幅频特性的测试,便于开发人员调整设计方案和设计参数。该设计的不足之处在于其没有实现对待测网络进行相频特性测试的功能,这将是下一步开发的重点完善之处。

[1]毛长根.低频扫频仪的设计与制作[J].微电子与基础产品,2002,28(3):37-40.

[2]毛敏,王淑仙,刘锦高.新型直接数字化合成式扫频仪的原理和研制[J].仪器仪表学报,2004,25(4):534-537.

[3]操长茂.基于DDS的频率特征测试仪[J].半导体技术,2003,28(12):44-46.

[4]陈小静.基于 DDS技术的扫频仪的设计[D].保定:河北大学,2010.

[5]孙丽明.TMS320F2812原理及C语言程序开发[M].北京:清华大学出版社,2008.

[6]康华光.电子技术基础[M].5版.北京:高等教育出版社,2006:418-422.

[7]郝俊寿,李春明.基于DSP正弦信号源的实现[J].现代电子技术,2007,249(10):158-160.

[8]程佩青.数字信号处理教程[M].3版.北京:清华大学出版社,2007.

[9]谭浩强.C语言程序设计[M].3版.北京:清华大学出版社,2005.

[10]钱能.C++程序设计教程[M].北京:清华大学出版社,1999.