用查表法实现数控振荡器的ASIC设计

欧阳雪,邹文英

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

数控振荡器是数字通讯中调制解调单元必不可少的部分,同时也是各种数字频率合成器和数字信号发生器的核心部分,具有频率分辨率高、频率变化速度快、相位可连续线性变化和生成的正/余弦信号正交特性好等特点。而且数控振荡器的相位、幅度均已数字化,可以直接进行高精度的数字调制/解调。随着数字通信技术的发展,传送的数据速率越来越高,如何得到一个可数控的高频载波信号是实现高速数字通信系统必须解决的问题。本文将介绍用查表法实现数控振荡器的ASIC设计的一种方法。

2 NCO概述

NCO(Numerical Controlled Oscillator)即数控振荡器用于产生可控的正弦波或余弦波,其实现的方法目前主要有计算法和查表法等。计算法以软件编程的方式通过实时计算产生正弦波样本,该方法耗时多且只能产生频率相对较低的正弦波,而需要产生高速的正交信号时,用此方法无法实现。因此,在实际应用中一般采用最有效、最简单的查表法,即事先根据各个NCO正弦波相位计算好相位的正弦值,并以相位角度作为地址把该相位的正弦值数据存储在表中,然后通过相位累加产生地址信息,读取当前时刻的相位值在表中对应的正弦值,构成一个幅度/相位转换电路(即波形存储器),通过该转换电路产生所需频率的正弦波。

用查表法实现NCO的性能指标取决于查表的深度和宽度,即取决于表示相位数据的位数(查表存储器地址线的位数)和表示正弦值数据的位数(查表存储器数据线的位数)。改善NCO性能最简单和最根本的方法是加大查找表的深度和宽度。目前,用查找表法实现NCO的普遍做法是用片内ROM作为查找表,由于片内资源的限制,查找表的深度和宽度一般不会很大,大大限制了NCO性能的提高,因此,设计高速、高精度的NCO时,大容量、读取速度快的ROM设计成为一大难题。采用正向全定制设计ROM模块,嵌入片内与标准单元进行布局布线,是用查表法实现数控振荡器的ASIC设计的一种好方法。基于此设计构想,笔者成功地利用0.5μm单多晶三铝的CMOS工艺设计加工出一款48位编码的高速、高精度NCO集成电路。

3 NCO的实现

3.1 结构设计

图1 NCO的结构框图

图1是数控振荡器的顶层电路结构,可以看到主要部件分为频率控制字寄存器,相位控制字寄存器、累加器、加法器、锁存器等。

3.2 设计实例

3.2.1 功能框图

该电路可以在WRN、CSN及ADDR总线的控制下,将DATA总线上的数据置入48位数据缓冲器中,在LDSTB下降沿的时候通过CLOCK将缓冲器中的数据每4位为1个单位,分12个节拍锁入锁存器中,累加器每次将最新的结果和锁存器中的数据相加,输出最高的13位结果,然后根据电路外部SIN和TWO两个控制线的状态输出相应数字格式的正余弦波。

图2 48位NCO的功能框图

3.2.2 频率控制字寄存器、相位控制寄存器、累加器和加法器的设计

频率控制字寄存器和相位控制字寄存器都是48位并行输入/并行输出寄存器,它们通过微处理器接口进行读写。频率控制字寄存器确定载波的频率,相位控制字寄存器确定载波的初始相位。48位累加器对代表频率的频率控制字进行累加运算,累加器对系统时钟进行计数,每到达输入频率控制字的值即进行累加,累加结果与代表初始相位的相位控制字通过48位加法器进行相加运算,在本电路中,取相加结果的高13位数据读取查找表的地址信息。

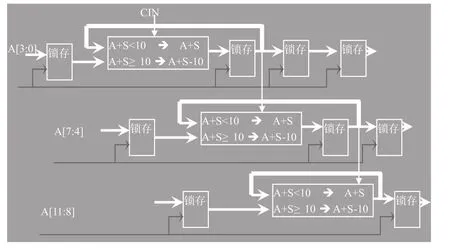

其中,累加器是决定NCO性能的一个关键模块,可以利用进位链实现快速、高效的电路结构,但是,过长的进位链会减少其他逻辑使用的布线资源;同时,也会制约整个系统速度的提高。因此,设计中采用进位链和流水线技术相结合的办法,能大幅提高系统的性能和速度。其原理结构如图3所示。

图3 采用流水线技术的累加器结构原理图

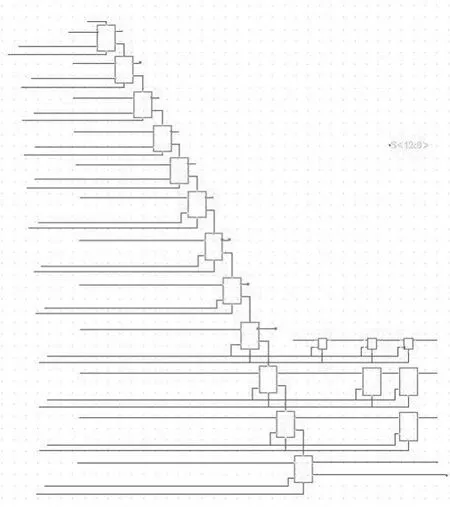

针对该电路的设计要求设计带流水线技术的48位高速并行相位累加器,每个时钟周期产生一个新的累加值,超出波形发生器最大值的累加值被溢出,并取48位数据的高13位作为波形发生器的地址信息,累加器的逻辑图如图4。

图4 电路相位累加器逻辑图

3.2.3 ROM模块设计

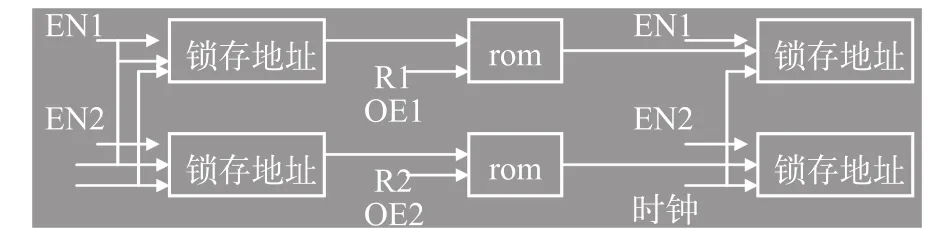

正余弦查找表的设计也是NCO电路关键的一块,本电路设计用13位≥12位(8192×12)的查找表,并采用Y对称原则进行相位简化为(4096×12)查找表,再进行正负幅度简化为(4096×11)查找表,评估X对称原则(即取四分之一象限)简化为(2048×11)查找表,采用两个相同ROM模块实现,结构如图5。

图5 简化后的ROM结构图

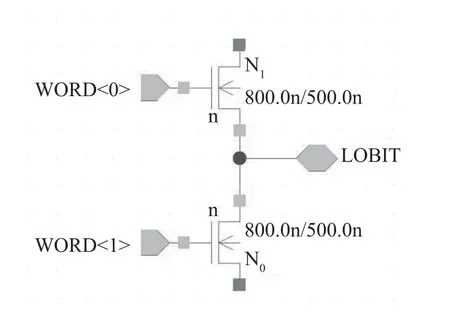

为达到读取速度的要求,ROM单元晶体管级的电路设计如图6,两个N管共漏减小位电容,版图设计时在栅上覆盖三铝,减小电阻。再根据此单元,全定制设计一字长11位、字深11位(2048×11)的ROM模块,嵌入自动布局布线的版图内部。

图6 ROM单元晶体管级电路图

4 NCO仿真结果及性能评估

按照上述结构,笔者设计的电路工作时钟为80MHz。用DSP作为微处理器,通过系统测试,该NCO的性能指标达到了设计要求,频率分辨率Δf=0.0186Hz,输出频率fout=25MHz(当然,NCO输出频率的上限要受到Nyquist定律的限制,即fout的最大值为工作时钟的1/2,实际设计一般不大于0.4fclk)。图7为NCO的部分仿真时序图。

图7 写时序和输出时序图

5 结束语

本文介绍了一种NCO的ASIC实现方法,用该方法设计的NCO可实现对载波频率、相位和幅度的完全控制,由于片内全定制设计ROM作为查找表,并引入流水线结构设计,使得NCO有较高的精度,且电路结构简单,可靠性高,在数控振荡器的传统设计方法上提高了电路精度和频率,非常适用于在正交数字混频器重进行高精度的数字调制/解调。