边缘检测方法在线阵CCD大坝位移计中的应用

刘建林戴瑜兴沈 雁

边缘检测方法在线阵CCD大坝位移计中的应用

刘建林1,2, 戴瑜兴2, 沈 雁2

(1. 湖南机电职业技术学院 电气工程系, 湖南 长沙, 410151; 2. 湖南大学 电气与信息工程学院, 湖南 长沙, 410082)

根据大坝变形监测的实际需求, 采用先进的CCD以及FPGA技术, 设计了用于大坝水平位移监测的高精度位移计. 根据线阵CCD的特性, 论述了利用平行光源进行测量的结构及原理. 通过对CCD图像进行数字化, 采用数字的高斯滤波及边缘检测算法对CCD图像进行像元级的边缘定位. 在实验中运行了FPGA作为处理部件, 采用Verilog HDL对处理算法进行逻辑设计, 通过论证, 系统具有很高的测量精度以及集成度.

大坝变形监测; CCD; 边缘检测

大坝为开发水利资源发挥巨大作用, 给人类带来极大便利. 但由于其建造历史、环境、材料与工艺的不同, 在面对今天复杂多变的气候变化和自然灾害时存在一定的隐患. 因此, 大坝的安全监测十分重要. 第1时间掌握大坝工作状态, 可为大坝日常运行的状况提供评价依据, 有助于制定合理的控制计划、维护修理措施和发布险情警报[1], 可大大提高资源利用率, 减少对环境的不良影响.

大坝安全监测中的一项重要内容——大坝变形监测, 国家有确定的实际要求[2]. 考虑大坝变形监测的发展趋势[3], 本文结合利用FPGA作为单片式控制处理核心、东芝公司的线阵CCD芯片TCDl703C作为测量传感器以及光电式位移计用于大坝水平位移监测. 与位移计的测量精度0.1 mm的指标相比, 光电式位移计的测量精度提高了4倍, 达到了0.02 mm, 有效测量范围也达到了0~50 mm, 充分满足了对大坝测量位移数据的高精度要求.

1 线阵CCD位移计

1.1 系统结构

线阵CCD大坝位移计的硬件系统结构见图1. 主要的构成部件包括了线阵CCD器件TCD1703C、AD转换器、FPGA以及一些外围部件. FPGA是最核心的处理部件, 其中运行有Nios II软核作为嵌入式处理器、检测算法的逻辑电路和驱动线阵CCD器件的逻辑电路. 在FPGA的驱动下, TCD1703C按时钟依次将感光元素线阵的电压信号输出到AD转换器. AD转换器将模拟信号转换成数字信号送入FPGA进行处理. 在FPGA中经过高斯滤波、差分运算产生线阵CCD的梯度图像, 同时提取边缘点左右相邻各2个像元的位置以及梯度数据, 可以精确地将图像边缘定位在一个像元上. 至此便将CCD原始信号变成了与钢丝位置相关的边缘数据序列, 再通过Nios II软核的处理最终计算出钢丝当前所处的位置.

图1 系统结构框图

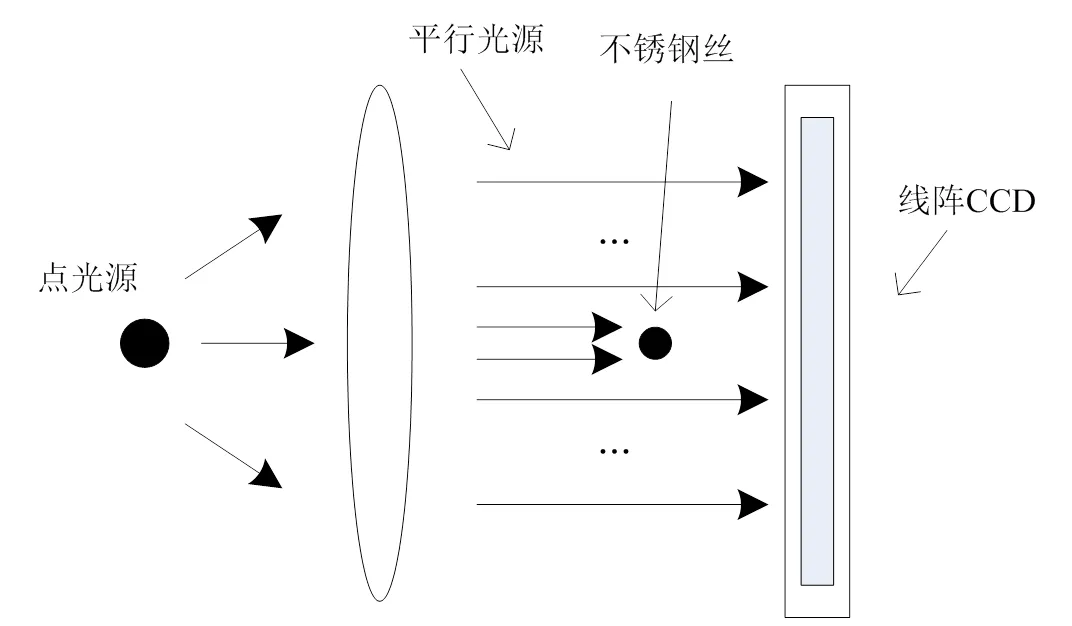

1.2 测量原理

在线阵CCD大坝位移计中, 被测物体为一根0.8~1.2 mm的细钢丝线. 为CCD提供光源的是一个点光源, 通过光学系统将其转化成一束平行光照射到线阵CCD器件上, CCD的微光敏元素列受到光强的影响便会形成离散的分布电荷, 进而在驱动电路的作用下, 依时钟转化为电压信号输出. 其原理示意图见图2[4]. 当将细钢丝线放置在光源与线阵CCD之间时, 由于细钢丝线的遮蔽, 其在线阵CCD上形成一个暗带, 而CCD两边未被遮蔽部分则表现为亮带. 细钢丝线的粗细决定了暗带的宽度, 为了提高精确度, 应尽量使用较细的钢丝线. 通过对CCD上暗带的定位, 便可以计算出钢丝的位移.

图2 测量原理图

2 边缘检测算法的应用

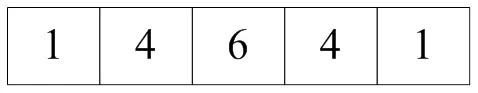

2.1 高斯滤波

引入高斯滤波器的原因在于线阵CCD经光线感应后生成的图像含有噪声, 而图像的差分运算对噪声非常敏感, 通过高斯滤波器对图像进行去噪便可极大提高边缘检测器的性能. 高斯滤波器根据高斯函数的形状来确定滤波模板的权值. 高斯函数的傅里叶变换也是高斯函数, 使得高斯滤波器在平滑滤波器中得到了广泛的应用. 将连接的高斯函数离散化便可用于高斯滤波器, 对于较小尺寸的一维高斯滤波器可以使用帕斯卡三角形来逼近. 5个点的高斯滤波器对应于帕斯卡三角形的第5行[5](见图3).

图3 高斯滤波模板

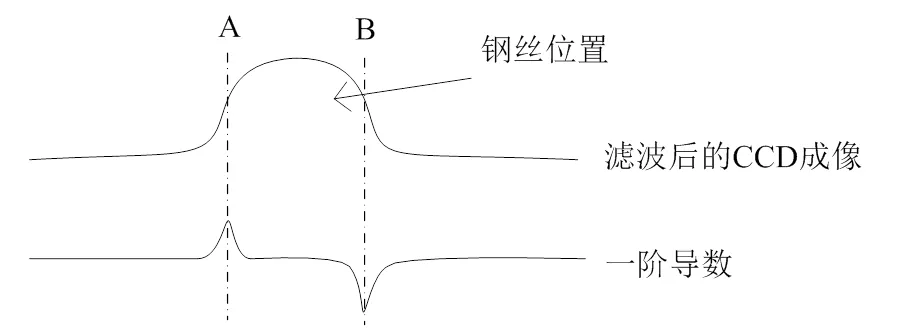

2.2 边缘检测

在经过梯度算子获得梯度图像之后, 为了确定边缘的位置, 构造一个包含5个像素的窗口来完成对边缘的提取工作. 具体步骤如下:

第1步: 对()求梯度,() =(+ 1)-().

第2步: 窗口边缘检测.

当() ≥(+ 1)>(+ 2)且() ≥(-1)>(-2)时() =(). (1)

当() ≤(+ 1)<(+ 2)且() ≤(-1)<(-2)时() =(). (2)其它情况下() = 0.

满足式(1)或式(2)的点则为边缘点. 在第2步中实际上是取得梯度图像中边缘的2个峰值点. 在实现中, 可以先对梯度图像取绝对值, 仅用式(1)即可. 这样减少了不必要的逻辑单元使用量.

图4 边缘及一阶导数关系图

3 功能实现

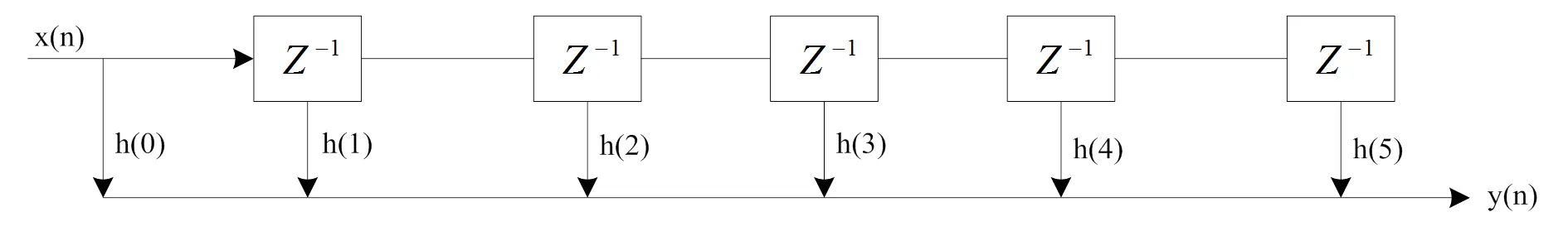

3.1 高斯滤波器的设计

由2.1节可知, 高斯函数离散化后的值便是高斯滤波器模板的各处的权重, 所以可看作是线性滤波器. 在使用逻辑电路实现高斯滤波器时, 分节延迟线是其中的基本结构单元, 输入数据依次延迟并通过抽头进行加权求和输出结果. 其结构见图5.

图5 高斯滤波器实现结构

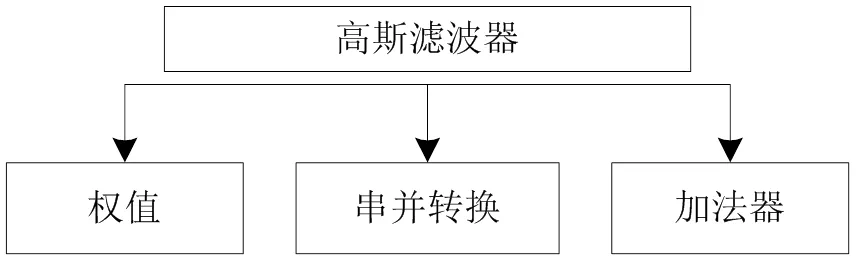

高斯滤波器由3个层次构成(图6). 首先串行的数据依次进入延迟线, 从而由串行数据转换为并行数据; 然后对并行数据进行抽头并加权; 最后对各加权的抽头数据进行累加输出得到滤波后的数据.

图6 高斯滤波器层次结构

3.2 边缘检测算法实现

找出局部梯度值最大的像元位置, 即图像灰度变化是边缘检测的主要目的. 数据的并行处理, 由4个比较器完成(见图7), 有利于提高系统的处理速度. Quartus II软件的LPM库中提供了本文需要的比较器, 可直接调用. 移位寄存器, 由5个D触发器组成, 依据给定的时钟信号, 串行数据依次移位输入转换成并行输出. 在图7中, 数据从data_in端输入, 由时钟控制5个D触发器完成串转并功能, 然后输出5组数据分别进行比较. 只有当这几组数据同时满足式(1)或式(2)时, 输出结果才为真, 即表示判断到了图像的边缘. 进一步便可以得出细钢丝线投影到CCD上的准确位置.

图7 边缘检测逻辑电路

3.3 位移计算处理

通过边缘检测运算之后, 得到的便是边缘检测结果序列:(1)、(2)、(3) …(). 它们记录了各边缘点所在的位置以及梯度幅值. 可能发生的情况是, 在整个序列中分布着许多比较小的梯度幅值, 这是因为高斯滤波器只是尽可能的使得序列变得平滑, 但一定会存在许多斜率很小的波纹. 因为需要通过阀值将它们忽略掉. 钢丝位置的计算流程见图8. 图8中0和H分别表示2点之间宽度的阀值以及梯度幅值(斜率)的阀值.

图8 位移计算流程

4 总结

本文以线阵CCD的原理为出发点, 讨论了利用平行光源及细钢丝线进行位移测量的大坝移位计的结构及硬件组成. 并根据数字图像处理的特点, 提出了通过高斯滤波抑制噪声, 通过差分运算进行边缘检测的定位方法, 使得定位的检测精度保持在像素级, 从而精确地计算出钢丝在量程范围内的位移位置. 在实验中, 采用FPGA作为处理器件, 将CCD驱动、检测算法及其它控制处理集成到单片FPGA上. 通过软硬件的结合, 减小了位移计的尺寸, 并提高了位移计的处理速度及测量精度.

[1] Mueuler S. Instrumentation and control system for Guangzhou[J]. International Journal on Hydropower & Dams, 1998, 5(2): 99-101.

[2] 中华人民共和国能源部和水利部. 混凝土大坝安全监测技术规范[M]. 北京: 水利电力出版社, 1990.

[3] 李宗春, 李广云. 我国大坝变形监测技术现状与进展[J]. 测绘通报, 2002(10): 19-21.

[4] 柴世杰, 戴瑜兴, 温烨婷. 基于C8051F410的光电式引张线仪设计[J]. 电子技术应用, 2011(5) : 41-44.

[5] 贾云得. 机器视觉[M]. 北京: 科学出版社, 2002: 71-76.

[6] 吴晓波. 图像边缘特征分析[J]. 光学精密工程, 1999, 7(1): 59-63.

Linear array CCD dam displacement meter based on edge detect method

LIU Jian-lin1,2, DAI Yu-xing2, SHEN Yan2

(1. Department of Electrical Engineering, Hunan Mechanical & Electrical Polytechnic, Changsha 410151, China; 2. Department of Eectrical and Information Engineering, Hunan Uiversity, Changsha 410082, China)

According to the deformation monitoring of dam’s actual needs, based on advanced CCD and FPGA technology, a displacement meter was designed with high precision and automatic measurement for dam use. On the basis of edge gradient step characteristic of a gray image, Gaussian filter and edge detection algorithm was used to find the pixel level boundary of a CCD image. Taking FPGA as the system processing core and the digital circuit hardware carrier, Verilog HDL language was used to design the system which is all included in a single FPGA. Simulation and test show that the sopc system had high precision, high processing speed, high integration density and high reliability.

dam deformation monitoring; CCD; edge detection

TP 391.41

1672-6146(2012)04-0049-04

10.3969/j.issn.1672-6146.2012.04.010

2012-10-16

湖南省科技计划 (2012FJ3042)

刘建林(1978-), 男, 讲师, 硕士研究生, 研究方向为建筑智能工程. E-mail: tikolin@126.com

(责任编校:刘刚毅)