2012年CPU技术趋势

从2006年的65nm、2008年的45nm到2010年的32nm,2012年如果继续使用传统的CPU制程工艺,那么就会遇到难以逾越的技术瓶颈。因此,明年年初英特尔将会率先在代号为Ivy Bridge的22nm制程处理器上采用3D晶体管技术。新的晶体管技术可以保证CPU制程继续遵循摩尔定律的规律发展,为计算机世界带来新的变革,直至接近硅原子的直径(0.3nm)。而ARM架构的CPU也将告别40nm的晶体管制造工艺,升级到28nm。CPU技术的创新将会使个人PC和移动终端设备的性能翻番。

特别值得一提的是,当前市场上风生水起的智能手机和平板电脑将从CPU制程工艺的进步中获益良多,尤其是在电池续航时间方面。因为新的制程工艺将会大幅度改进CPU芯片的微结构,在成倍提升性能的同时,也将大大降低功耗。未来,在手机上观看高清3D电影、玩大型游戏就不会再有意犹未尽的感觉了。

晶体管越小速度越快

每一个芯片都是由晶体管组成的,每一个晶体管通常负责控制1位(0或1)的信息。英特尔最新的32nm制程Sandy Bridge处理器由近10亿只微型的晶体管元件组成,而且截止目前 “晶体管的体积越小,集成的数量越多,芯片的计算性能就越高”的规律依然有效。但是在原有技术的基础上继续升级到更小的22nm晶体管已经没有可能,因为量子力学效应阻碍了晶体管性能的发挥,除非创造出新的晶体管结构。

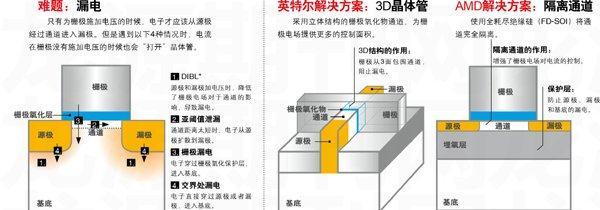

从基本结构上来看,一个晶体管包含3个电极,分别是源极、漏极和作为控制电极的栅极。其中,源极和漏极被芯片基底分隔开,使二者互相隔离。这3个电极都是由硅材料制作而成的,硅原子的最外层包含4个电子(8个电子为稳定态)。如果在源极与漏极的硅晶体中掺入磷和砷,那么因为它们的最外层包含5个电子,所以这样就会多出一个自由电子,使半导体硅可以导电(N型半导体)。如果在基底的硅晶体中掺入硼元素和铝元素,那么因为它们的最外层包含3个电子,所以这样就会缺少一个电子,从而使半导体硅可以导电(P型半导体)。在P-N结之间使用二氧化硅制作一个绝缘的分隔区域,可以阻止电子的流动。

如果给栅极增加电压的话,这个分隔区域就会打开一个通道,帮助电子轮流从源极进入漏极,此时晶体管处于“开”的状态。但是,当晶体管的结构越来越小的时候,就会遇到即使栅极不加电压,源漏极之间仍然有电流通过。也就是说,在应该处于“关”的状态时,晶体管仍然保持“开”的状态。该问题的存在意味着我们无法通过继续减小晶体管的体积来获得更高的性能。

漏电导致芯片性能下降

漏电消耗了近一半的电流,而且晶体管的体积越小,漏电消耗的电流越大。控制漏电电流需要解决源极和漏极对芯片基底的影响。尤其是当漏极加上高电压时,漏感应势垒降低(Drain Induced Barrier Lowering,DIBL)现象显著地降低了栅极电场对于通道的影响,导致即使栅极在没有施加电压的情况下,源极在漏极电场的影响下依然会打开通道,使电流可以通过,而隧道效应(Tunnel Effect)与漏感应势垒降低同样明显。根据量子力学的原理,微观电子的位置存在不确定性和随机性。如果漏电感应势垒太薄太弱的话,那么电子跨过势垒的可能性就会增加。电子将会随机出现在势垒的另一侧,就像跨越了一条隧道。如果晶体管的体积继续变小,那么晶体管之间的势垒就会减小,栅极电子就会击穿二氧化硅绝缘层,甚至有可能击穿源极到漏极之间的基底材料。因此,解决漏电问题的首要方法就是加强栅极电场对电子的控制。

目前来看,由隧道效应与漏感应势垒降低现象引起的功耗增加问题需要通过重新设计栅极对通道的控制才能避免,芯片制造商在过去的几年中研究出了3种可行的解决方案。

3D结构封装晶体管

首先,我们应该努力改进栅极与通道之间的绝缘层。为了实现该目标,英特尔已经改变其45nm制程芯片的材料,将二氧化硅升级为铪合金材料。这种比二氧化硅更厚一些的高K材料(K源于希腊文Kappa,它是用于衡量一种材料存储电荷能力的电子学术语)具有良好的绝缘属性,并且可以加强栅极与源漏极通道之间的场效应,降低隧道效应对芯片性能的影响。

不过,当CPU制程工艺提升、线路宽度降低到32nm以下的时候,高K材料就无法满足结构设计的需求了,这就是为什么芯片制造商将目标重新对准改变现有晶体管结构设计的原因。原有的平面结构设计已经在市场上延续了几十年,将其改为3D结构面临着巨大的风险,但是成功的意义远大于风险。在英特尔重新设计的鳍式场效应管(FinFET)中,通道被设置为了凸起的形状,看起来就像在基底上凸起的鱼鳍一样。栅极将通道的3面都封闭起来,这样就可以在更大的面积上对通道进行控制,减少了漏电电流。此外,由于通道不再受到干扰,电子就可以无障碍地通过,同时速度也不会受到影响,这样的话晶体管就可以获得更快的开关频率。

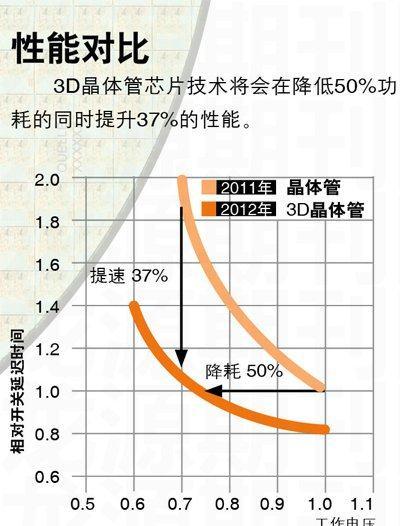

其实鳍式场效应管(FinFET)的技术从10年前就开始研究了。2012年,英特尔将会在其下一代适用于桌面PC和笔记本电脑的Ivy Bridge处理器上采用该技术。据英特尔官方声明,这种3D晶体管芯片技术将会在降低50%功耗的同时,提升37%的性能。

除了英特尔的3D晶体管方案之外,它的竞争对手AMD和IBM也已经联合研发了另一种控制漏电电流的方法。与英特尔将通道移动到芯片基底上不同,AMD和IBM想要在基底上将通道完全“隔离”起来。因此,在通道与基底之间加入了一个埋氧层(Buried Oxide),组成全耗尽绝缘硅(Fully Depleted Silicon On Insulator,FD-SOI)晶体管。

原则上,FD-SOI晶体管与FinFET晶体管同样高效。但是目前全耗尽绝缘硅(FD-SOI)技术面临着多薄层晶圆生产困难的问题,预计到明年年初才能大规模量产这种晶圆,而英特尔的鳍式场效应管(FinFET)已经进入量产阶段。

降低功耗 提升性能

英特尔计划2013年年初在Atom处理器上采用新的3D晶体管技术,并将优化该芯片在智能手机和平板电脑上的运行表现。众所周知,与ARM架构的处理器相比,英特尔的Atom处理器需要耗费更多的电力,这是目前几乎所有的移动终端设备都选择ARM架构处理器的重要原因之一。英特尔的x86架构CPU是为Windows桌面电脑处理各种任务设计的,采用了复杂指令集,在设计之初就没有考虑到需要为使用电池的设备进行节能设计,而ARM架构的CPU采用了更高效的精简指令集设计,更适合采用基于Unix/Linux的iOS和Android移动终端设备使用,拥有良好的功耗控制表现。

ARM的指令采用统一的4字节长度,现在智能手机和平板电脑上普遍采用的ARM授权Cortex-A9架构CPU基于先进的8级流水线,并且支持推断型乱序执行(out-of-order execution)特性,在每个循环中可以执行多达4条指令。另外,ARM的指令集都可以带条件执行,所以诸如“If……then”这样的语句能够更快速准确地执行。而x86架构的CPU无法直接识别条件声明,而是会预测运行结果。如果预测结果出现错误,那么指令就会被返回并进行重新计算。同样,x86架构的Atom处理器也不支持乱序执行,而新的ARM架构芯片,比如Tegra 2双核处理器已经支持乱序执行。

结构上的根本不同,使得ARM架构处理器的热设计功耗(TDP)拥有明显优势,TDP指的是当处理器达到最大负荷时所释放出的热量。目前,大部分Windows平板电脑上使用的Atom处理器TDP至少为5W,而Tegra2处理器仅2W。不过,可以预见未来采用新晶体管的Atom处理器在TDP表现上将有大幅改善,真正阻碍其发展的将会是复杂指令集的低效率。

智能手机性能追赶电脑

尽管ARM处理器在移动终端领域如日中天,但是它并没有停止前进的步伐。今年年底,采用40nm的四核心处理器产品即将上市,比如主频为1Ghz~1.5Ghz的Tegra 3处理器。它引入了NEON增强指令集,强化了DSP处理功能和多媒体处理效率,并且提供了增强型浮点运算技术,以满足下一代3D图形和游戏的要求。英伟达声称Tegra 3的功耗要比Tegra 2更低,但芯片表面积从49mm²增加到了80mm²。当然除了集成NEON增强指令集之外,Tegra 3还集成了强大的GPU。

其他的ARM架构处理器制造商,比如高通和德州仪器将会等到芯片制造工艺升级到28nm的时候再行动。因为新一代的Cortex-A15架构将会升级到28nm制程,支持高达2.5GHz的主频,采用1MB~4MB的共享式高速二级缓存,更好地执行视频解码和3D影像处理等任务。估计到2012年秋天的时候,芯片制造商台积电就会率先生产28nm制程的Cortex-A15架构CPU。

更重要的是,Cortex-A15架构不只是为移动终端设备设计。它将地址空间扩展到了40位,因此最多可以使用1TB的内存,并且支持虚拟机技术(该技术对于PC和服务器非常重要)。此外,微软已经声明下一代操作系统Windows 8将会支持ARM架构的处理器,同时英伟达也透露了八核心ARM架构处理器的生产计划,显然垄断个人PC产业长达30年的Wintel联盟已经终结。但是ARM和英特尔的竞争对于最终用户而言是有益的,因此我们希望看到功耗更低的ARM架构超轻薄笔记本电脑,也希望英特尔打破ARM架构CPU在移动终端上的垄断地位。