一种高精度多通道采集系统及其性能分析

胡永兵,周云飞,杨 钦

(华中科技大学 机械科学与工程学院,湖北 武汉 430074)

在巨型或大型测控系统中,往往需要对大量测试点进行数据采集,并要求数据采集系统能够更快、更准、更稳定。这些测试点需要监控不同的模拟信号,例如:温度、湿度、压力、速度等。

因基于单片机的数据采集系统处理速度低下,而基于DSP的数据采集系统会产生过于频繁的中断,所以考虑采用基于可编程逻辑器件 (FPGA)的数据采集系统。基于FPGA数据采集系统有着开发周期短、集成度高、功耗低、工作频率高、设计费用低、编程配置灵活等一系列优点[1]。本文介绍了一种基于FPGA的高速高精度多通道的数据采集系统,并对此系统的精度性能进行了一定的分析。

1 系统概述

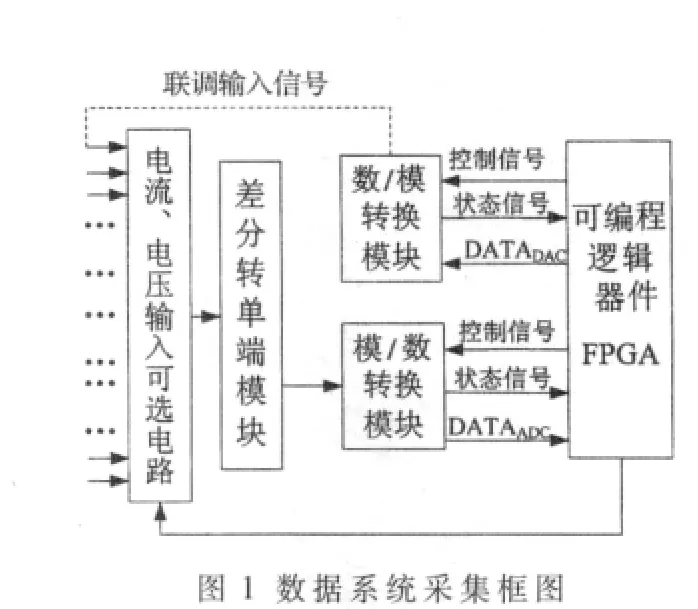

基于FPGA的高速高精度多通道采集系统由如下几个模块组成:电流与电压输入信号可选模块、差分信号转单端信号模块、模/数转换模块、数/模转化模块和信号处理控制模块,如图1所示。不论是4 mA~20 mA的电流信号,还是-10 V~+10 V的电压信号,都可以被采集。这些模拟信号经由电流信号与电压信号可选模块,经过选择后,再通过差分信号转单端信号模块进行差分转单端处理(单端信号也适用),然后再进入到高速精密模/数转换器进行数据转换。在这整个过程中,FPGA对模/数转换器进行时序控制,同时将转换后的数字信号传输给处理模块。为了验证数据采集系统的精度性能,在本文中特意加入了数/模转换电路,其主要作用就是与模/数转换模块进行联调。

2 系统硬件结构

2.1 电流、电压输入信号可选电路

在工业应用中,常见的模拟信号都是以电流或电压形式被采集,其范围一般为4 mA~20 mA电流或者-10 V~+10 V电压[2]。为了使数据采集系统既能采集电流信号又能采集电压信号,在模拟信号进入的前端设计了一个可选的电流信号转电压信号的转换电路。

当采集的信号是电流信号时,需要将电流信号转换成电压信号。在图2中使用250 Ω的精密电阻作为I/V转换的取样电阻,将输入的电流信号转换为电压信号,采用公式:

其中,Vin为转换后电压信号,Iin为采集的电流信号,R为采样电阻。电流信号从P0和N0口输入,其中P0端接信号端,N0端接地。4 mA~20 mA的电流信号通过式(1)可转化成1 V~5 V电压信号。

图2 电流、电压输入信号可选电路图

当采集的信号是电压信号时,只需不焊接图2中电阻R185。而且此时输入的信号既可以是差分信号,也可以是单端信号。

2.2 高速精密放大器

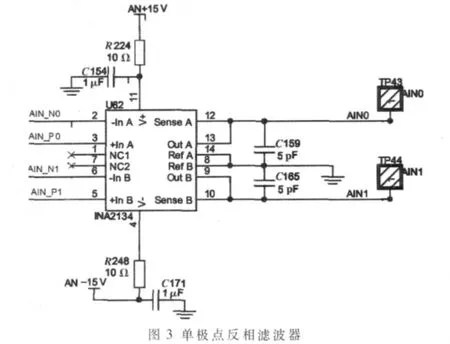

INA2134是采用片上精密电阻和高性能运算放大器组成的差分线路接收器,具有卓越的AC性能,包括低失真(1 kHz时的 0.000 5%)和高压摆率(14 V/μs),保证良好的动态响应。此外,宽输出电压摆幅和高输出驱动能力,适用于多种要求苛刻的应用环境。双通道含有完全独立的电路,可以防止交互串扰,即便过载或超载也能保证不相互影响[3]。

如图3所示,差分信号分别接在引脚3、引脚2和引脚5、引脚 6,连接到输入源阻抗必须是几乎相等,以保证良好的共模抑制。一个10 Ω的源阻抗不匹配,会降低近74 dB的共模抑制比[3]。

INA2134采用±15 V电源供电,且每个电源引脚上加上去耦电容,这些电容要充分靠近芯片引脚。输入的差分信号,经INA2134转换成单端信号,VAIN0=VAIN_P0-VAIN_N0,然后从AIN0输出。

2.3 A/D模块

AD7606是16 bit 8通道同步采样的模数数据采集系统,其内置模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器、16 bit电荷再分配逐次逼近模/数转换器(ADC)、灵活的数字滤波器、2.5 V基准电压源、基准电压缓冲以及高速串行和并行接口。AD7606采用5 V单电源供电,可以处理±10 V和±5 V真双极性输入信号,同时所有通道均能以高达200 kS/s的吞吐速率采样[4]。

从INA2134输出的模拟信号,进入 AD7606。图4显示了AD7606的电路图,4个AVCC电源引脚需要各使用1个100 nF和1个10 μF去耦电容。VDRIVE电源连接到与处理器(FPGA)供电的同一电源。

引脚 CONVST A、CONVST B、RESET、BUSY、nRD/SCLK和引脚nCS分别连接到FPGA的普通I/O端。其中引脚CONVST A、CONVST B可以互连后再连接到FPGA;引脚nBUSY的信号流向是从AD7606到FPGA,其余的则是通过FPGA控制AD7606的。V1和V1GND为单端信号输入引脚对,DB0~DB15为转换输出的数字信号。

2.4 D/A模块

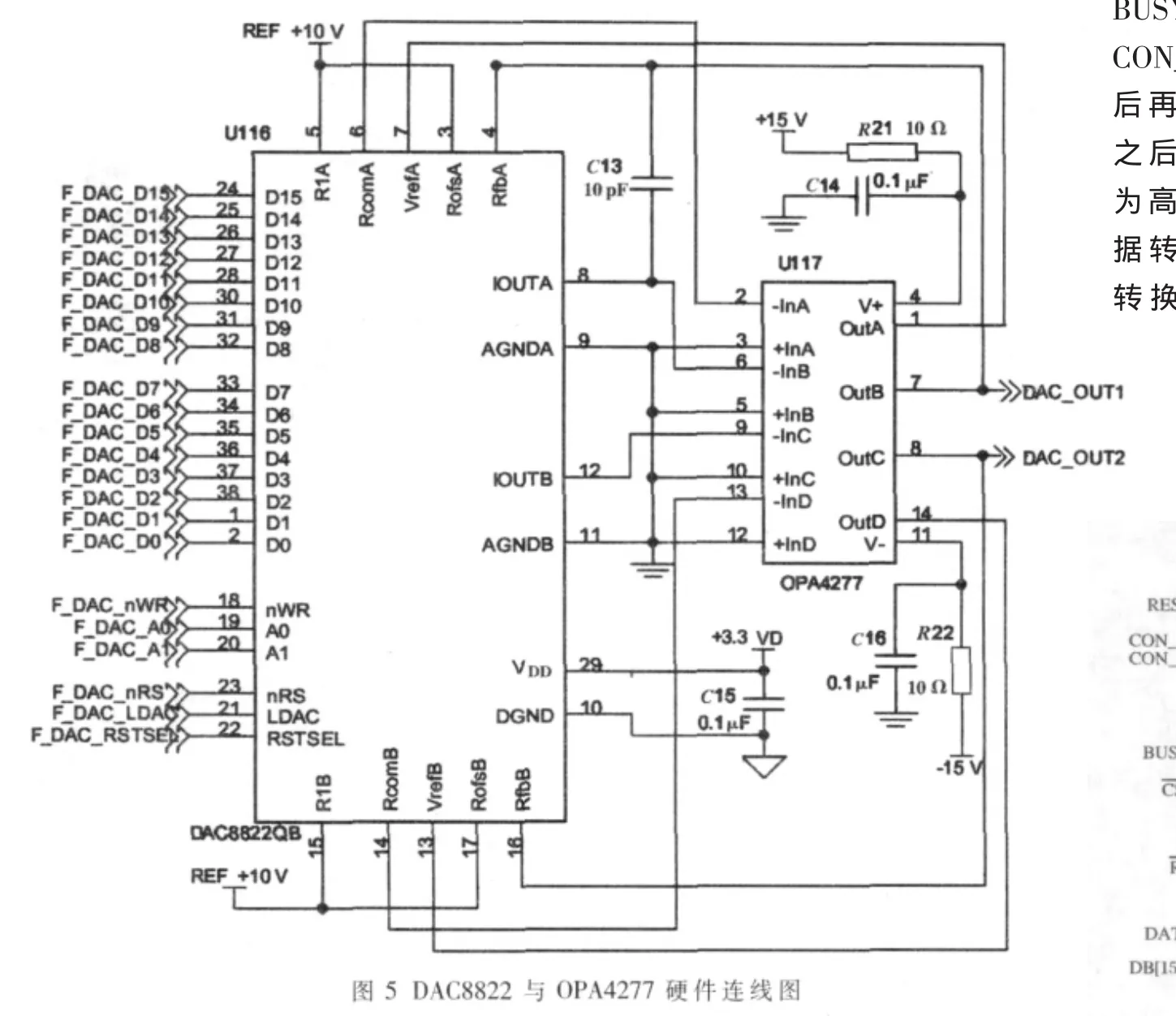

DAC8822是双路、2.7 V~5.5 V单电源供电的乘法数模转换器,具有低噪声、低功耗、低稳定时间等优良特性[5],它与OPA4277硬件连线如图5所示。

引脚D0~D15为 DAC8822的数字数据输入端,引脚nWR、A0、A1、nRS、LDAC 和 RSTSEL 分别连接在处理器(FPGA)上。FPGA通过对A0、A1写逻辑选择输出通道。采用与处理器一样的3.3 V电源供电,采取外部高精密参考。为了保证输出的模拟信号尽可能少地受到影响,在模拟输出端连接了一个高精密放大器OPA4277作为电压跟随器,采用双极性电源±15 V供电。

2.5 控制器模块

控制器采用Altera公司的Cyclone III系列的FPGA,其具有低功耗、低成本和高性能,体系结构包括高达120 K的垂直排列逻辑单元(LE)、以 9 KB(M9K)模块构成的4 Mb/s嵌入式存储器、200个18×18的嵌入式乘法器,且含有非常高效的互联和低偏移时钟网络,为时钟和数据信号结构提供链接;采用3.3 V、2.5 V、1.2 V分别给不同模块进行供电;灵活的I/O控制使得电路设计方便、编程简化等[6]。在本研究中采用的是EP3C25F324。采用AS和JTAG配置模式,配置芯片为 EPCS16SI8N[7]。器件的时钟配置为50 MHz。

3 系统软件设计

程序的编写采用硬件描述语言Verilog HDL,编写软件为 Altera Quartus II9.0。

3.1 模数转换的程序设计

控制器FPGA通过对模数转换器AD7606写逻辑实现对模/数转换器的控制。图6是并行模式下转换时读取数据时序图。首先将转换器件复位,然后检测BUSY和RD的状态,并将CON_A、CON_B写为高电平;当BUSY为低电平、RD为高电平时,通过对CON_A、CON_B进行写低操作,并维持 t2,然后再写为高。在CON_A、CON_B变为高电平之后的t3时间段后,BUSY将会自动转变成为高电平,表示此时采样结束,开始进行数据转换。在转换过程中,同时对上一次的转换进行数据读取,即在BUSY为高电平后的t4时间段,将CS写为低电平;在经过t5时间段后,将RD进行写8个脉冲,在每个下降沿时读取并行数据总线上的数据。

3.2 数模转换的程序设计

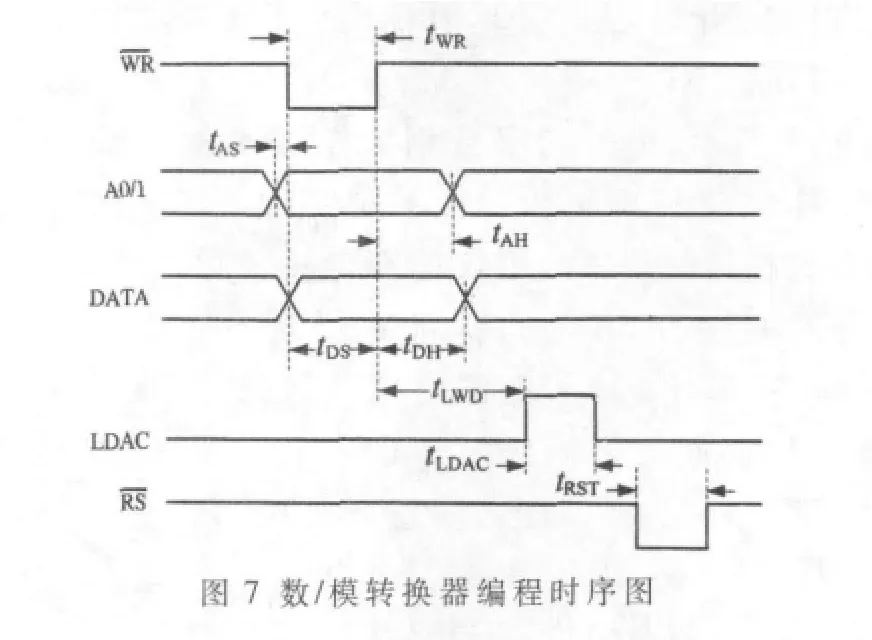

控制器FPGA通过对数模转化器DAC8822的写逻辑实现数/模转换操作,图7为数/模转换器偏程时序图。

WR为写寄存器使能信号,低电平有效;LDAC是DAC寄存器数据传输使能。RS为复位信号,低电平有效。A0和A1为地址编码信号,其高低电平的不同,则输出通道不同,如表1所示。

表1 DAC8822输出通道选择情况

4 实验结果及其分析

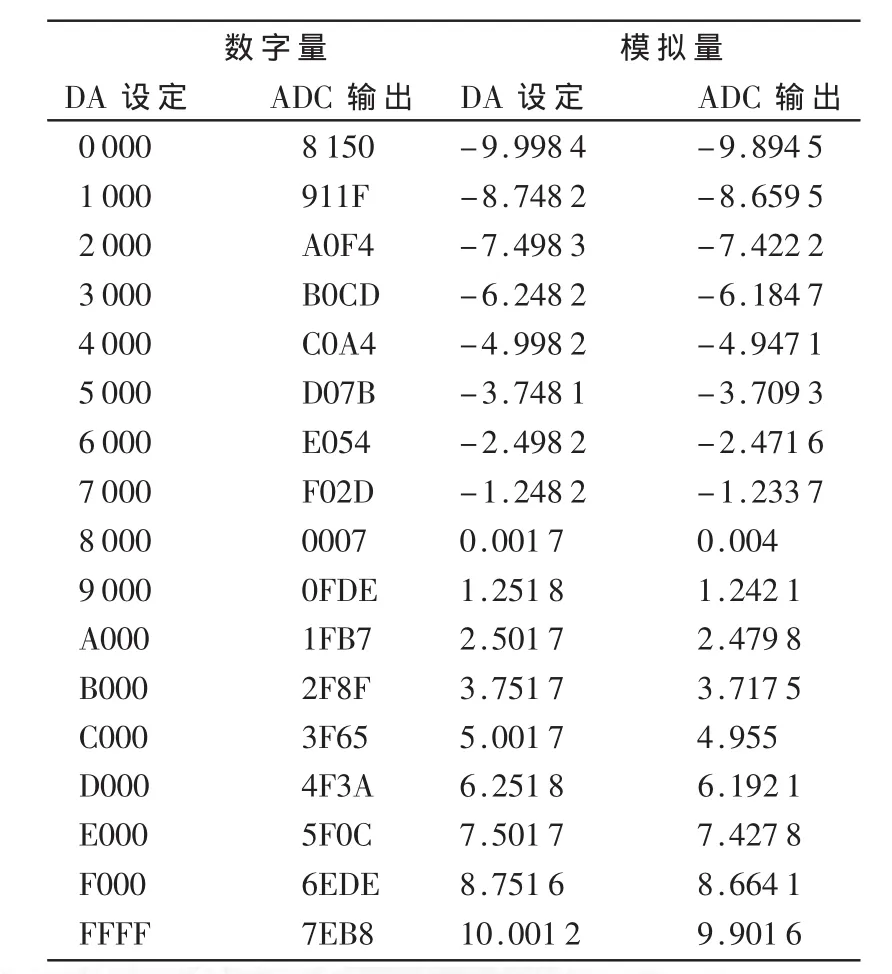

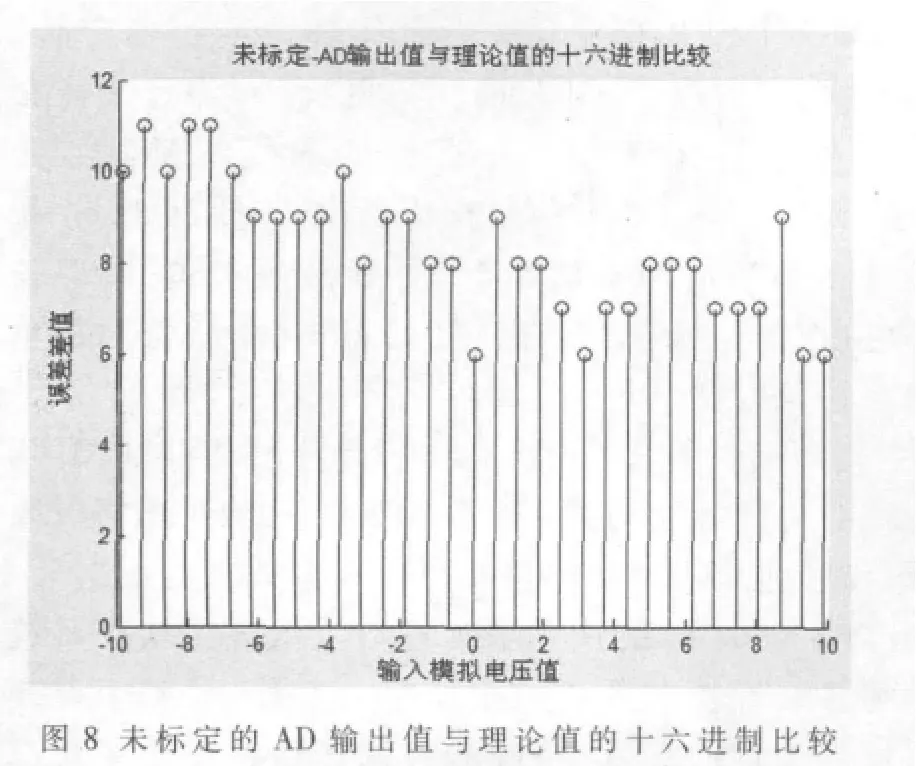

为了验证本数据采集系统精度性能,在研究中将模/数转换器的输出直接作为模/数转换器的输入,即将DAC8822的输出端直接接在电流、电压输入信号可选电路的输入,作为AD7606的输入信号;然后将AD7606输出的数字量与DAC8822设定数字量进行比较。采用最小二乘标定将实测结果进行标定,分析实际转换结果与理论结果的差值。采集系统的采集值如表2所示。利用MATLAB分别绘得图8和图9,其中图8为未标定的AD输出值与理论值的十六进制比较;图9为标定的AD输出值与理论值的十六进制比较,从图9中可见,标定后数据采集系统具有良好的精度性能,可以达到14 bit精度以上。

表2 17个数据采集值

本设计中,简单且可选的电流转电压信号的转换电路设计保证了输入的模拟电流或电压信号都能被采集;差分转单端的电路设计让差分和单端的模拟信号都能被采集;高速高精的模/数转换模块既保证了转换速度,又确保了转换精度;灵活多变的I/O使得FPGA的电路设计和编程都趋于简单。在通过数/模转换器与模/数转换器之间相互联调,得出此信号采集系统能够保证精度在14 bit以上,是一种精度性能良好的高精度多通道采集系统。

[1]李兰英.Nios II嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2006.

[2]BAKER B.嵌入式系统中的模拟设计[M].李喻奎,译.北京:北京航空航天大学出版社,2006.

[3]TI.Inc.INA134/INA2134 audio differential line reseivers[Z].1997.

[4]ADI.Inc.8-/6-/4-Channel DAS with 16-bit,bipolar input,simultaneous sampling ADC[Z].2010.

[5]TI.Inc.DAC8822 16-bit,dual,parallel input,multiplying digital-to-analog converter[Z].2007.

[6]Altera,Inc.Cyclone III FPGA family datasheet[Z].2003.

[7]Altera,Inc.Cyclone III configuration interface guidelines with EPCS devices[Z].Version 1.0.2008.

- 网络安全与数据管理的其它文章

- 基于组件的非线性软件开发过程研究*

- 高职院校C2C电子商务网站的设计