基于FPGA的数字化变电站计量仪表研究与设计

杨新华 ,韩永军

(1.兰州理工大学 电气工程与信息工程学院,甘肃 兰州 730050;2.甘肃省工业过程先进控制重点实验室,甘肃 兰州 730050)

随着数字化变电站技术的大力发展和IEC61850标准体系的全面推广,标志着变电站自动化技术进入了全新阶段。因为IEC61850标准的发展方向是“即插即用”,与数字化变电站接口相关的产品将得到快速发展[1]。数字化变电站计量仪表作为数字化变电站内部的智能电子设备,接收合并单元的数据包并由内部的数据处理模块进行运算,得到电压、电流等,整个过程全部为数字量,没有模拟量的参与,计量仪表的精度将大大提高。

近年来,同类产品普遍使用高速数字信号处理器来完成,但其成本较高且工艺复杂,导致设计灵活性不够。本文提出了一种基于SoPC的设计方案,不仅具有较大的灵活性,而且通过对高速FPGA的配置可灵活地对设计进行改动,以适应技术的快速发展,同时系统功耗、成本、设计复杂性都得以降低。

1 总体设计

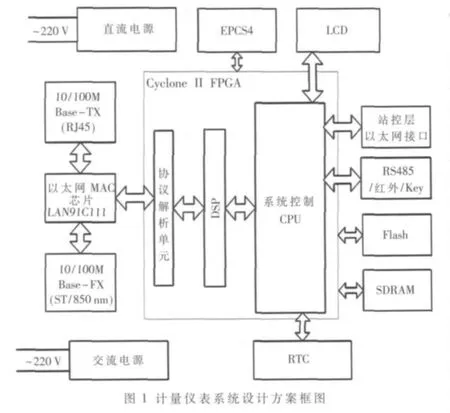

基于SoPC的数字化变电站计量仪表的系统设计方案如图1所示。系统由两路电源、光纤通信电路、以太网接口电路、RTC、LCD、Flash、红外线接口及一片 Cyclone II FPGA组成。其中协议解析单元、DSP、系统控制单元都在一片FPGA上实现,FPGA在设计中处于核心。

系统工作流程:协议解析单元接收合并单元通过光纤或双绞线发出的SMV数据包,由Nios II处理器解析后存放在FIFO中供DSP模块读取;数字信号处理单元负责完成电量、功率以及电能的计算等任务,计算结果存储在FIFO中供系统控制CPU读取;系统控制模块的Nios II处理器对电量信息进行处理,最终完成电参数的显示、储存,同时响应站控层通信服务请求等功能。

2 主要硬件设计

2.1 以太网接口电路设计

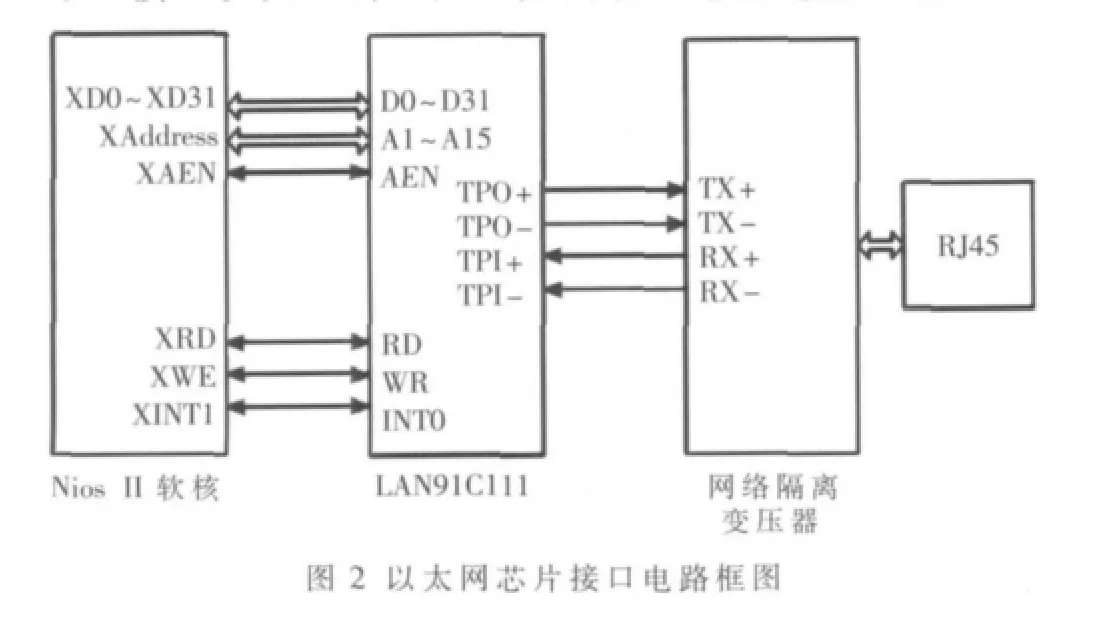

本文采用LAN91C111实现与站内以太网连接,该芯片是SMSC公司专为嵌入式应用系统而推出的第三代快速以太网控制器,片上集成了MAC和PHY,符合IEEE802.3/802.U-100Base-Tx/10Base-T规范[2-3]。LAN91C111与 Nios II软核连接方便,它作为Avalon Memory-Mapped Tristate Slave器件挂在Avalon-MM总线上与Avalon Memory-Mapped Tristate Master连接。LAN91C111的地址线A1~A15、数据线D0~D31、读写控制信号分别与 Nios II的相应信号相连,SoPC系统分配给该芯片的中断优先级为 0。 LAN91C111的输出信号 TPO+、TPO-、TPI+、YPI-接网络隔离变压器TG100-S050N2,变压器的输出接RJ45接口。图2所示是以太网接口电路连接示意图。

2.2 CPU系统模块设计

高速以太网数据交换及数据包解析需要占用相当大的CPU运行资源,因此本设计在一片FPGA上设置了两颗 CPU:cpu_ethernet负责解析数据,cpu_control负责系统控制。

根据该模块要完成的功能,在SoPC系统上配置了标准 NiosII 软 核 、SDRAM Controler、EthernetControler、Avalon Memory-Mapped Tristate Master、片内 RAM、定时器、JTAG_UART等部件,部件添加之后需要设置各个部件之间的连接矩阵、地址、中断优先级。调试过程中CPU从SDRAM中启动,程序及程序运行所需的堆栈、内存都放在SDRAM中,调试完毕后硬件配置文件放在EPCS4中,程序代码放在NOR Flash中。这部分电路设计完成后就可以在Quartus II对电路进行管脚分配、编译。

3 软件设计

本文用Verilog HDL设计了一个RTC IP,用来实现与实时时钟芯片的读写。软件部分包括BSP层、应用程序层。BSP层包括HAL、设备驱动、标准C函数库、RTOS、可选的软件包。其中实现驱动程序的方法采用IP核方式实现外部器件控制。这种方法把外部器件映射到外部存储器空间,作为Avalon Slave器件连接到总线上,Nios II软核通过总线实现器件控制。采用这种方法设计的主要工作硬件描述语言模块,可以由设计者自行定义外设操作的各个存储器,从而实现复杂的时序控制功能。IP核设计完成之后,可以由SoPC Builder开发环境调用[4],灵活添加到用户设计的SoPC系统之中,并且可以提供给其他人使用。

4 基于FPGA的电量参数算法

4.1 有效值测量

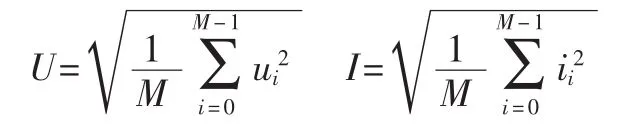

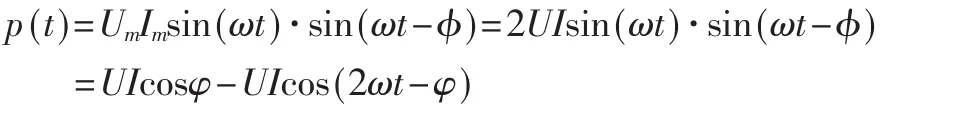

有效值可以用以下两个公式表示:

其中M是交流信号每个周期的采样点数。

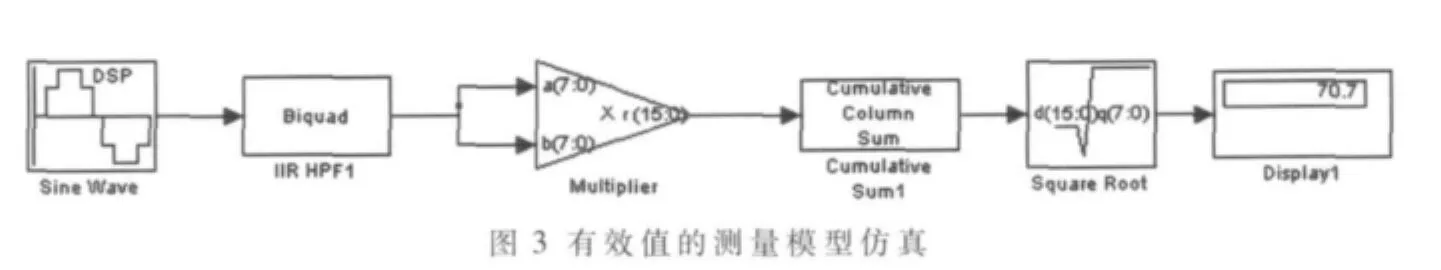

在Matlab/Simulink下建立的有效值测量的算法模型流程可以用图3表示,图3中峰值为100的正弦信号首先经过高通滤波,然后自乘、平方和累加后进行开方运算,仿真时间为一个周期,仿真结果与预期结果一致。从仿真情况来看,影响有效值测量精度的主要是周期的测量。

4.2 有功功率测量

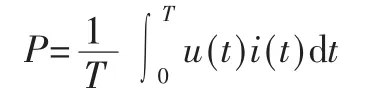

在正弦电路中,瞬时功率可表示为:

瞬时功率在一个周期T内的积分即为平均功率:

本文采用低通数字滤波器法实现有功功率的测量。这种方法将数字乘法器的运算数据结果输入到低通数字滤波器,从滤波器的输出端就得到了有功功率。这是因为在瞬时功率的表达式中,积分第2部分UIcos(2ωtφ)的频率为基波频率的2倍,只要设计好合适的滤波器参数,就可以采用滤波器实现有功功率的测量。

4.3 数字滤波器设计

数字滤波器从实现的网络结构或者从单位脉冲响应分类,可以分成无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)。

根据两种滤波器的特点和本课题的应用实际,高通滤波器用IIR滤波器实现,低通滤波器用FIR实现。

本文中高通数字滤波器的主要指标如下:通带截止频率为 30 Hz,通带纹波 1 dB,阻带衰减 60 dB,采用 4阶椭圆滤波器实现。

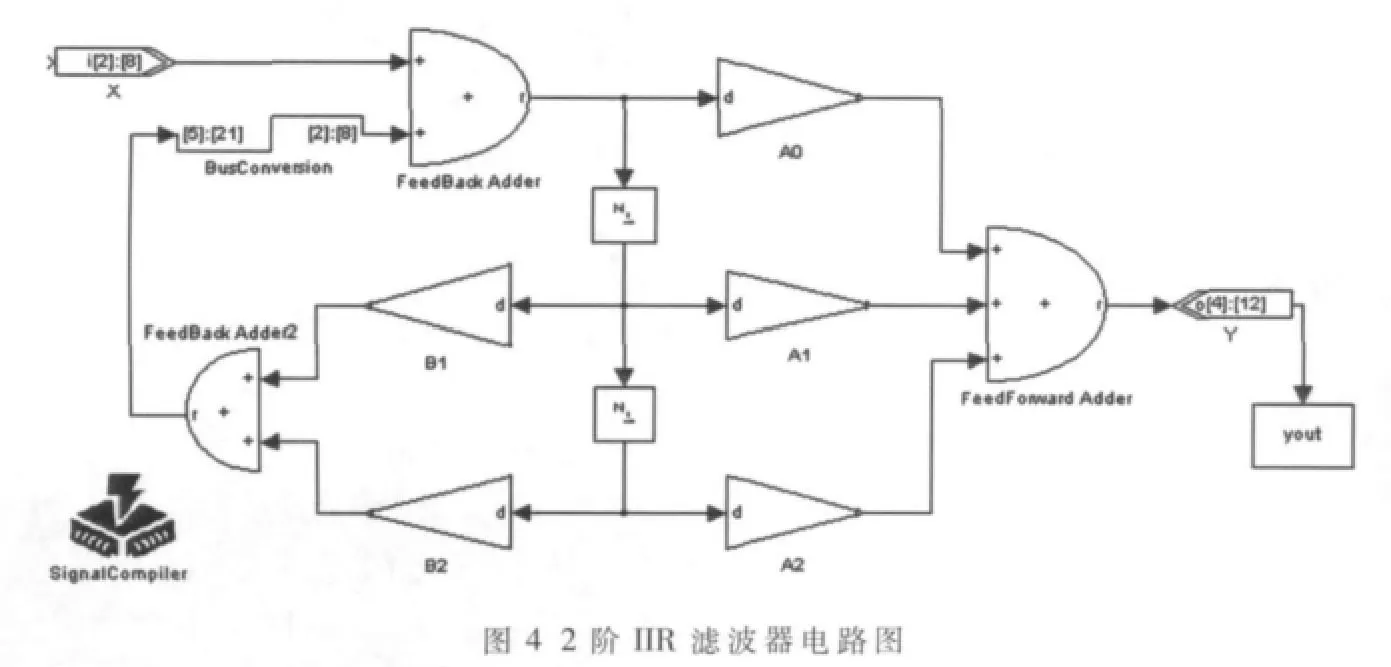

图4为在Matlab/Simulink下搭建的2阶Direct Form II型IIR滤波器电路模型。本文中设计的数字滤波器为4阶IIR滤波器,可以由两节Direct Form II型滤波器级联而成。图4中2阶Direct Form II型滤波器的系数可以由Matlab生成,然后更新模型即可。

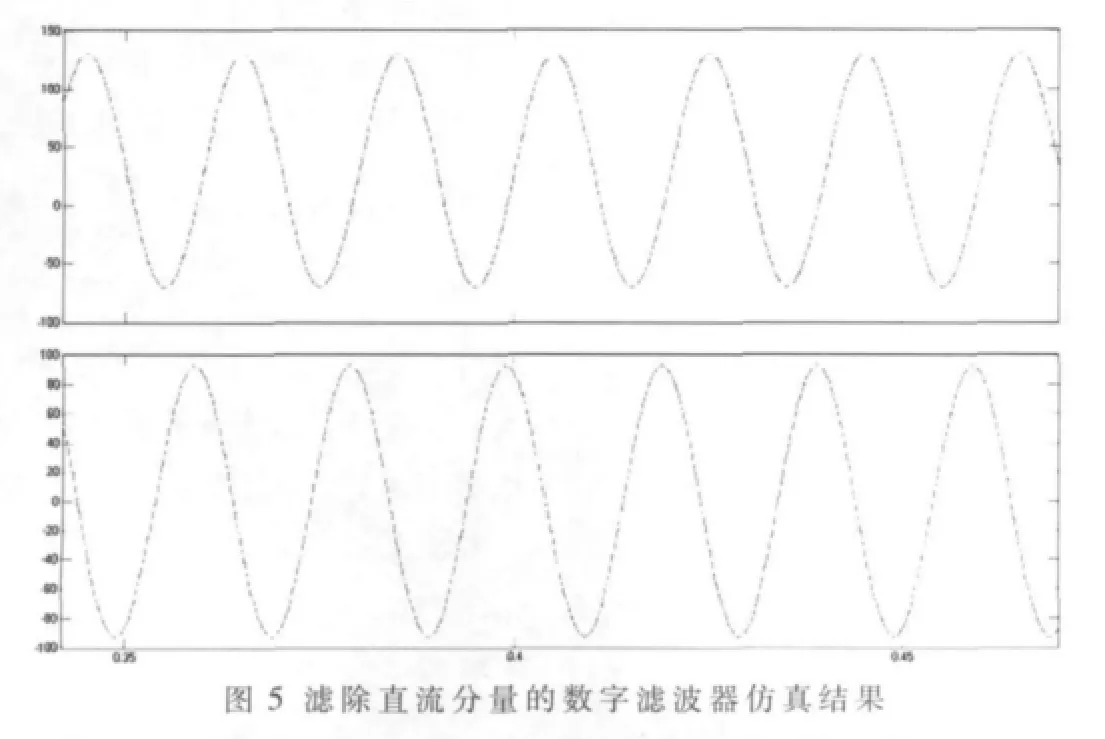

图5为附加直流偏置的正弦信号u(t)=100sin(100πt)+30通过设计的IIR数字滤波器的仿真结果,从图中可以看出,滤波后的信号在±100范围内波动,表明该滤波器能够很好地去除直流分量,满足设计要求。

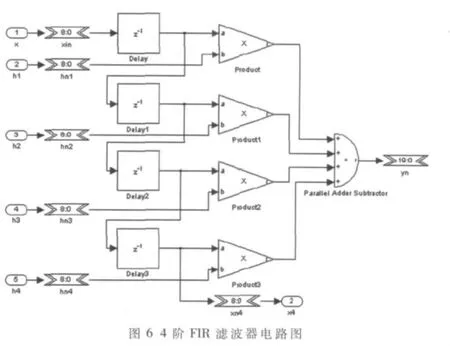

低通滤波器采用FIR滤波器实现,该滤波器主要功能是消除瞬时功率信号中频率为2 W的交流分量,从而得到有功功率信号。据此采用equiripple法设计的FIR滤波器的主要指标如下:阻带截止频率为95Hz,阻带纹波10 dB,通带纹波 1 dB。图 6为在 Simulink下利用 DSP Builder搭建的4阶FIR滤波器电路模型,该电路经SignalCompiler编译后即可生成HDL文件[5]。本设计中的FIR低通数字滤波器可以由多个4阶FIR滤波器级联而成,系数可以由Matlab生成。

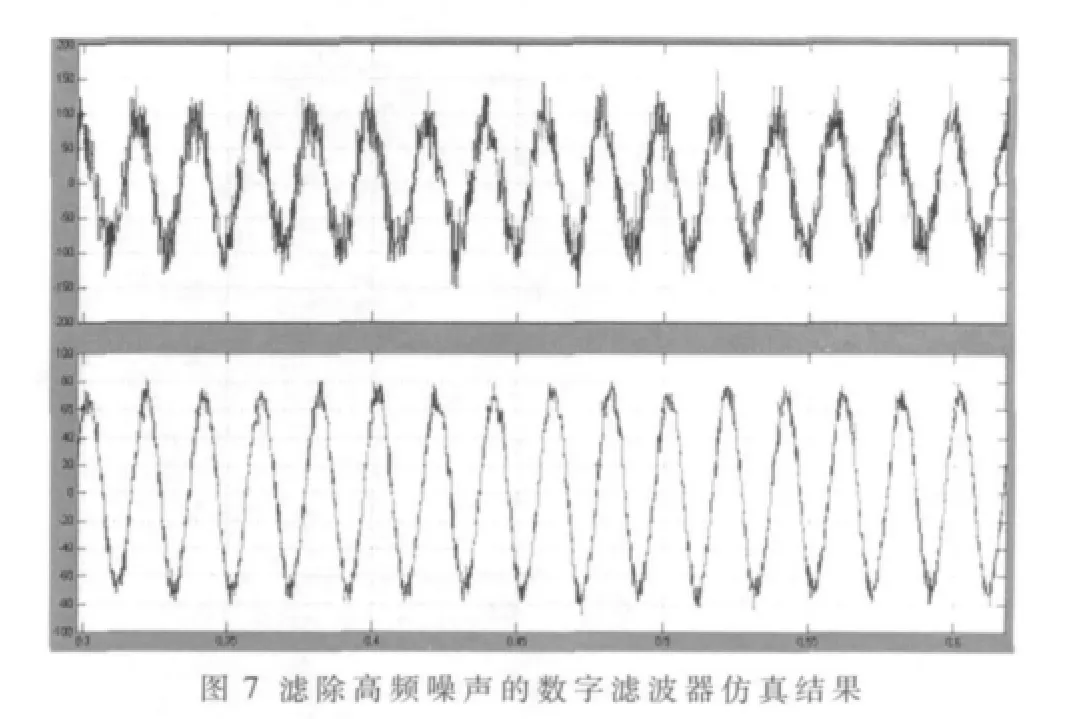

图7为附加高斯白噪声的正弦信号通过设计的FIR数字滤波器的仿真结果。从图中可以看出,该滤波器能够较好地去除高频分量,满足设计要求。

本文提出一种基于SoPC的数字化变电站计量仪表设计方案,系统在一片FPGA基础上构建,利用现代EDA设计工具采用自顶向下的方法进行设计。SoPC系统是计量仪表的工作核心,由三个模块构成:协议解析模块、数据处理模块和系统控制模块。采用SoPC技术,可以大大减少系统的元件数量,提高系统可靠性。由于SoPC系统的灵活性,可以在不改变外围硬件电路及印刷线路板的情况下对系统进行升级。

[1]高翔.数字化变电站应用技术[M].北京:中国电力出版社,2008.

[2]史运锋.基于NiosⅡ软核的嵌入式以太网设计[D].南京:南京理工大学,2009.

[3]王亮,陈文艺.基于 SoPC的嵌入式以太网LAN91C111控制器的开发应用[J].西安邮电学院学报,2010,15(3):96-100.

[4]Altera Corporation.DSP builder reference manual.2010.

[5]刘建成,邹应全,徐伟.基于 FPGA的FIR滤波器设计与仿真[J].南京信息工程大学学报:自然科学版,2010,2(5):400-404.