基于FPGA视频和图像处理系统的FIFO缓存技术

向厚振,张志杰,王 鹏

(中北大学 信息与通信工程学院,山西 太原030051)

近年来,基于FPGA硬件技术的视频图像处理系统被广泛地应用于视频智能监控、智能交通系统、视频采集、跟踪系统等。作为机器视觉的一个重要研究方向,动态目标检测在视频智能监控、智能交通系统等方面得到了越来越多的应用。动态目标检测是视频智能化系统的前提,其目的是从视频图像序列中将变化区域提取出来。对变化区域的有效提取对后续的目标分类、跟踪和行为理解等处理都非常重要[1-2]。

视频图像处理系统设计中,视频信号经过采集、缓存、处理、输出(显示或存储)。而缓存模块的设计取决于视频图像数据传输速率以及格式大小,根据国际电联定义的ITU-RBT.656数字图像接口标准[3],中国采用的是世界上大多数国家所采用的720×576分辨力的PAL制式视频信号,每帧数据由场消隐信号、行控制信号、有效视频数据组成,一帧图像大小为3 240 kbit(灰度数据)。在基于FPGA技术的视频和图像处理系统设计中,利用FPGA可配置逻辑资源设计一帧图像数据缓存单元的方法是行不通的,那么如何更好地利用FPGA芯片有限资源成为FPGA设计的难题。

本文基于Xilinx Vritex-4芯片的动态目标检测系统设计,合理利用芯片资源,以及根据系统动态检测设计帧间差分法更有效地完成系统设计,达到动态检测实时性的目的。

1 动态目标检测系统架构

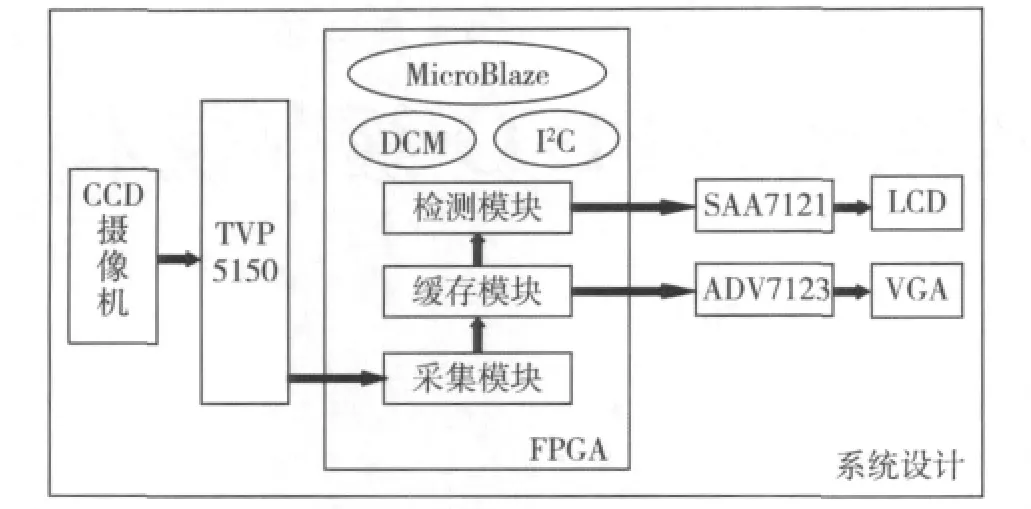

基于FPGA的动态目标检测系统分为视频采集模块、视频图像缓存模块、视频数据检测模块。系统硬件平台设计框架如图1所示,FPGA芯片接收由CCD摄像机采集到模拟视频信号经TVP5150解码芯片转换出来的数字视频信号,FPGA视频采集模块检测数字视频流当中的有效视频图像信号,经图像缓存模块缓冲,一路传输给检测模块进行算法处理,经SAA7121编码芯片转换输出LCD显示,一路直接还原为视频数据流信号,完善的系统显示模块还包括经ADV7123芯片转换输出到VGA显示器对比,以达到动态目标检测的可视化效果。此外,系统涉及到FPGA芯片与各个器件之间的硬件连接和通信协议,以及对FPGA内部的逻辑资源进行例化,包括MicroBlaze软核、IIC总线模块、DCM模块等[4-5]。

系统基于Xilinx Virtex-4芯片设计[6],其资源丰富,功能强大,内嵌1个32位的MicroBlaze软核,集成了10 240个逻辑单元(slice),128个DSP逻辑单元,4个数字时钟管理模块(DCM)。这些逻辑单元包含分布式RAM的容量高达160 kbit,块RAM的容量高达2 304 kbit。这些为视频流在FPGA芯片内部实现延时提供了缓存空间。DSP逻辑单元为视频数据流在片内进行运算和处理提供了计算能力上的支持。DCM模块为内部例化器件提供系统时钟信号。另外,DCM具有将信号差分、相移、倍频、分频等功能,这些都为系统外接器件提供了相应的时钟信号,使整个系统具有良好的扩展性。

图1 系统硬件平台设计

2 FIFO缓存与帧差法设计

动态目标检测图像数据缓存的难点在于数据容量大,速率与系统时钟不一致,以及视频图像数据的连续性。视频图像处理是以一帧图像数据进行算法处理为前提。经过解码模数转换后的720×576分辨力的一帧数字视频图像,包括色度信号Cb和Cr,以及亮度信号Y。一帧图像分奇数场和偶数场各288行,一行数据以色度信号Cb、亮度信号Y和色度信号Cr按2∶4∶2组成,共1 440个采样点。其中的Y数据流就是视频图像的灰度值数据流,也是人眼敏感的图像数据,通常图像处理的也是图像灰度值。

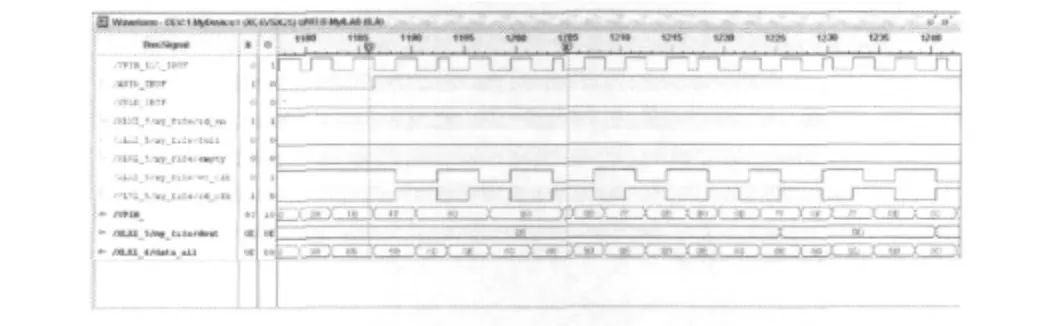

由解码芯片传输给FPGA芯片的视频信号是频率为27 MHz的亮度色度混合的数字信号VPIN。该系统利用VPIN_LLC分频时钟clk_675将亮度信号(灰度数据信号)单独提取出来写入FIFO做处理,但前提是要检测这些信号是否为视频有用信号。检测方式有两种,一种是通过解码芯片产生的AVID指示信号检测高低电平,从而判断输出数据是否为灰度数据或无效数据。AVID用来检测指示VPIN有效视频起始SAV信号和有效视频结束EAV信号,图2是通过在线逻辑分析仪ChipScope Pro得到的系统设计内部信号波形图。由图可知,AVID Start跳变指向的是VPIN有效数据起始SAV信号FF,00,00,C7,同样AVID Stop跳变指向的是EAV信号。另一种检测方法是通过可综合的VHDL程序代码写状态机FSM检测SAV,EAV信号。

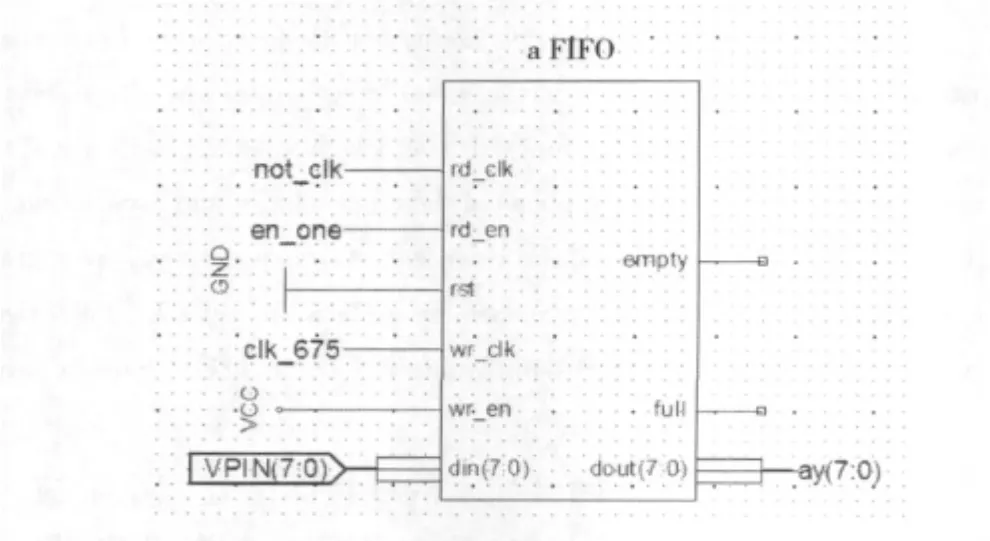

图3是系统部分设计原理图。设计中,a FIFO缓存VPIN当中有效灰度数据,b FIFO延迟a FIFO的输出数据。通过写时钟wr_clk控制数据输入,读使能rd_en、读时钟rd_clk控制数据输出。当clk_675上升沿到来时,a FIFO写入VPIN数据流有效数据当中的亮度信号Y,直到a FIFO写满半帧奇数场数据或偶数场数据,读使能en_one打开,读时钟not_clk上升沿时读出数据Y,此时a FIFO输出是第一帧的奇数场或是偶数场的Y值信号。Y值信号进入b FIFO缓存,相当于将Y值信号做了延迟,读使能开启输出Y信号。在系统时钟下,两个FIFO输出的ay,by则是VPIN第二帧、第一帧的奇数场或是偶数场的Y值信号,将两个输出做差法,可得出相邻两帧灰度值变化区域。

图2 ChipScope Pro Analyzer分析结果局部示意图

图3 ISE Schematic Symbol FIFO部分原理图

动态目标检测就是将视频图像序列中变化区域检测出来,这里通过相邻两帧之间做差,将差值通过阈值判断,得出像素变化区域,进而检测出动态目标。系统设计中,巧妙地根据帧差法、FIFO缓存达到系统检测的目的[7-8]。

3 ChipScope在线逻辑分析

系统设计中的解码编码芯片和A/D芯片均由FPGA芯片控制其工作状态,通过系统设计工具EDK和Platform Studio,对其内部寄存器以及I/O口的配置均由C语言编写实现。系统内部工作状态由内部资源实例化MicroBlaze软核、总线模块、DCM模块等实现芯片工作的时序性、稳定性。ISE工程实现系统逻辑处理功能,对视频图像序列进行动态检测。ChipScope在线逻辑分析仪调试查看系统搭建成功后内部信号或节点,包括嵌入式硬件和软处理器。如图4所示,系统搭建成功后,各个主要信号实时波形图。包括视频输入信号VPIN、缓存FIFO输出dout、系统输出信号data_all以及系统时钟VPIN_LLC、FIFO读写时钟。由波形可得出,在有效数据位时FIFO进行数据输入,写入一场数据后输出,data_all是系统将有效灰度数据经过检测模块处理后还原到视频序列后的信号,可输出LCD显示其动态检测效果。另外,将FIFO缓存输出信号直接还原到视频序列经ADV7123输出到VGA显示器[9],可观测实时视频图像,以便对比检测动态效果。

图4 Analyzer分析结果

4 小结

视频图像处理系统设计中,图像缓存可以让系统时序稳定,实时性更高。本文以动态目标检测系统设计中FIFO缓存与系统设计帧差法巧妙结合,以Xilinx Vritex-4芯片为处理器,TVP5150,SAA7121解码编码码芯片以及ADV7123转换芯片系统实现了对视频图像的动态检测。系统设计实时性高,稳定性好,其次以FPGA芯片为处理器的系统设计具有小型化、低功耗、开发周期短、投入少、芯片价格适中等优点。该系统设计可应用于基于FPGA的视频图像处理系统各类应用场合中,具有一定的扩展性和应用前景。

[1]郑世宝.智能视频监控技术与应用[J].电视技术,2009,33(1):95-97.

[2]程明洁.智能视频监控系统目标检测和跟踪技术分析[J].电视技术,2008,32(10):86-88.

[3]ITU-R BT 656,Digtal TV system[S].1995.

[4]田耕,胡彬,徐文波.Xilinx ISE Design Suite 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[5]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[6]XILINX.Virtex-4 FPGA data sheets[EB/OL].(2010-08-30)[2011-9-07].http://china.xilinx.com/.

[7]王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):38-41.

[8]熊璟,唐广,唐湘成,等.基于DDR IP核视频图像缓存的设计与实现[J].电视技术,2011,35(2):55-57.

[9]宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):51-53.