基于OMAP-L138处理器的AD模块设计

梁 龙,翟守忠,李富伟

(长沙矿山研究院, 湖南长沙 410012)

0 引言

2009年德州仪器(TI)推出了具有无与伦比连接选项和浮点功能的OMAP-L138处理器,它构建于工作频率为300 MHz的TMS320C6748处理器和ARM9处理器基础之上的双内核处理器,适用于全面外设接入;并且拥有很低的功耗,在不同使用情况下总功耗为440 mW,待机模式功耗为15 mW。但OMAP-L138处理器内部未集成模拟数字转换器(ADC),需外扩ADC芯片实现模拟信号的采集。

ADS8556是一款6路16位逐次逼近寄存器型(SAR)ADC,具有真正的双极输入。每路包含了采样保持电路,允许同时对多路模拟信号进行高速采集,其并行接口模式的数据速率高达630 kSPS,总线宽度8~16位可选;串行接口模式数据速率高达500 kSPS。ADS8556的工作电压±12 V,具有高达91.5 dB 的信噪比(SNR)。

1 系统总体框图设计

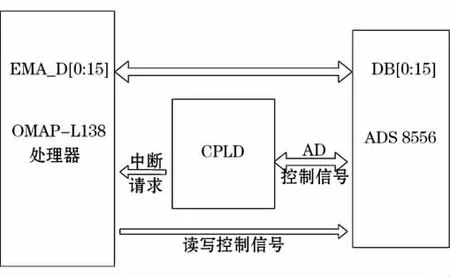

ADS8556利用OMAP-L138处理器的DSP端的外部存储器接口(EMIFA)实现6路模拟信号采集。输入通道分为3个组(分别为A0、A1,B0、B1,C0、C1),且每组可并行采集信号,每个通道的转换都由独立的转换开始信号控制。由于CPLD的时序严格,速度较快等优点,AD模块的控制信号选择用可编程器件CPLD XC95144编译产生,系统结构见图1。

2 硬件电路实现

2.1 电源模块设计

图1 系统总体框架

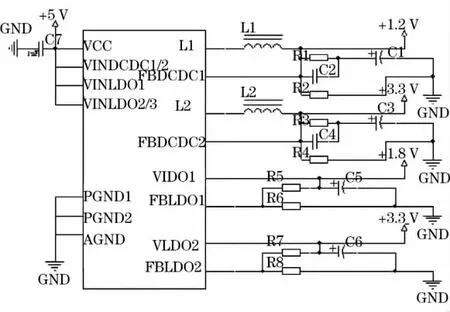

在电源电路设计方面,由于OMAP-L138处理器的DSP端内核电压为1.2 V,IO口电压为3.3 V。ADS8556需要4个独立的供电电源,分别为:5 V的ADC的模拟供电(AVDD)电压,用于ADC内部供电;3.3 V的数字IO接口的供电(BVDD)电压,用于驱动IO缓冲器;DSP内核电压1.2 V及±15 V模拟输入的高压供电(HVDD和HVSS)电压,由外部±15 V电源直接供电。选用TI的具有两个降压转换器和3个低输入电压LDO的5通道电源管理芯片TPS65053,最多可实现5路电压输出。设置其电压范围上限均为5 V,分别输出1.2 V、3.3 V、3.3 V_RTC及1.8 V(供给外围器件),如图2所示,降压转换器及3路LDOs的输入电压都连接到+5 V电压,并与地之间需接1 μF去耦电容。输出根据分压原理对R1~R8选择合适的电阻值。

2.2 ADC模块硬件接口电路设计

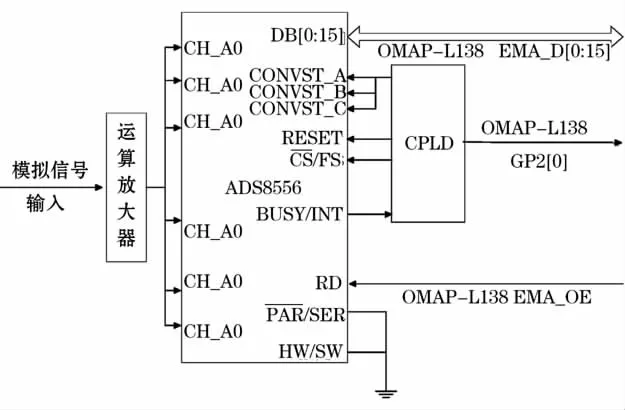

图3为基于ADS8556芯片的ADC模块硬件接口设计电路,其中将引脚PAR/SER和HW/SW置为低电平,实现并行模式下的信号采集;数据总线DB[0∶15]连接到处理器OMAP-L138的EMIFA数据端,实现数字转换结果的输出;BUSY/INT作为AD中断信号经 CPLD输出到 OMAP-L138的GPIO口,实现对模拟信号采集的控制;ADS8556使能内部参考电压源,对每一路信号提供缓冲参考电压。

图2 电源供电原理

图3 AD模块接口电路

3 软件设计

3.1 唤醒程序

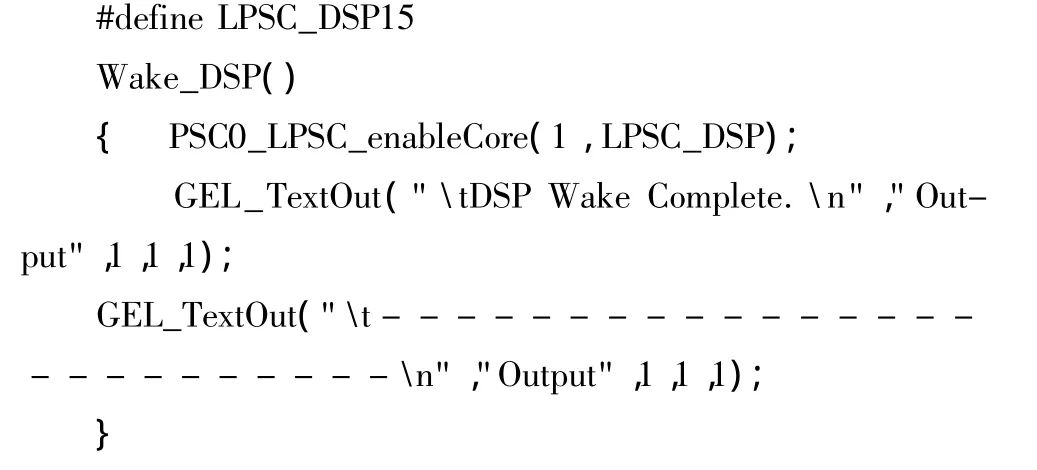

设计OMAP-L138作为一种快速、低功耗的处理器,由于其特殊的结构,DSP端必须在需要时由ARM唤醒,通常DSP端处于睡眠状态。所以,首先要编写一段链接程序从ARM端唤醒DSP。OMAP-L138处理器具有统一的管理外设和CPU供电的模块(PSC模块),PSC0的PD1用来控制DSP的L1和L2存储器的休眠状态。唤醒子程序如下:

其中PSC0_LPSC_enableCore为LPSC中使能DSP的子函数,即给DSP上电。

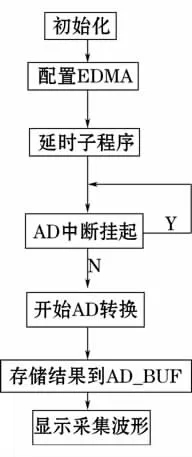

3.2 主程序设计

对AD采样使用中断控制方式,在编写中断控制子程序之前需配置相应的中断控制寄存器及处理器对应引脚的功能。具体软件模块如下。

(1)初始化模块,OMAPL138_init;OMAPL138RAM_init;EMIFA_init;AD_init。其中 OMAPL138的初始化实现Power and Sleep控制器的设置及时钟的配置;RAM初始化模块实现SDRAM的初始化及其上电,时钟的配置;EMIFA初始化配置了AD模块数据总线与地址总线及相关的控制总线;AD模块初始化开启AD中断,等待中断信号。

(2)EDMA3配置模块(DMAconfig)。将GP2[0]作为DSP对AD中断信号的接受端,则GPIO中断使能寄存器BINTEN的bit2=1;使能GP2[0∶15]的中断请求信号,复位相关寄存器。

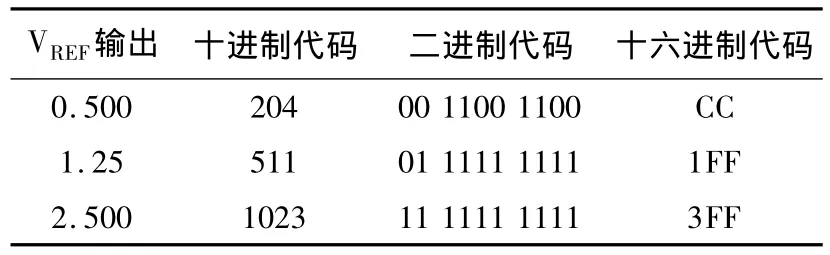

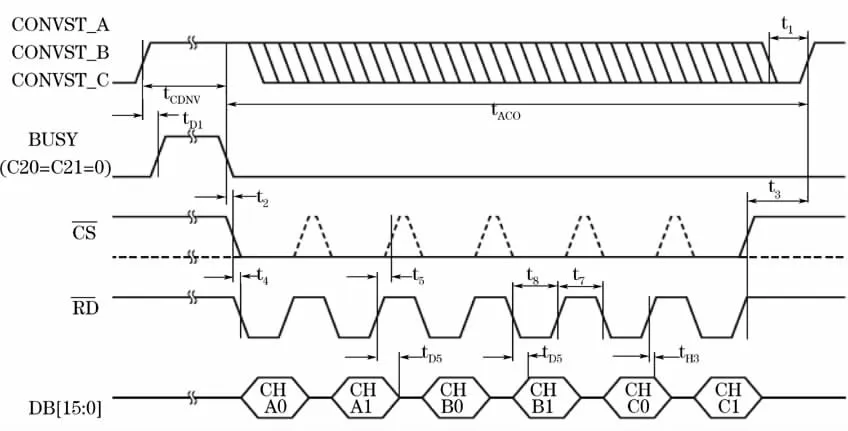

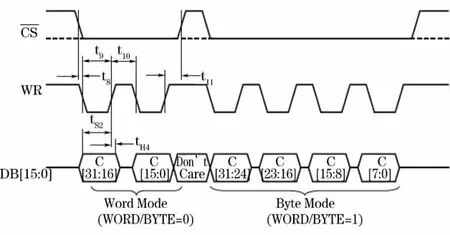

(3)AD测试模块(TEST_ad),将参考电压选为2.5 V,其 CR(控制寄存器)默认为 0x000003FF,如表1所示。并行接口模式下控制寄存器的改变在WR的上升沿有效。并行接口模式下从模拟通道读数据和给CR控制寄存器写入数据的时序逻辑如图4和图5。ADS8556在整个转换周期中CONVST_x应当始终保持为高电平,且每个通道组的模拟输入在对应的CONVST_x信号的上升沿保持,在读模式下,片选端CS为低电平时,在RD每个下降沿开始读取数据,6个周期读取6通道的数据。在写模式下,以字方式写入时,在每个WR的下降沿先写入高16 位(C[31∶16]),再写入低 16 位(C[15∶0]),在WR信号的2个周期内完成;当以字节方式写入,在每个WR的下降沿写入8字节,完成一次写入需要4个周期。

表1 DAC设置(2.5 V)

测试程序流程如图6所示。

4 试验结果及分析

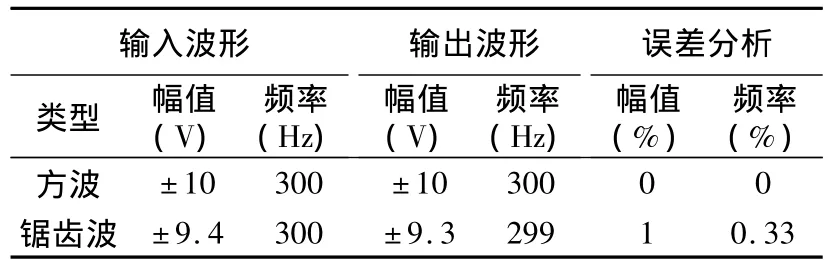

通过实验,当输入为300 Hz、±10 V的方波和锯齿波信号时,其幅值误差在±0.1 V范围内,频率误差在±1 Hz范围内,具体见表2。

图4 并行模式读时序

图5 并行模式写时序

图6 程序流程

用集成ARM与DSP的双核处理器OMAP-L138和多通道A/D转换器ADS8556组成了并行AD转换功能模块,采样速度快(最高可达630 ksps),实时性能好,精确度高(与实际模拟信号幅值误差1%,频率误差0.3%),并且可完成多路模拟信号的同时采集。

表2 试验结果及分析

[1]Texas Instruments.OMAP - L138 data sheet[Z].June 2009.

[2]Texas Instruments.ADS8556 data sheet[Z].August 2009.

[3]Texas Instruments.TMS320C674x DSP Cache[Z].February 2009.

[4]谷重阳,汪 渤,龙殊颖.并行模数转换器 ADS8364与TMS320F2812 的接口设计[J].微计算机信息,2006,(1).

[5]张雄伟,陈 亮,徐光辉.DSP芯片的原理与开发应用(第3版)[M].北京:电子工业出版社,2003.