基于ARM11+FPGA的多路视频监控系统关键技术研究

胡健生,张 倩,蔡艳军

(1.武警工程学院,陕西 西安 710086;2.武警西安指挥学院,陕西 西安 710038)

责任编辑:任健男

0 引言

在视频监控领域,数字化、多路化、高分辨力和小型化应经成为一种趋势,实时动态视频采集和传输已经成为一种趋势,已经成为信息和计算机领域的研究热点。目前,常见的设计方案主要有4种:1)基于专用的视频采集卡的方案,该方案的缺点是只能进行上层的应用软件开发,不能对其硬件电路进行更改,体积大,成本高,不适合嵌入式应用领域[1];2)基于专用的多媒体嵌入式处理器的方案,该方案的缺点是每路视频采集都需要独立的视频编码解码芯片和处理器,进行多路视频采集时有局限性,浪费了大量的处理器资源[2];3)基于FPGA的方案,FPGA主要面向逻辑控制和时序控制,可实现多路视频信号的采集,但是要实现视频信号的编码相对困难[3-4];4)基于DSP技术的方案,该方案设计灵活,但是不适合进行上层应用程序的开发,且设计复杂、开发周期长、成本高[5-6]。

1 系统总体结构

系统主要有4个部分组成:1)多路模拟视频输入单元,由4个模拟摄像机组成;2)多路视频信号采集单元,由 FPGA 芯片、4片视频解码芯片(SAA7111)、2片SRAM、时钟源和配置电路组成,完成对4路模拟视频信号的采集、存储和整合,并以BT.656格式的视频信号输出到下一个单元;3)视频信号压缩编码和传输单元,由ARM11高性能处理器(S3C6410)、外围存储器、以太网模块等组成,利用Camera IF接收整合后的多路视频信号,在MFC模块中对输入的视频信号进行H.264压缩,并通过IP网络发送到远程监控端;4)远程监控单元,一方面可以显示远端采集的视频信号,另一方面,也可以用于控制远端多路视频采集系统,如视频矩阵的切换和云台控制等。整个系统组成如图1所示。多路视频信号采集单元和视频信号压缩编码和传输单元是系统的核心,在设计时需要解决以下问题:1)多路视频信号的时钟同步;2)多路视频信号数据的储存;3)FPGA与ARM11数据接口的实现;4)对视频数据的压缩编码。

2 关键技术研究

2.1 多路视频信号的时钟同步

图1 系统组成框图

FPGA通过I2C总线,对4片SAA7111进行工作模型、输入端口、色彩控制和输出格式等图像采集的控制参数进行配置,以上参数中较重要的是输出数据格式。SAA7111支持的输出数据格式有411(12 bit)、422(15 bit)、CCIR-656(8 bit)、RGB(16 bit)和 RGB(24 bit),为了便于与后续单元的数据传输和对视频数据的压缩编码,这里将SAA7111输出的数据格式配置成CCIR-656(8 bit)。该接口使用8 bit的复合YUV数据和27 MHz的时钟,分辨力是720×576,不需要使用传统的视频时序信号(HSYNC,VSYNC和BLANK),将时序代码嵌入到视频流中,可以减少芯片接口的引脚数量[7]。

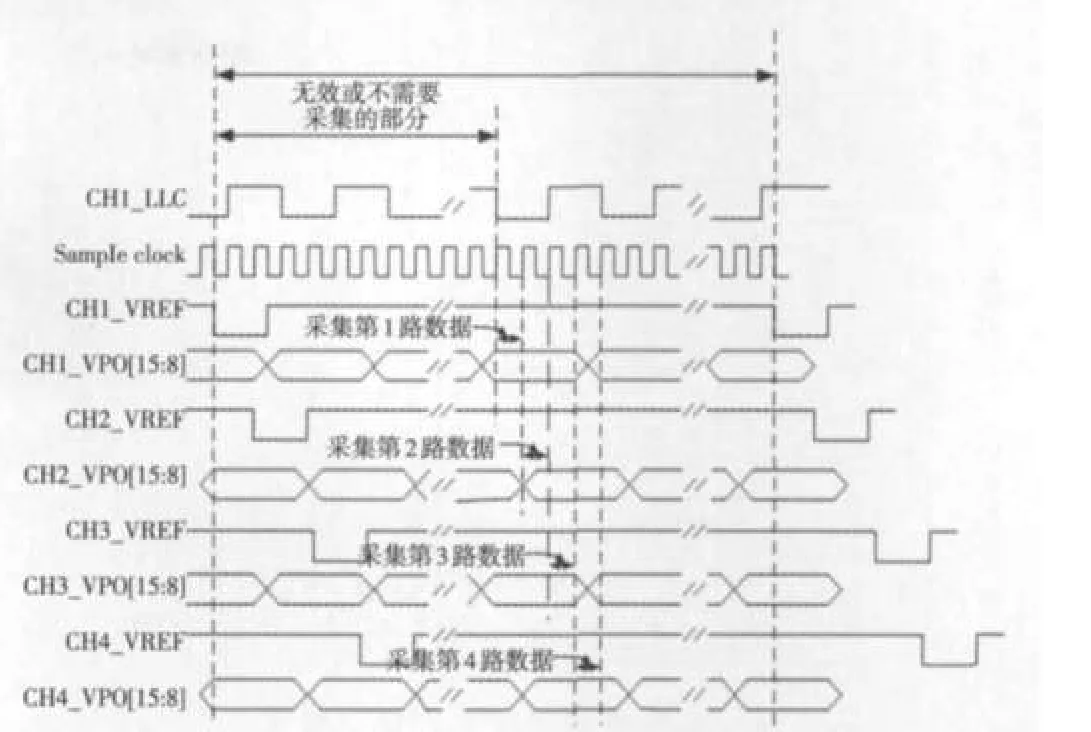

由于4片SAA7111在工作时是不同步的,每次上电后输出的时钟和数据都具有不确定性,而最终采集到的4路视频数据要求存储在同一显示缓存中的相应位置处,因此必须要对4片SAA7111输出的视频信号进行同步。利用FPGA内部的锁相环模块,对任意一路(这里不妨设成第1路)SAA7111的输出像素时钟信号LLC(27 MHz)进行4倍频,生成采样时钟信号sample_clock(108 MHz),这样在4个sample_clock周期内刚好完成对每路视频信号的1次采集;以第1路SAA7111输出的帧同步信号(VREF1)为基准,当其输出第1个需要采集的像素点时,开始进行采样,这样又可以在1个帧周期内,完成对4路视频信号中所有需要的像素点的采样。采集时序如图2所示。

2.2 对多路视频数据的缓存

系统中的FPGA需要先对4片SAA7111采集到的有效数据进行缓存,然后通过以BY.656视频格式将数据发送给ARM11,进行编码处理,此过程存在以下3个问题需要解决:1)显示缓存是16 bit的SRAM,而BT.656视频格式的数据是8 bit,因此不能直接将采集到的视频信号存储到SRAM中,也不能直接将SRAM中的数据读出发送给ARM11;2)为了保证视频数据传输的高时效性,FP⁃GA必须将缓存SRAM中的数据及时读出,发送给ARM11,因此存在FPGA向SRAM中同时读写数据的冲突问题;3)FPGA对4路视频数据采集的时钟sam⁃ple_clock频率为108 MHz,BT.656视频格式的时钟频率为27 MHz,而FPGA读写SRAM也有严格的时序要求,因此需要合理解决FPGA读写SRAM时钟、FPGA采集数据时钟和BT.656视频时钟之间的同步。这里,使用FIFO电路和读写SRAM时分复用机制,解决上述问题。

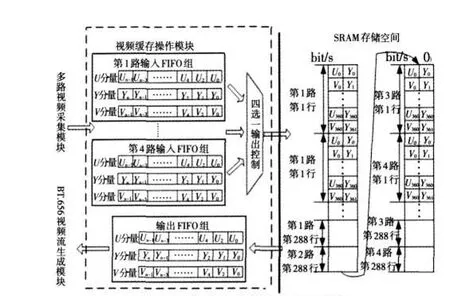

图2 多路视频信号同步

在视频缓存操作模块中,对于与多路视频采集模块相连的输入端,设置4组输入FIFO组,分别缓存采集到的4路视频数据;每组FIFO又由3个队列,分别缓存Y,U,V分量。通过四选一控制器,判断选择相应的FIFO组中的数据。每对SRAM进行1次写操作,都要读取某路FIFO组中的U队列(或V队列)和Y队列中的数据各1次,共16 bit的数据,存储到SRAM中的1个单元中。对于与BT.656视频流生成模块相连的输出端,需要设置一组输出FIFO组,同样也由分别缓存Y,U,V分量的队列组成。每对SRAM进行一次读操作,将数据的高8 bit放置在U(V)队列中,将低8 bit放置在Y队列中。这里需要说明的是,由于U,Y和V分量是同步的,因此每个FIFO组的3个FIFO队列的“满”或“空”状态也是同步的,程序设计时使用任意一个队列的状态信号即可。对多路视频信号的缓存过程,如图3所示。

系统采用的“读写SRAM时分复用机制”,就是根据以FPGA内部主时钟master_clk为基准,根据对多路视频信号的采集、BT.656视频格式、读写SRAM三者的时序要求,按照一定的时间间隔,分时对SRAM进行读操作和写操作,不仅解决了一片SRAM作为视频数据缓存所存在的读写冲突问题,也解决了上述3个时序信号的同步问题。读写SRAM的时分复用原理如图4所示。

图3 对多路视频信号的缓存原理

图4 读写SRAM的时分复用原理

对第1路SAA7111的LLC(27 MHz)进行8倍频,得到FPGA工作的主时钟mater_clk(216 MHz)。以mas⁃ter_clk为基准时钟,以其下降沿为触发条件,根据输入FIFO组的“空”标志信号和输出FIFO的“满”标志信号的状态,进行SRAM读写状态的判定。以对读SRAM操作的判定为例,原则如下:当master_clk下降沿第一次到来时,master_clk应为高电平(sram_r/w初始状态为0),FP⁃GA进入读操作判断状态(r0)。若输出FIFO组非满,表明可以从SRAM中读取数据,在接下来的3个主时钟周期里,依次跳转到r1,r2,r3和r4这4个状态,完成1次读SRAM操作;若显示数据输出模块中的FIFO电路满,则不能再对SRAM进行读操作,在接下来的3个主时钟周期内,依次跳转到r4,r5和r6这3个状态,在这4个状态里不对SRAM进行任何操作,仅起到延时作用。对写SRAM操作的进行判定时,则参考输入FIFO组的“空”标识信号状态为依据。这样,经过上述r0→r1→r2→r3(或r0→r4→r5→r6)→w0→w1→w2→w3(或 w0→w4→w5→w6)→r0共8个状态的切换,刚好是1个LLC信号或BT.656视频时钟信号周期,完成对SRAM的读写操作各1次。

2.3 FPGA与ARM11数据接口的实现

为了能对采集后的多路视频信号进行压缩编码,FP⁃GA要将显示缓存(SRAM)中的视频数据以BT.656格式输出,因为SAA7111输出的数据格式应经配置成YUV 656(8 bit),因此这里需要再次生成BT.656视频的时序信号,将视频缓存操作模块中的输出FIFO中的数据读出即可。

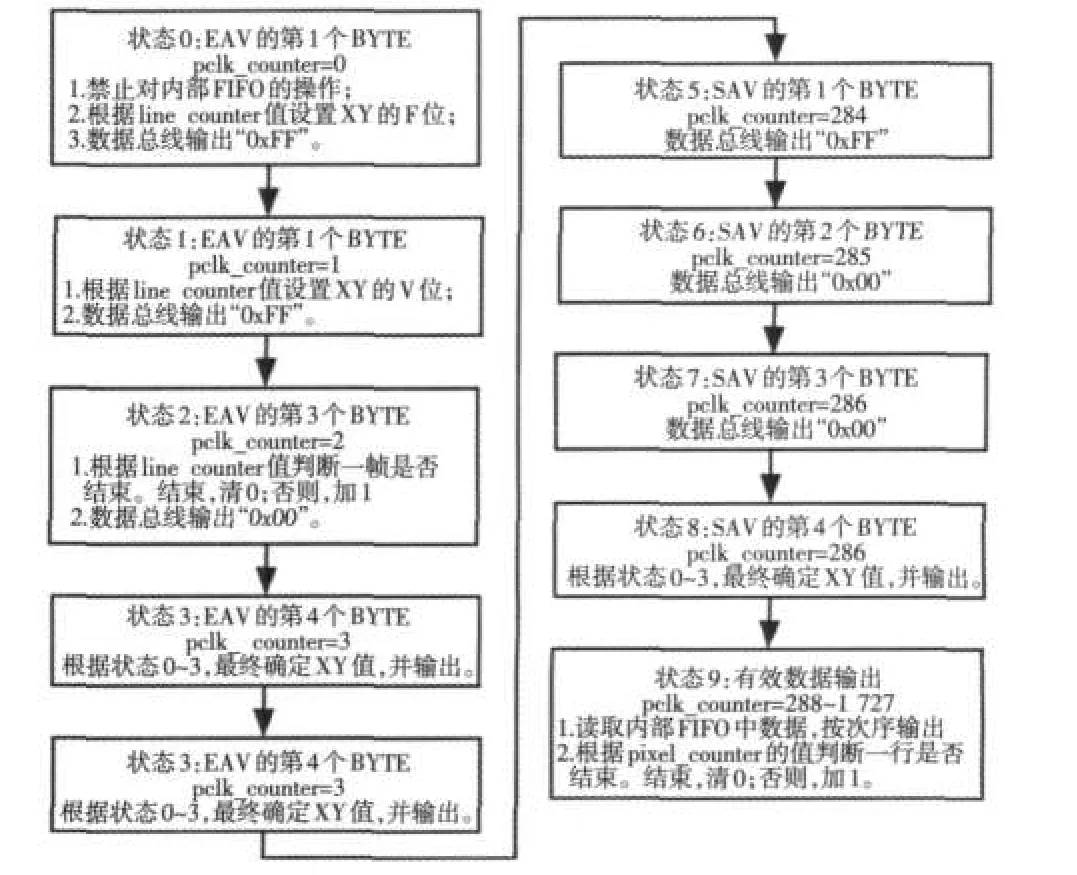

选用20 MHz的外部时钟源,利用FPGA内部锁相环生成系统的主时钟27 MHz,即BT.656视频标准的像素时钟频率。在设计视频时序信号时,设置一个20 bit像素时钟计数器的(pclk_counter),对像素时钟信号(pclk)进行计数;设置一个4 bit的状态转移标识变量status,根据pclk_counter的值确定状态值,在10个状态之间进行切换;设置一个10 bit的行计数器(line_counter),对输出视频的行进行计数。BT.656视频时序信号生成的状态转移如图5所示。

图5 时序控制代码产生的状态转移过程

2.4 视频信号的压缩编码

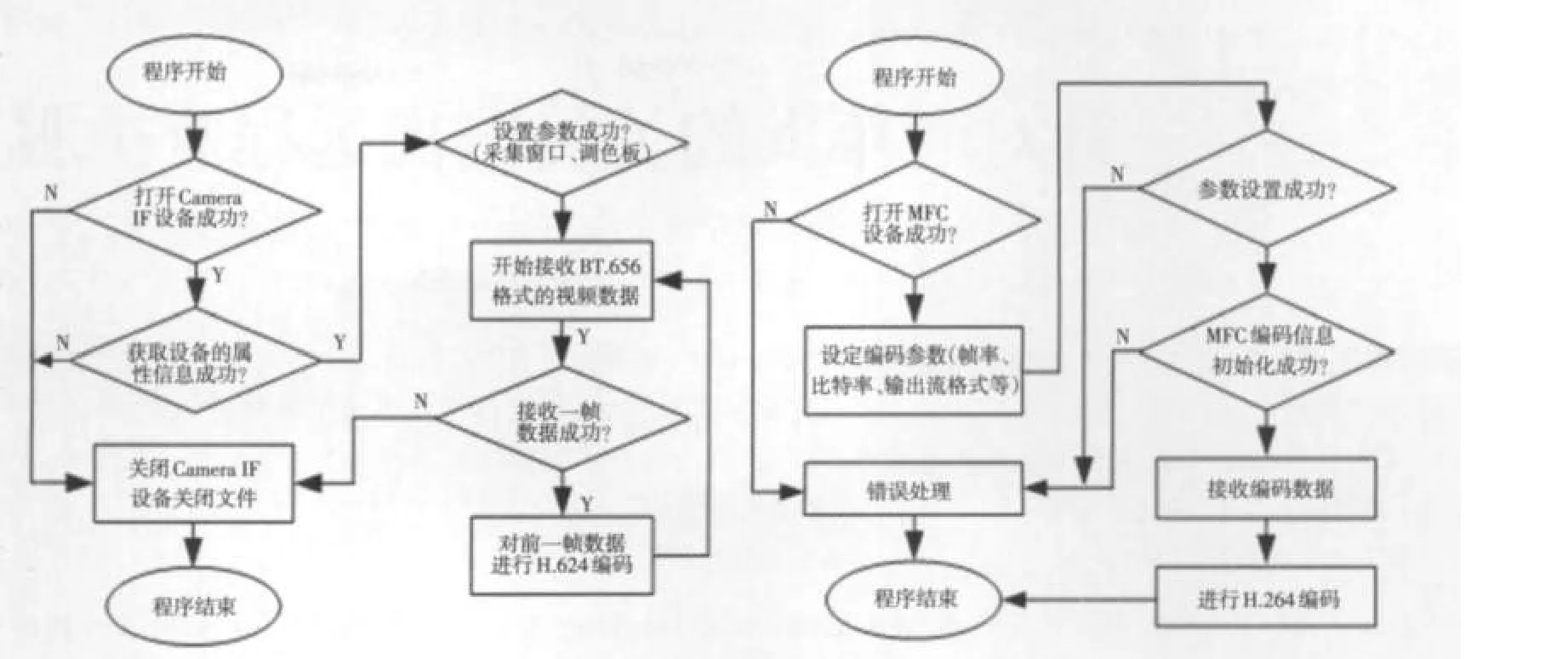

系统的ARM处理器S3C6410,内部集成的多媒体编解码器(MFC)支持MPEG4/H.263/H.264的编码与解码,并支持VC1解码,性能可以达到全双工30 f/s@640×480同时编解码和半双工30 f/s@720×480或25 f/s@720×576编解码。同时,自带摄像头接口(Camera IF),可以支持ITU R BT-601/656 YUV 8 bit标准的视频数据,支持90°旋转功能,有2个DMA输出通道,1个与其显示控制器相连,用于本地显示,1个与MFC相连,用于视频数据的编解码后续处理[8]。系统所使用的处理器S3C6410的生产厂商三星公司已经提供了相应的操作系统s3c-linux-2.6.21的源码,以及摄像头模块、MFC和网络设备的驱动源码,在此只须对操作系统内核各功能模块进行剪裁,再创建镜像文件即可,具体方法不再赘述。

图6 处理器接收视频数据及编码流程

ARM处理器接收视频数据及编码过程的如图6所示。S3C6410利用Camera IF接口接收FPGA采集到的多路视频信号,将FPGA作为一个设备文件映射到内存中,绕过了内核缓冲区,进程可以像访问普通内存一样对文件进行访问,同时还可采用了双缓存的思想设计,加快了视频数据的读写速度。同样,加载了MFC驱动之后,可以像操作普通文件一样调用MFC函数对视频数据进行H.264编码。最后,经编码后的视频数据,通过系统的网络接口进行远程传输,远端监控主机利用一般的视频解码软件进行解码即可。

3 结论

系统基于ARM11和FPGA实时对多路视频信号进行采集、编码和传输,实现了多路视频监控功能,测试采集传输VGA的图像可达到25 f/s,图像经过H.264编码后平均每帧只有12 kbit左右,占用网络宽带很少,传输图像清晰稳定,具有很强的实用性和广阔的应用前景。

[1]雷刚勇.多路视频远程监控系统(客户端)的设计与实现[D].西安:西安电子科技大学,2006.

[2]姚琳.安防监控热门方案评价[J].电子设计技术,2009(4):87-95.

[3]周鑫,何建新,李学华.门禁系统视频监控电路设计[J].微计算机信息,2009,25(1):310-312.

[4]胡健生,臧晓昱.嵌入式多路视频采集显示系统设计[J].液晶与显示,2010,25(6):831-835.

[5]梁修如,严国萍.嵌入式视频监控服务器系统典型方案及其性能分析[J].电视技术,2005,29(10):93-96.

[6]席鑫宁,潘宏侠.基于DSP的LCD模块设计及其设备状态监控系统中的应用[J].液晶与显示,2009,24(1):110-115.

[7]Intersil Corporation.BT.656 video interface for ICs application note[EB/OL].[2011-03-27].http://www.datasheet.net/document/app-note BT.656%20Video%20Interface%20for%20Ics?id=1767350.

[8]Samsung Electronics,Inc.S3C6410 user’s manual[EB/OL[2011-03-27].http://www.google.com.hk/url?sa=t&source=web&cd=&ved=0CC⁃MQFjAA&url=http%3A%2F%2Fwww.hhcn.com%2Fchinese%2Ffiles%2Fs3c6400_rev15.pdf&rct=j&q=S3C6410%20USER%E2%80% 99S% 20MANUAL&ei=tomeTtqdMNCciAfEp7WvCQ&usg=AFQjCNFW2ETBGvJcJG0poQdh7sCPLMO5tg&cad=rjt.