自适应数字频率计教学课题的设计

汪小会

(解放军电子工程学院,安徽合肥 230037)

本文介绍了一种基于FPGA的自适应数字频率计的设计方案。它以数字电子技术和可编程逻辑器件的控制原理为切入点,贯穿了数据选择器、触发器、计数器和锁存器等功能器件的基本原理和应用方法。设计方案在FPGA器件上实现,采用图形输入方式,由数字电子技术课程介绍的基本模块构成。

现有资料介绍自适应数字频率计设计方法,大多采用VHDL设计[1]。但是,掌握VHDL设计要用较多时间,且本科生教学设计课题成功率较低,如果用数字逻辑电路和可编程逻辑器件FPGA设计,通常可以完成课题设计任务。

1 数字频率计测量原理及系统框图

数字频率计是直接用十进制数字来显示被测信号频率的一种测量装置[2]。对于非矩形波信号测量时需先进行处理,整形变换成幅度为5V的矩形波。本文讨论对矩形波信号基本测量频率为10kHz(显示四位十进制数)和扩大10倍量程信号频率即100kHz测量。

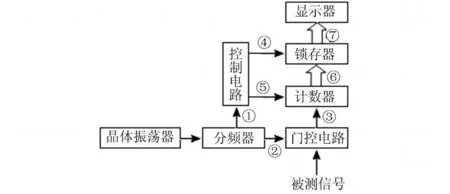

本系统由脉冲输入电路、控制电路(由FPGA构成)和输出显示电路组成。控制的核心芯片是FPGA,它由两大功能模块组成:①频率计数模块,包含选通时间控制部分和计数两个部分。②显示模块。如图1所示。

该系统的工作原理是:被测信号经门控电路整形生成矩形波,输入到控制核心芯片FPGA的计数模块,计数器根据矩形波上升计数。计数时间则由选通时间控制电路决定,可根据频率所处的范围来决定档位。最后将计数的结果给显示电路,在数码管上显示频率。

图1 基本测频系统总体框图

2 电路设计方案

本课题在FPGA的开发环境QuartusⅡ中进行,学生使用逻辑符号设计方式[3]。在QuartusⅡ图形文件编辑过程中,输入器件型号即可调出所需器件。由于QuartusⅡ的基本元件库几乎囊括了所有中规模集成器件,QuartusⅡ还具有兆功能函数库中的参数化模块,含有所有基本数字逻辑功能器件。这些参数化功能模块的输入、输出以及各种控制方式都可由用户设定。学生的设计基本不受器件资源的限制,能够实现真正意义上的自主设计。

1)电路实现方案

本文是以一个闸门信号低电产控制被测信号通过门控电路。通过门控的信号由计数器来统计,闸门信号一个周期内完成一次信号数量统计,同时刷新一次显示数码,即闸门信号选通结束时将计数器内数码转移到锁存器,锁存器内数码作为显示状态。其后清除计数器内数据。故电路中需要有控制电路产生锁存器锁存控制信号(图1中④)和计数器清零信号(图1中⑤)。

2)计数器与锁存器

计数器为同步型(10000)10进制加法计数器,锁存器(图1中⑥)由2片74373锁存4片74160十六位二进制数码组成[4]。

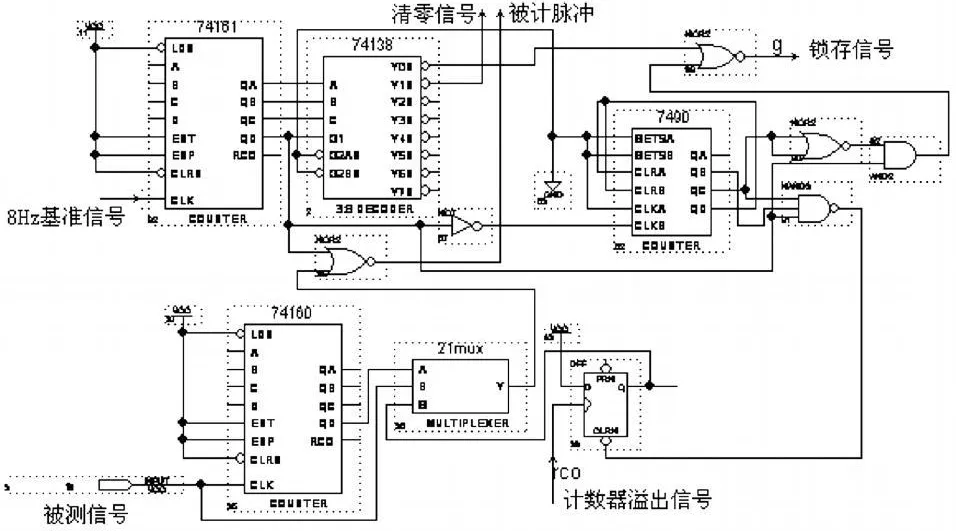

3)闸门信号和控制信号

将晶体振荡器信号分频产生一个正脉冲或负脉冲(本文以负脉冲)宽度为1秒的信号(图1中②)作为闸门信号(图2中74161输出QD)。晶体振荡器分频中产生另一个8Hz信号(图1中①)作为计数器74161时钟信号。74161输出用74138译码产生锁存控制信号g和计数器清零信号(图2中74138输出Y1N)。

4)溢出信号产生电路

计数器在闸门信号选通期若最高位数码由1变0(即下降沿)就说明所测信号超出范围,这时产生一个信号(图2中DFF输出Q)为1,用此信号去控制图2的二选一数据选择器。有溢出时将测信号十分频(图 2中74160)后作为待测信号,把图 4中DFF输出Q信号用作指示灯示意被测信号进行了十分频,或用于控制显示的数码管小数点。

图2 闸门信号和控制信号产生电路

在闸门信号选通期如有溢出在本周期内计数器统计的脉冲数目并非是实际信号数目,所以此时计数器状态不进行锁存即不显示,在下一个闸门信号周期才锁计数器状态即显示,再下一个周期应将溢出信号完成清除(置0)。图2中在7490右边电路就是为此目的设计所用。

5)更大范围测频设计

可将上面的计数溢出信号进行计数,判定是否溢出,其后对被测信号进行十分频。类似进行上面处理及控制数码管该点亮的小数点及单位符号。

最后编程下载至FPGA,经测试测量矩形波信号基本档误差±1Hz,扩张档误差±10Hz。

3 结语

本课题是笔者多年从事数字逻辑电路和可编程器件开发应用教学多个课题中一个典型代表,其综合知识范围广,设计思想新颖,十分适合用于教学实验。本课题设计是采用原理图输入法完成,部分模块还可采用硬件描述语言法来做。数码的显示还可用动态数码管显示,如果这样做可提高学生对各种知识综合运用能力的提高。

[1] 杨刚,龙海燕.现代电子技术-VHDL与数字系统设计[M].北京:电子工业出版社,2004

[2] 黄正瑾.CPLD系统技术设计入门与应用[M].北京:电子工业出版社,2002

[3] 赵曙光.可编程逻辑器件原理、开发与应用[M].西安:西安电子科技大学出版社,2006

[4] 中国集成电路大全[M].国防工业出版社,2000