基于ADV7125的嵌入式系统VGA接口设计

郑佃好,张红雨,张洪斌

(电子科技大学电子工程学院,成都611731)

郑佃好(硕士研究生),主要研究领域为嵌入式系统设计、射频识别、模糊控制。

引 言

目前VGA接口是计算机系统以及智能仪器中重要的标准输出接口,但是大部分硬件系统选择LCD终端输出。很多显示设备,如常见的CRT或LCD显示器一般都采用统一的15针VGA显示接口。如需要外接这些设备,则需要把LCD输出信号的接口转换为VGA接口。本设计是在三星公司芯片 S3C2440平台下,利用最高频率可以达到330 MHz的ADV7125芯片,设计了能够把输出的LCD信号转换为VGA信号的转换电路。该设计方案具有电路简单、价格低廉、输出图像清晰稳定等特点。

1 ADV7125芯片介绍

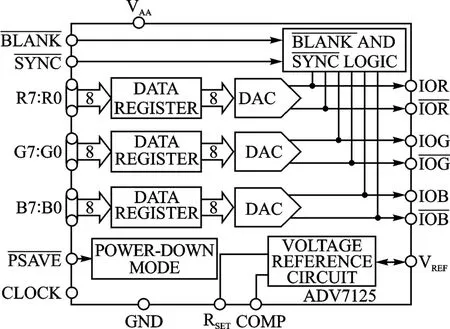

ADV7125是一款单芯片、3通道、高速度的数模转换器。内置3个高速、8位、带互补输出的视频DAC、1个标准TTL输入接口,以及1个高阻抗、模拟输出电流源。它具有3个独立的8位宽输入端口。只需1个+5 V/+3.3 V单电源和时钟便能工作。ADV7125还具有其他视频控制信号:复合同步信号控制端消隐信号控制端以及省电模式控制端。它能够与各种高分辨率彩色图形系统兼容[1]。ADV7125功能框图如图1所示。

ADV7125有3个视频数据寄存器DATA REGISTER和一个视频控制寄存器POWER-DOWN MODE。数据寄存器的3个输入端分别连接红绿蓝三色的数字视频信号,数据寄存器后面紧跟数模转换单元,将数字信号转换为模拟信号;控制寄存器将数字的消隐信号、同步信号转换合并。数模转换后的模拟视频信号和控制寄存器输出的同步、消隐控制信号共同作为ADV7125的输出信号,此输出信号大小受Rset端和地之间接入的外加电阻RSET大小的控制。

图1 ADV7125功能框图

2 ADV7125芯片用于VGA转换的基本原理

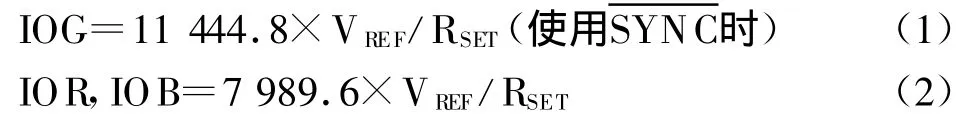

ADV7125芯片用于VGA转换的基本原理是,将S3C2440输出的数字视频信号转换为模拟的VGA输出信号,模拟的VGA输出信号的大小受ADV7125芯片外围参考电压VREF和外加电阻 RSET的控制,(VREF和 RSET的具体接法如图4所示)其关系如下:

式中IOG、IOR、IOB分别代表绿、红、蓝三色信号的幅度。当不用复合同步信号时,需要把端连接低电平,这时IOG的关系式同式(2)。

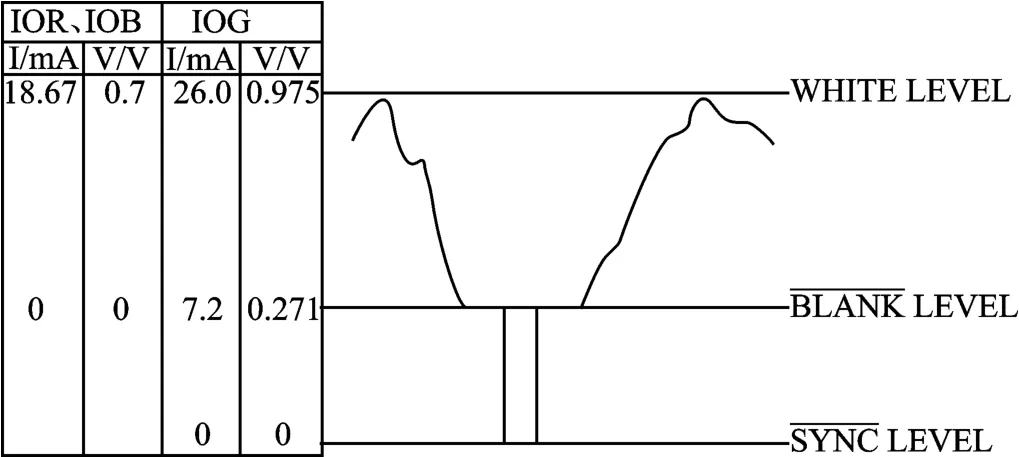

图2 ADV7125的端 对输出视频信号的影响

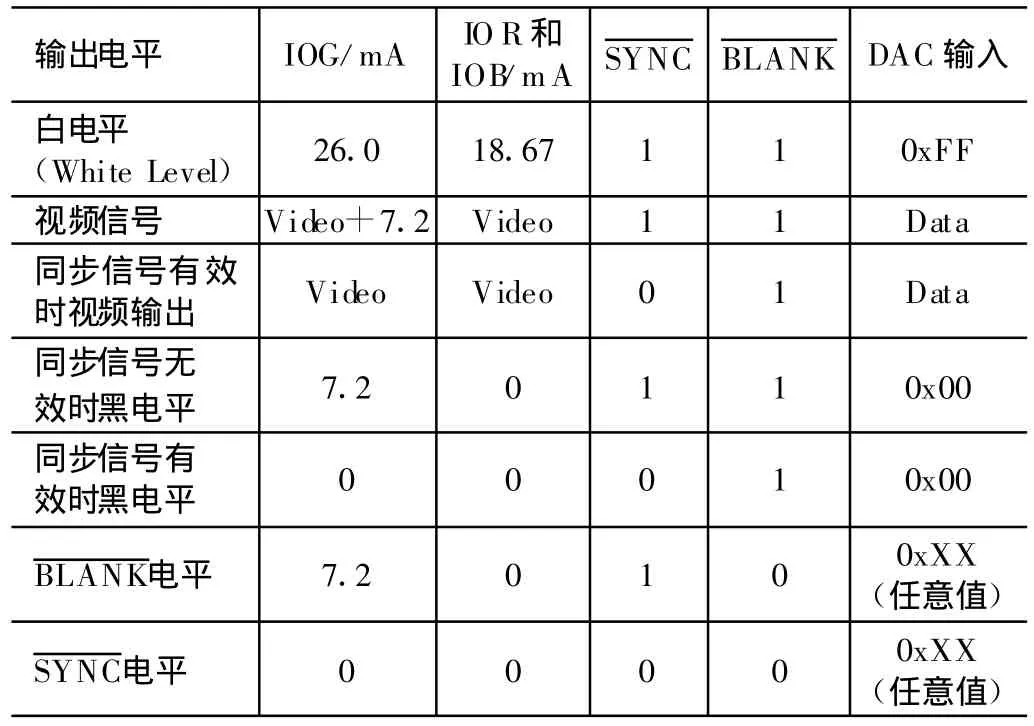

表1 典型的视频输出真值表

对应图2和表1可得到以下结论:

①当IOR、IOG 、IOB三端的DAC输入为0x00时,代表屏幕最黑,此时对应图2为对应表1为第7行。从图2左面列表可以看到,IOR、IOB端的电流、电压分别是0mA、0V,IOG端的电流、电压分别是7.2 mA、0.271 V。即电流相差7.2 mA。

②当IOR、IOG、IOB三端的DAC输入为0xFF时,代表屏幕最白,此时对应图2为WHITE LEVEL,对应表1为第2行。从图2左面列表可以看到,IOR、IOB端的电流、电压分别是18.67 mA、0.7 V,IOG端的电流、电压分别是26.0 mA、0.975 V。即电流相差7.3 mA。

从表1,可以得到以下的结论:

面对这种情况,依托学校资源,由不同所有制经济主体共同出资成立独立经济实体,实现决策、培养、评价、改进的混合所有制经济,应该是一种不错的校企合作培训模式。它突破了合作方各自为政的教育模式,实现了从理念、决策、培养方案到资源调配的统一,有利于校企合作培养模式的质量升级。

3 VGA接口设计

根据需要,把LCD信号转换为VGA信号,转换时必须根据VGA信号的时序进行转换。VGA信号一共包括5部分,分别是红(R)、绿(G)、蓝(B)三色信号和行(H)、场(V)同步信号,红(R)、绿(G)、蓝(B)三色信号和行(H)、场(V)同步信号根据S3C2440的配置时序,由S3C2440以数字信号的形式输出,之后由ADV7125对红(R)、绿(G)、蓝(B)三色信号进行转换,行(H)、场(V)同步信号直接进入VGA接口中,不需要转换。下面分别介绍VGA信号的时序、硬件连接、软件设计以及注意事项。

3.1 VGA时序信号

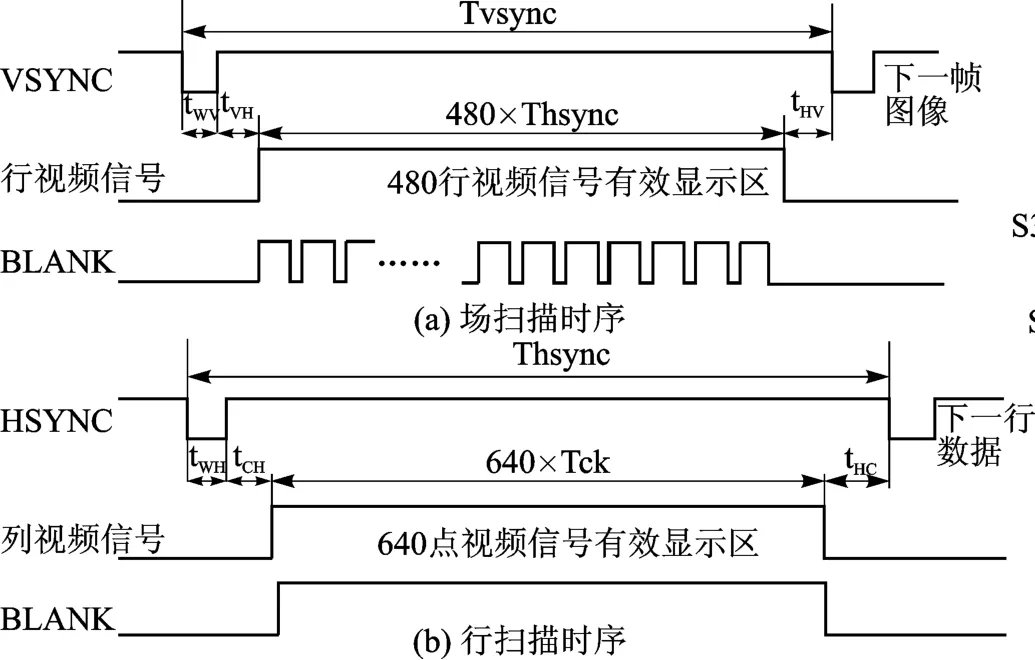

以分辨率为640×480、刷新频率为60 Hz、16位的彩色显示模式为例,VGA信号的扫描时序如图3所示。

图3 VGA信号扫描时序图

在场扫描时序中,VSYNC为场同步信号,Tvsync是指显示器扫描1帧完整画面需要的时间,大小为16 667 μ s;VSYNC信号每场有525行,其中480行为有效显示行,45行是场消隐期。场消隐期包括场同步时间(低电平场同步脉冲)tWV(2行/63 μ s)、场消隐前肩tHV(13行/412 μ s)、场消隐后肩 tVH(30 行/952 μ s),共 45 行 。

在行扫描时序中,HSYNC为行同步信号,Thsync是指显示器扫描一行需要的时间,大小为31.75 μ s,该周期通过Hsync(行同步脉冲)来同步,脉冲的宽度tWH=3.81 μ s。每显示行包括800点,其中640点为有效显示区,160点为行消隐期(是非显示区)。行消隐期包括行同步时间tWH(3.81 μ s),行消隐前肩 tHC(0.516 μ s)和行消隐后肩tCH(1.786 μ s),共 160 个点时钟 。

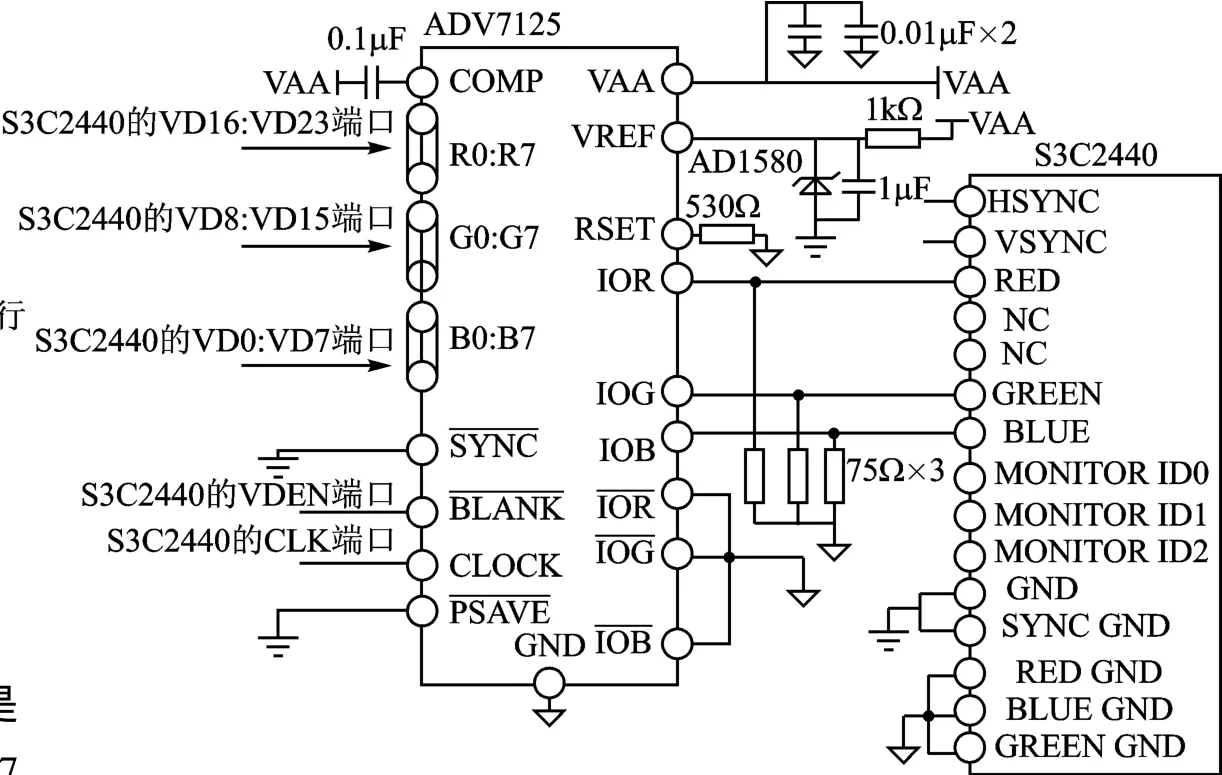

3.2 S3C2440和ADV7125的电路连接

设计中主要使用S3C2440处理器的 LCD控制器接口,它主要通过 DMA方式占用系统总线,支持彩色 TFT液晶屏,支持 16 bbp无调色真彩。LCD接口数据的低8位,中间8位和高8位分别与 ADV7125芯片的BLUE信号、GREEN信号和 RED信号相连,这样就完成了S3C2440处理器与ADV7125芯片之间数字信号的传输。ADV7125芯片的时钟信号采用LCD接口的时钟信号,信号与VM(VSDN)信号相连接,SYNC同步信号接地。COMP端用于内部参考运放的补偿,用 0.1 μ F的陶瓷电容连接在COMP与模拟电源VAA之间,防止自激振荡以增加稳定性。采用AD1580作为参考电压,AD1580输出信号稳定,能够很好地满足电路设计的需要。RSET引脚与地之间接一个530 Ω的电阻,用来控制视频信号的满幅度。在图像系统中,不会自动产生复合同步信号利用本设计可以实现视频同步信息编码直接进入绿色信道。如果不需要,把输入端与逻辑低电平相连。S3C2440和ADV7125的电路连接如图4所示。其中 VD0、VD1、…VD23、VDEN 、CLK 、HSYNC、VSYNC为S3C2440的输出端。

图4 ADV7125和S3C2440的电路连接

3.3 电路连接需要注意的问题

ADV7125可以用于灰度视频信号输出。例如:仅用于1个通道进行视频输出,这时其他两个不用的视频数据信道都应该与逻辑0相连,不用的模拟输出应该与使用的信道一样连接相同的负载。

为了实现ADV7125的最优噪声性能,对PCB的设计必须特别注意。ADV7125电源和地线上的噪声应该优化。可以通过屏蔽数字输入和提供好的退耦达到这一点。VAA和GND的引线长度应该尽量短,这样可以减小电感环路。在设计PCB时应尽量把模拟地与数字地分开,地线应该通过1个磁珠与PCB大面积铺地相连,并且磁珠应该尽可能的靠近ADV7125器件的地引脚。电路中使用的电容应该尽可能的靠近对应引脚,,并且电容的引线应该尽可能的短,这样可以减小引线电容。由于使用频率非常高,时钟引线应尽可能地短,这样可以减小噪声的抖动。视频输出信号应该由数字地平面覆盖,这样可以增大高频电源抑制比。

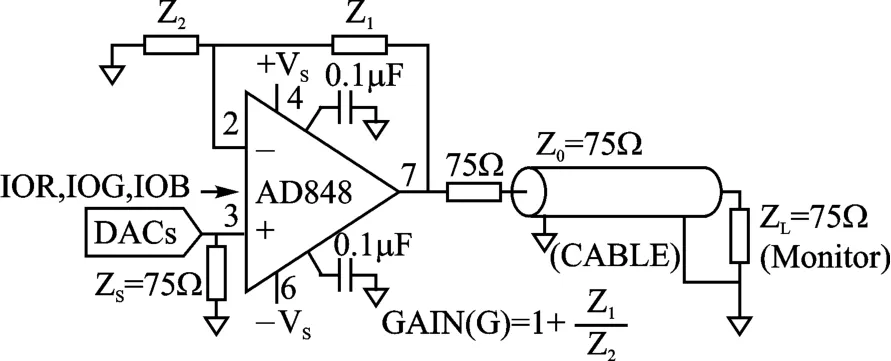

由于模拟RGB信号采用高阻电流源输出方式,可以直接驱动75 Ω的同轴传输线。长于10 m的电缆可能会对高频模拟输出脉冲衰减。使用输出缓冲可以补偿电缆的失真。这些缓冲器在整个输出电压摆幅期间,必须有足够的电流。常见的有AD84x系列的单片运放。在较高的频率下(如80 M Hz),推荐使用AD848。其典型增益电路如图5所示。

图5 VGA信号长距离传输的典型增益电路

通过简单的计算可以得知其增益为:GAIN=1+Z1/Z2。改变缓冲电路的增益器件Z1、Z2来满足所要求的视频电平。

3.4 相关的软件设置

下面以简单的测试程序为例来说明相关软件的编写。

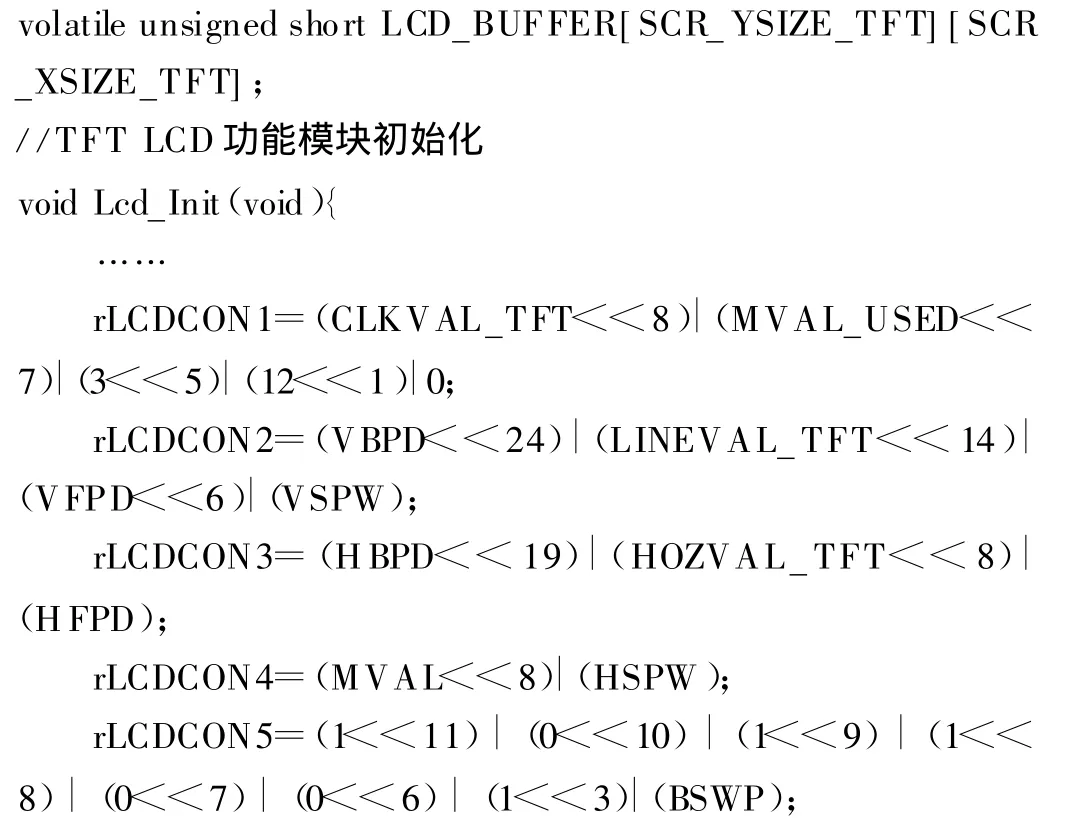

软件设计的基本流程如图6所示。具体过程如下:

①首先对LCD的功能寄存器进行初始化,主要设置LCD控制寄存器1~5,LCD缓冲区起始地址控制寄存器;屏蔽LCD中断。

②其次对LCD的输出时序(VGA信号时序)进行设置。设置分辨率、周期、前(后)信号、同步脉冲。

③再次是对视频信号进行设置,主要是使能LCD视频信号的输出。

④用一幅图像的输出来测试VGA的显示是否正常。

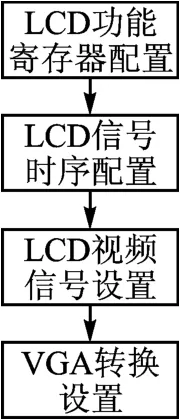

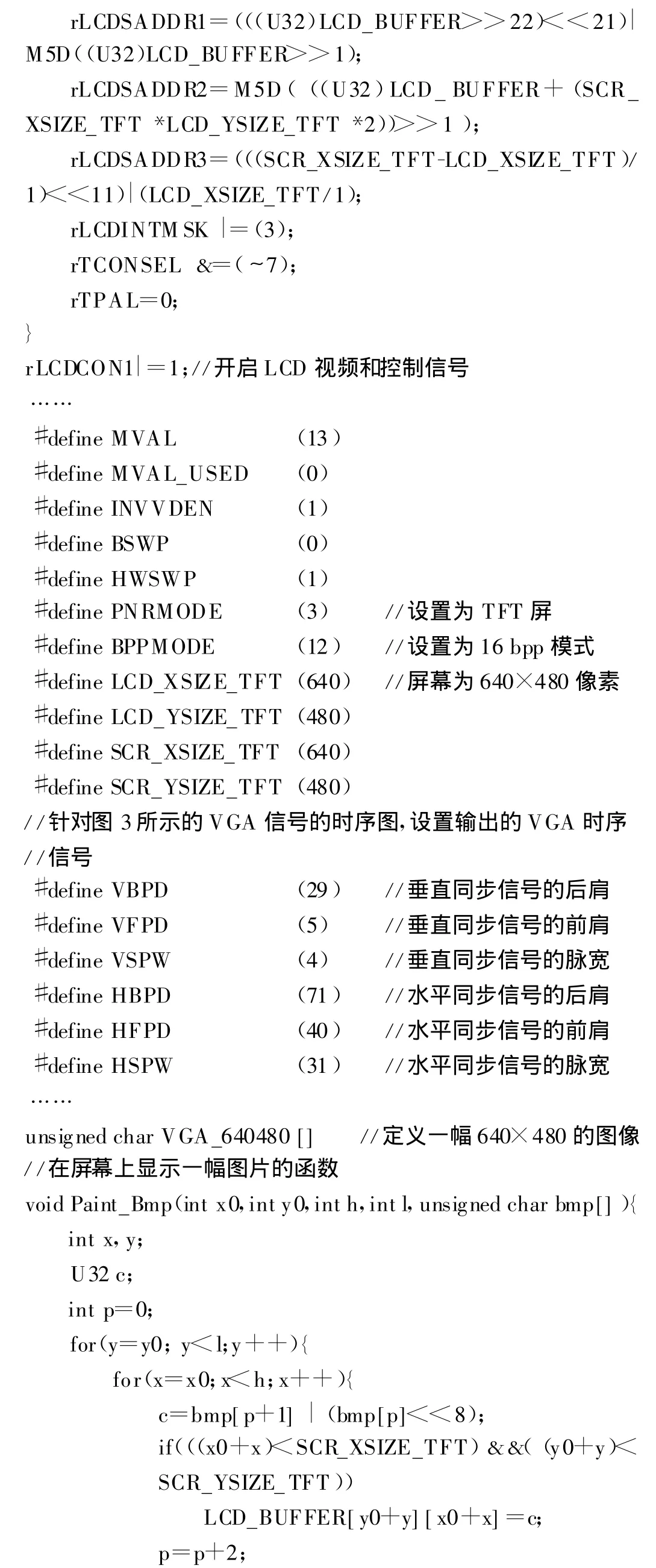

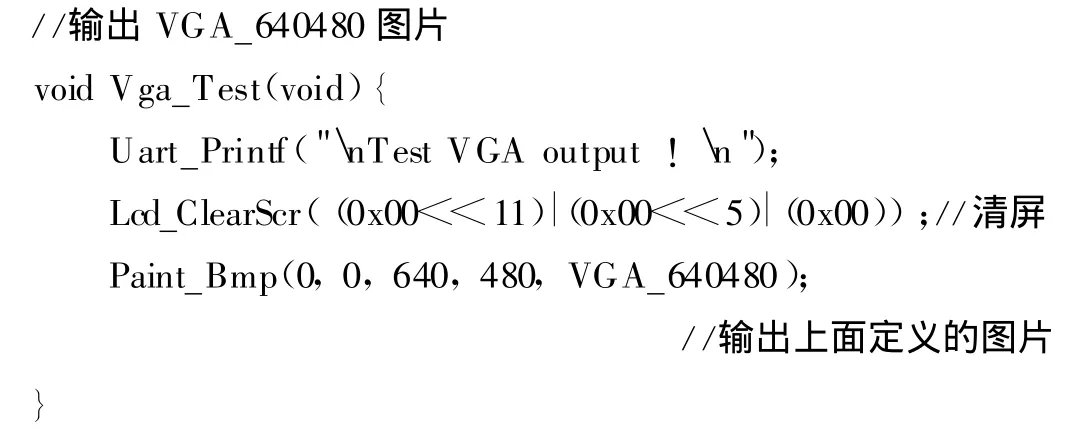

主要代码如下所示:

图6 软件设计流程

结 语

本文结合S3C2440处理器和ADV7125芯片的特点,介绍了LCD转VGA方案,该方案简单易行,适用于嵌入式系统设备的VGA信号输出。ADV7125芯片有多种频率可供选择。本设计也可以用于灰度级输出的信号中,在此基础上进行一些简单的修改,可以满足高分辨率,高刷新频率的环境要求。

[1]ADV7125芯片数据手册[OL].[2011-03].http://www.analog.com/static/imported-files/data_sheets/ADV7125.pdf.

[2]王恒心,熊庆国.基于FPGA/CPLD的嵌入式VGA显示系统[J].微计算机信息,2008,24(9-2):146-148.

[3]乔义川,冯丽辉.一种基于S3C2410的LCD转VGA简易技术方法研究[J].云南师范大学学报,2009,29(4):42-45.

[4]范金龙,王景中.基于CH7004的嵌入式系统VGA接口设计[J].电子设计工程,2009,17(9):6-8.