基于高速D/A AD9739的宽带信号产生*

王 锰,吕卫祥

(南京船舶雷达研究所,南京 210003)

1 引言

自雷达问世以来,人们通过雷达看到的所谓“目标”一直都是A/R 显示器上的“尖头脉冲”或PPI 显示器上的“亮点”。但是,人们也一直希望雷达能像“眼睛”一样看到目标的“形象”,即真正的目标“图像”,这就需要采用宽带雷达技术。宽带雷达能提供高分辨目标距离剖面图(一维距离像),帮助目标分类识别,提高目标距离测量精度,提高抗干扰能力,降低多路径效应,并能提供更好的在杂波中目标检测的能力[1]。宽带雷达技术与合成孔径(或逆合成孔径)技术同时采用,则可形成目标的高分辨二维图像。

在目前的宽带雷达中,脉内宽带线性调频信号是一种最常用的信号形式。产生线性调频信号有两种基本方法,即模拟法和数字法。模拟法一般是通过线性锯齿电压控制压控振荡器产生线性调频信号或者利用SAW(声表面波)器件作为展宽网络产生调频信号。但是,压控法存在每个脉冲起始的射频相位不相参的问题,且稳定性较差,相位噪声和谐波分量也比较大;SAW 器件法受SAW 器件物理尺寸限制,产生信号脉宽较短,且不同脉宽的信号需采用不同的声表面波器件。

随着大规模集成电路的发展,直接数字合成(DDS)法较多地被应用于宽带线性调频信号的产生,使用直接数字合成技术能产生任意波形,并能对输出波形的频率、幅度和相位进行精确的控制。另外,DDS还被应用于频率合成器中,产生时钟、倍频链输入信号等较低频率的连续波信号。目前,直接数字合成法硬件方案主要有两种,一种是DDS ASIC 芯片法,DDS 芯片内部集成DDS 核及高速D/A 转换器,利用DSP、FPGA 或CPLD 给DDS 芯片送入控制字,即可得到所需带宽、脉宽、周期及频率信号;另一种是FPGA与高速D/A 转换器结合,由FPGA 完成DDS 核的功能,送高速D/A 转化器转换为模拟信号[2]。第一种方法工作时钟频率较高,但灵活性欠佳,主要用于连续波以及简单脉冲信号的产生;第二种方法灵活性较强,可以用于任意波形的产生,但受限于FPGA的工作频率,主要用来产生较低频率的中频信号。随着集成电路技术的不断发展,FPGA 工作时钟不断得到提高,与高速D/A 结合能用于宽带任意信号及高中频连续波信号的产生,本文介绍的即是此种方法。

2 原理分析

为提高端口传送速率,时钟频率在1 GHz 以上的D/A 芯片通常采用双沿数据传送(DDR)模式。本文中所采用的D/A为双输入数据端口,每个端口最高速率为1.25 GSPS,DDR 模式,而FPGA 内部采用普通I/O口传送方式无法直接输出如此高速率的数据,需要采用新型FPGA 提供的ChipSync 特性,通过多通道合成的并串转换技术来实现。为保证系统工作的稳定性,本方案中最终设计FPGA 输出端口工作在双路端口速率各为1.2 GSPS,DDR 模式。采用16 通道数据合成1 通道的方式为D/A 芯片提供数字波形数据,设计D/A 工作时钟速率为2.4 GSPS。为产生宽带线性调频信号,假设其带宽为B,起始频率为f0,脉宽τ,根据文献[3]的推导,16个通道中第j个通道的初相和第i个采样时刻的数据和频率步进码分别为

3 硬件实现

根据公式(1)、(2)的计算结果,可利用FPGA 产生16个通道的信号数据,通过并串转换排序输出给D/A后,就能得到所需要的信号。

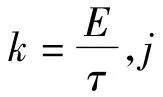

硬件平台主要包含XILINX 公司的VIRTEX-5 系列FPGA XC5VSX50T,AD 公司的2.5GSPS D/A 转换器AD9739,NS 公司的时钟分配芯片LMK01000 及稳压电源芯片等,硬件原理框图如图1。

XC5VSX50T FPGA为XILINX 公司基于65 nm 工艺的新一代FPGA,包含288个DSP48E Slices,最大4752 Kb Block RAM 以及最大480个用户可定义I/O口,其时钟管理片中包含两个DCMs和一个PLL,其中DCMs 最高输入时钟450 MHz,最高输出时钟500 MHz,PLL 最高输入时钟645 MHz,内部VCO 最高工作频率可达1 000 MHz,支持OSERDES技术实现高速IO 口互联。

图1 硬件原理框图

AD9739为AD 公司一款高速高性能RF 数模转换器,内部最高采样率达2.5 GSPS,双通道LVDS 数据输入,每个通道数据最高速率1.25 GSPS(DDR),当工作在其独特的“MIX MODE”下时,可将第二或第三奈奎斯特区的输出信号直接用作发射信号,减少混频环节,真正以“软件无线电”的方式实现了上行通道功能。FPGA VHDL 程序设计主要包含时钟分配,DDS 数据产生,并串转换等。在本例中,FPGA 内部OSERDES 模块的CLK(串行数据时钟)和CLKDIV(并行数据时钟)分别为600 MHz和150 MHz,受限于FPGA的布局及DCM的最高工作频率,CLK 及CLKDIV 只能用FPGA内部的PLL 模块产生。时钟分配主要是将来自LMK 01000的300 MHz时钟(为保证时钟的相参,将AD 9739 工作时钟的四分频DCO 输出用LMK 01000 再二分频后送FPGA的全局时钟输入端)经过PLL后,得到150 MHz和600 MHz,其中150 MHz分别作为FPGA的工作时钟和OSERDES 模块的CLKDIV,600 MHZ时钟作为OSERDES 模块的串行时钟CLK。DDS 数据产生主要是产生16组初相位不同的DDS 数据,经排序后送给FPGA 内部的OSERDES 模块。并串转换作用主要是将16组低速并行数据转换为双14 位串行高速DDR数据,并同时送出同步数据时钟,在同步时钟的同步下将数据送往AD 9739。

此外,还通过对板载的AT89C 2051 单片机的编程来设置AD 9739和LMK 01000的功能参数和芯片初始化,以保证其正常稳定工作。

4 测试数据

4.1 宽带脉内线性调频信号测试数据

采用微波信号源提供AD 9739 2.4 GHz的工作时钟,AD 9739 工作于Normal MODE,利用上述硬件平台产生544 MHz中心频率,带宽为200 MHz,脉宽为178 μs的线性调频信号,其频谱及时域波形如图2所示。可见,在未滤波的情况下,带内平坦度在0.5 dB 内。

图2 中频宽带线性调频信号频域及时域图

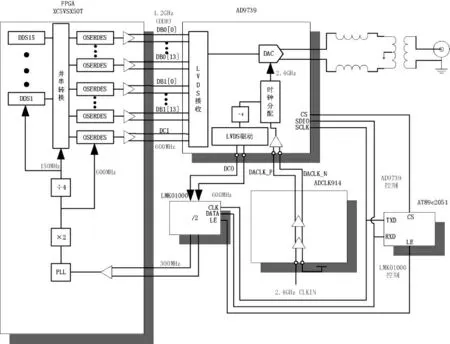

采用微波信号源提供AD 9739 2.4 GHz的工作时钟,AD 9739 工作于MIX MODE,利用上述硬件平台产生1 400 MHz中心频率,带宽为300 MHz,脉宽为178 μs的线性调频信号,其频谱见图3。可见,在未滤波的情况下,带内平坦度在0.5 dB 内,这比普通D/A的输出在第二奈奎斯特区的大幅度滚降有相当大的改善。

4.2 连续波信号测试数据

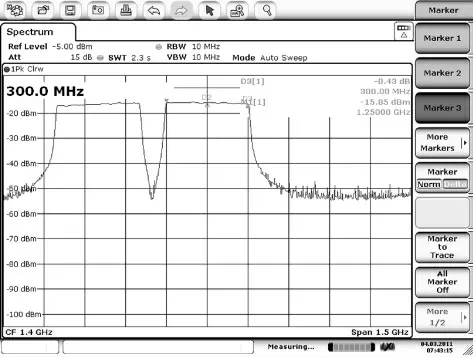

采用微波信号源提供AD9739 2.4 GHz的工作时钟。AD 9739 工作于Normal MODE,利用上述硬件平台产生172.5 MHz的连续波正弦信号,其频谱图如图4所示。可见,杂散可达到-75 dBc 以下,将172.5 MHz滤波后,经过十六倍频得到2760 MHz的微波连续波信号,其频谱图如图5所示,其杂散可达-60 dBc 以下。

图3 MIX MODE 下射频宽带线性调频信号频谱图

图4 172.5 MHz 连续波信号频谱及波形图

图5 2760 MHz 连续波信号频谱图

5 结束语

将FPGA与高速D/A 结合,用DDS 产生544 MHz中心频率、200 MHz 带宽的线性调频信号,再用本振一次混频得到宽带通道的微波激励信号,此方案目前已应用在某型雷达样机中取代倍频方案。经测试,信号参数及最终脉压结果比倍频方案有较大改善。而利用上述方案产生较低频率连续波,经倍频得到微波一本振,杂散指标也比原专用DDS 芯片AD 9858的方案提高了10 dB 以上,可用于高性能数字式频率合成器的设计。

目前,限于D/A的工作频率,输出信号频率还比较低,仍需要一次混频或倍频才能得到所需要的更高微波频段信号。随着模拟和数字器件工艺的发展,D/A 及FPGA的工作频率会不断得到提高,基于DDS的信号产生方式会得到越来越广泛的应用,“软件无线电”也会逐步实现。

[1]费元春.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.

[2]A Technical Tutorial on Digital Signal Synthesis[M].Analog Device,Inc.1999.

[3]蒋倜.并串转换法合成多通道宽带DDS信号[J].雷达与对抗,2009(4).