光传飞行控制交叉通道数据链路接口技术研究

王新华,甄子洋,杨一栋,龚华军

(南京航空航天大学自动化学院,南京 210016)

0 引言

光传操纵系统被誉为继电传操纵后的第3代操纵系统,是21世纪飞行操纵必然的发展趋势[1-5]。光传操纵系统(Fly-By-Light,FBL)是指在飞机的飞行控制、发动机控制和航空电子系统中采用光纤作为信号传输的媒介。光传操纵系统由于采用了光纤作为传输媒介,与电传飞行控制系统相比具有如下优点:1)可以有效地防御电磁干扰(EMI)及由雷击或闪电引起的电磁冲击(EMP),对核爆炸等引起的电磁脉冲不敏感;2)由于光纤一般由SiO2晶体制成,纤芯很细,因而可以极大地减少系统的重量和尺寸;3)光纤传输频带宽、容量大;4)光纤的抗腐蚀性和热防护品质优良。

随着对飞机性能要求的不断提高,数字控制技术已经广泛应用于飞行控制系统,它以较少的硬件提供较高的故障检测覆盖率,能消除容差积累,提供完善的信号选择和性能监控,且设计具有很强的灵活性。但是数字控制系统由于部件增多,因此故障率较高,一般单一通道数字控制回路难以满足飞机可靠性的要求。为了实现飞机操纵系统的安全可靠性,除了设法降低元部件本身的故障率外,在现有条件下,一条重要的途径是采用余度技术。目前技术条件下飞行控制计算机之间的数据通信有两种方式:数据总线和交叉通道数据链路(Cross Channel Data Link,CCDL)方式。其中交叉通道数据链路硬件结构比较简单,易于实现,减少了对数据总线的依赖,因此电气隔离性能好,一个通道的单点故障不会波及其他通道和其他部件,容易满足整个系统的可靠性及安全性要求。美国F-18、F-16飞行控制系统均采用了类似的方式[6-7]。

基于串口RS232协议的三余度光传飞行控制半物理仿真验证系统是为了验证光纤技术工程化实现的可行性而开发的地面半物理验证平台[8]。通过此平台,可以验证光交叉通道数据链路(OCCDL),光传余度管理算法和策略等功能。但是计算机串行协议的最高速率仅为961.2 kb/s,已远不能满足未来战机的需求,而且光器件的数据传输容量也远远高于此速率,还有进一步提高的可能。为此,本文设计了一种基于FPGA的高速交叉通道数据链路,以进一步提高信息交换的传输速率和可靠性。

1 OCCDL接口卡设计

三余度光传飞控计算机之间总共用6条多模光纤来实现双向通信[6-10],信号都是通过PCI接口卡收发。由于每台计算机都要与另外两台计算机相互通信,所以每个PCI卡需要两条通道,即通道a和通道b,每条通道既要进行发送,又要进行接收。

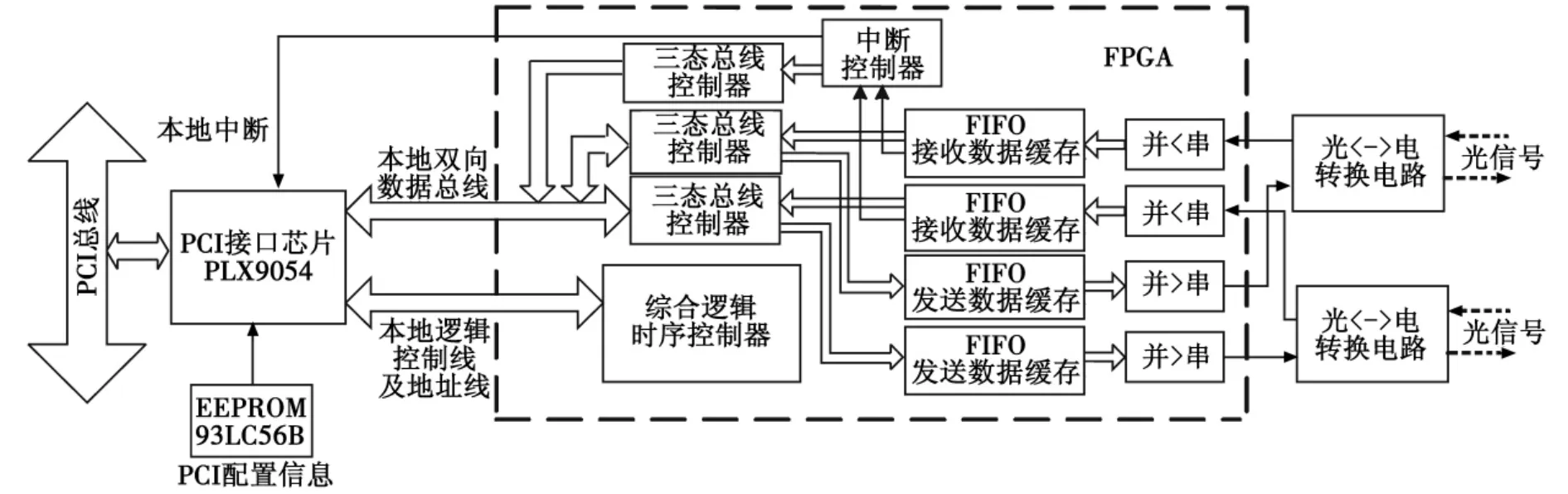

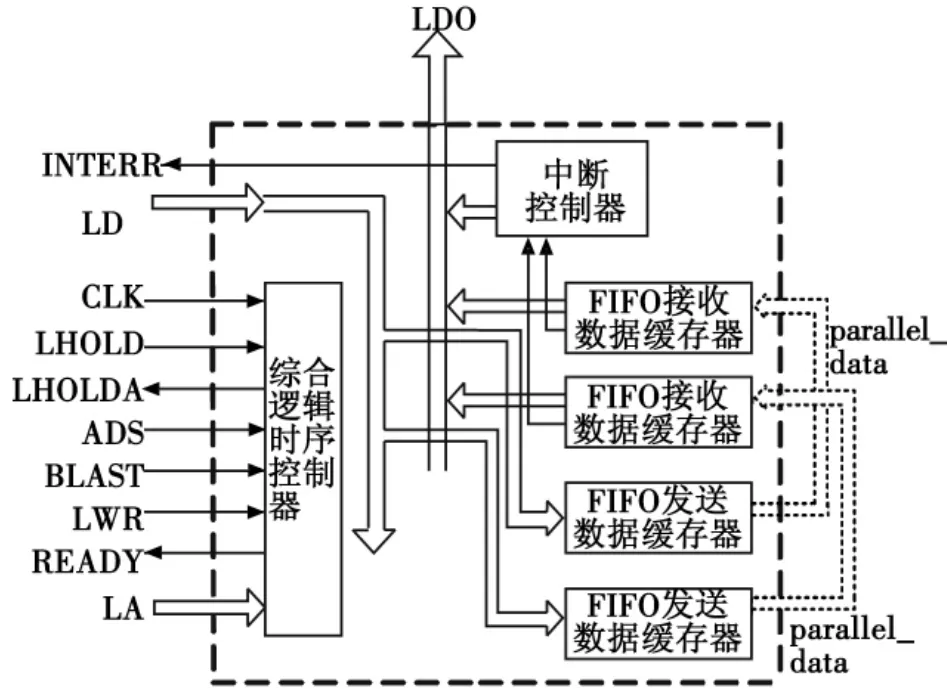

光交叉通道数据链路PCI接口卡的设计方案如图1所示。其中PLX9054的PCI端口负责与PCI总线连接,完成所有的本地总线与PCI总线的转接工作。本地端口与FPGA连接,FPGA模块中综合逻辑时序控制器用于实现每个通道的数据传输。PLX9054有读/写的控制线,C模式下有单周期读/写时序和突发周期读写时序。每个时序都有对应的引脚,将这些引脚与FPGA相连,由FPGA来控制实现读/写的时序。三态总线控制器用于FPGA与PLX9054双向数据总线的控制。

图1 光传交叉通道数据链路接口卡框图Fig.1 Structure of the optical cross channel data link interface card

PLX9054内部的FIFO用来缓存数据,实现PCI总线与本地总线之间的异步接收。但往往由于PLX9054本地总线传输速率较慢,为保证可靠性,需要在PLX9054本地端扩充FIFO,用于临时存储数据。本接口卡用4个FIFO模块,分别对应两个通道的读FIFO和写FIFO。

本接口卡是采用完全相同的两个通道a和b,每个通道各有收/发两路。飞控计算机在处理完需要发送给其他飞控计算机数据后,分别加以发送,先后顺序可以由软件控制,也可以随机选择发送。而主要需要解决的是在接收的时候,计算机需判别是哪个通道的信号,这就需要在FPGA中设计中断寄存器来告知计算机接收信号的通道号。

以上功能以及串/并、并/串转换功能均由FPGA来实现。

2 OCCDL通信逻辑及光电转换电路实现

2.1 FPGA逻辑电路实现程序设计

通过上述分析,要完成本接口卡各部分硬件的协调工作,关键是设计FPGA的内部逻辑电路。在此给出了本设计的FPGA内部逻辑框图,如图1所示。采用Altera公司的FLEX10K30A,该芯片最高传输速率超过77 MHz,相应配套的 EEPROM是 EPC2LC20;有30000个逻辑门,有效RAM达到12 kb,可用I/O引脚147个,完全能满足上述设计。在程序实现上采用了VHDL语言进行逻辑编程。

2.1.1 综合逻辑时序控制器

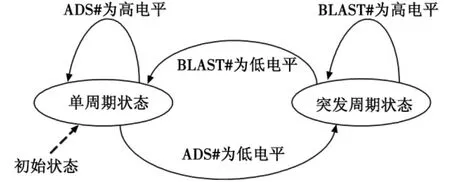

PLX9054的读写过程是:当PLX9054需要向本地端FPGA读写数据时,首先发出LHOLD高电平信号请求本地端FPGA,本地端FPGA收到后立即应答LHOL-DA高电平信号;PLX9054收到应答后,置ADS#一个时钟周期低电平以表示新的一轮访问开始;访问开始后,本地端FPGA立即置READY#为低电平以表示此时数据总线上的读写数据有效;当读写数据还有最后一个时,PLX9054置BLAST#为低电平;FPGA发现BLAST#为低电平时,在下一个时钟周期置READY#为高电平以表示此时数据总线上的读写数据无效。由于PLX9054存在单周期和突发周期两种时序,综合考虑后,设计一个包含两种状态的状态机,如图2所示。

图2 状态机工作机理Fig.2 Working process of state machine

2.1.2 中断管理控制器

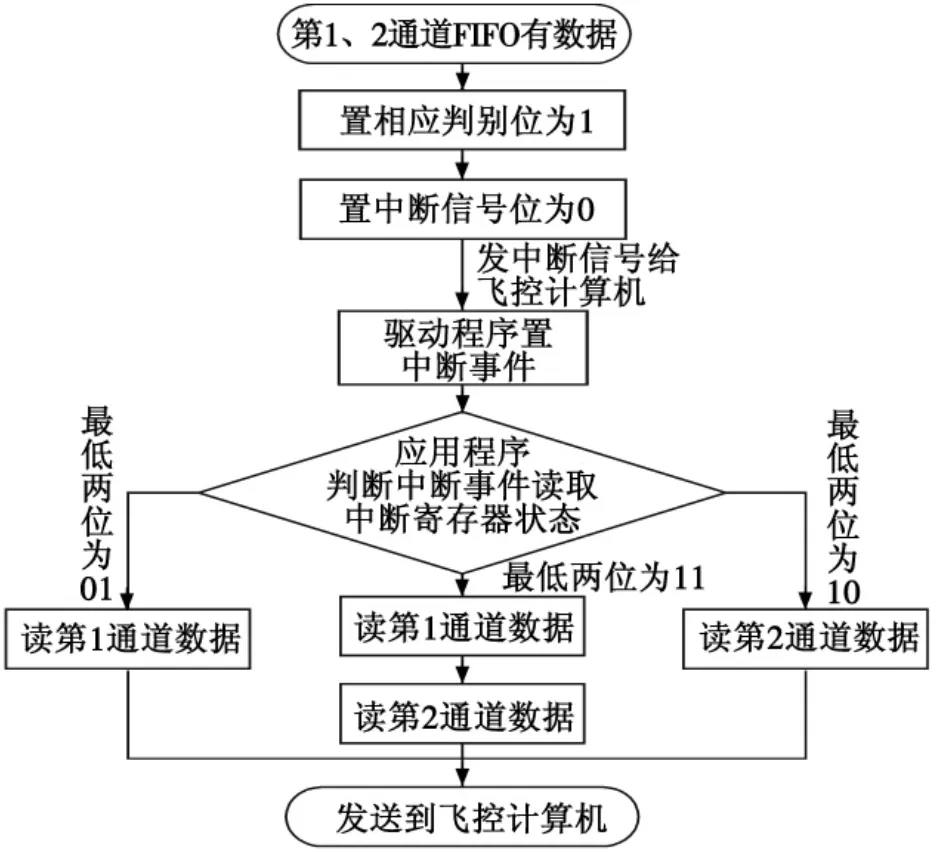

设计中断控制器的关键在于判断两个接收FIFO缓存区中是否有数据,可以通过FIFO模块的empty输出信号来判断。本接口卡将中断控制器设置为8位的寄存器,其中设置最低位、第2位分别表示第1、2通道的FIFO是否有数据,高电平表示有数据,低电平表示无数据。最高位设置为中断信号位,低电平表示产生中断信号;反之不产生中断信号。产生中断信号的条件是两个FIFO中至少一个有数据。其流程见图3。

图3 中断控制器流程图Fig.3 Working process of interrupt controller

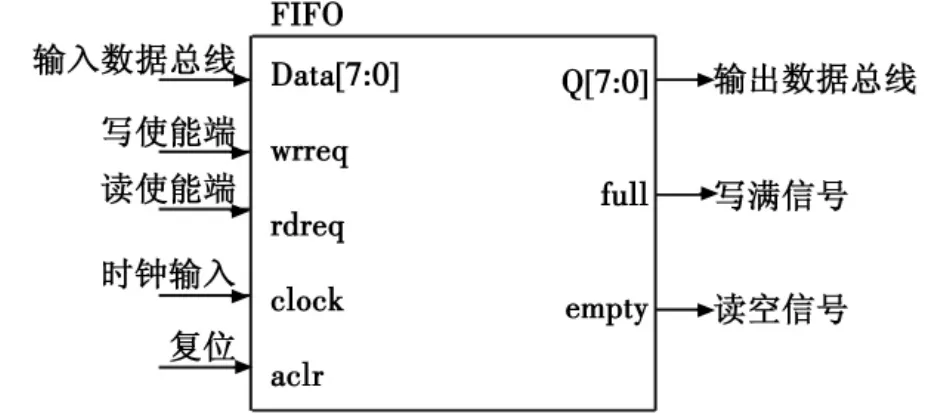

2.1.3 FIFO 缓存器

收发数据FIFO缓存器采用IP核复用的方式设计,以减少设计人力和风险,缩短设计周期。本系统采用Altera公司的固IP核来设计FIFO收发数据缓存器,进行相关配置后生成如下IP核,如图4所示。

图4 FIFO收发数据缓存器Fig.4 Data buffer with FIFO

2.1.4 三态总线控制器

本系统使用三态总线控制器用来控制本地双向数据总线以进行双向的分时传输。三态总线控制器采用Altera公司的固IP核,并根据需要对一些参数进行配置。

2.1.5 串并转换模块

由于本地总线是并行总线,而光纤只能传输串行数据,因此必须设计并→串及串→并转换模块。本系统并→串转换模块的传输协议采用标准RS-232协议,即1个起始位,8位数据位,1位停止位,其中起始位规定为低电平,停止位为高电平。

并→串转换模块的设计思想是首先判断FIFO缓存器中是否有并行数据,若有则取出并行数据并存储在转换寄存器中,同时发送起始位;之后连续发送8位数据,依次由低到高传输,并计数;由计数值知道是否完成了8位数据传输,若完成则发送停止位,同时计数器归零,可以开始下一轮传输。

2.2 光/电、电/光转换电路

光电模块采用成熟的多模光纤、光/电和电/光变换芯片。本系统的光/电、电/光转换模块分别采用Agilent公司的一对产品HFBR2412和HFBR1414,该产品的转换速率最高为155 Mb/s。另外需要逻辑与非门和反向器等,分别用SN75451和74LS14。该转换电路经过单独测试,其传输速度达到了4 Mb/s。

3 OCCDL逻辑电路综合仿真

本系统运用Altera公司提供的FPGA编程工具Quartus6.0进行编程,然后综合、仿真、布局布线、时序分析、优化,得到正确的结果后,将生成的网表文件下载到FLEX10K30A(或EPC2LC20)中,在物理上实现了上述功能。为了验证FPGA逻辑功能的正确性,建立了如图5所示仿真结构。图5中虚线部分分别表示输出的并行数据与输入的并行数据相连进行测试。

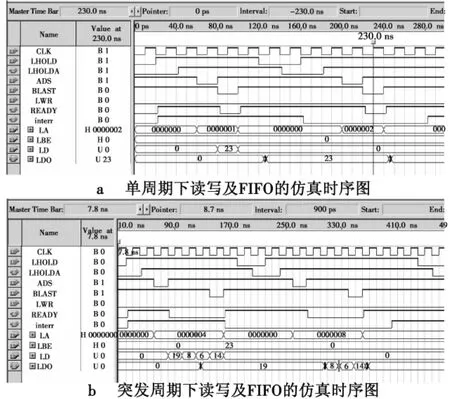

首先在单周期下,判断读写及FIFO缓存器的时序是否正确,并判断写入与读出数据是否完全一致,中断信号是否输出正确。其仿真结果见图6a。对突发周期下读写及FIFO缓存器的时序、中断进行仿真,仿真图见图6b。将上述仿真图与PLX9054读写时序图对比后可知,接口时序逻辑完全符合时序要求,且写入的数据与读出的数据完全一致,验证了FIFO缓存器的功能,同时当接收FIFO中存有数据时,中断输出端interr为低电平,产生了中断信号,符合设计要求。

图5 FPGA逻辑控制模块仿真结构图Fig.5 Simulation structure of FPGA logic control module

图6 FPGA逻辑控制模块仿真时序图Fig.6 FPGA logic control module simulation timing diagram

4 OCCDL接口驱动程序开发与测试

此外,本文还进行了光通信PCI接口卡的设备驱动程序的开发,通常开发PCI设备驱动程序有多种模式,在Windows环境下,主要采用WDM(Windows Driver Model)模式。本系统选择DriverStudio3.0作为开发WDM驱动程序的工具,DriverStudio是一整套开发、调试和检测Windows平台下设备驱动程序的工具软件包[11]。它把DDK(Device Development Kit)封装成完整的C++函数库,根据具体硬件通过向导生成框架代码,并且提供了一套完整的调试和性能测试工具(SoftICE、Diver Monitor)等。Driver Studio支持Windows多种操作系统下的驱动软件开发,并且在不同的操作系统下,开发者所写的驱动软件代码完全不用修改,只需要在不同的操作系统下重新编译即可。

本设计使用的是Visual C++环境,在Windows2000下开发和调试本卡的设备驱动程序。在本卡驱动程序设计中,关键两点是PCI的中断服务程序和PCI总线的数据交换(读、写)。利用Driver Wizards这个向导来生成PCI结构的驱动程序的框架。在此框架的基础上增减一些代码,包括配置空间的访问模块、中断模块、读写模块等。

驱动程序中INF文件是指设备信息文件:在支持即插即用机制(Plug&Play)操作系统中,当为指定硬件设备安装驱动程序时,系统会根据INF文件中包含的检测和安装设备的信息来决定设备使用的资源,并为该设备安装相应的驱动程序。Driver Studio会自动为开发者定制一个INF文件,所要做的工作是对制造商、设备类型、设备名称等基本信息加以修改,并添加一些附加信息,如提供者、设备版本号、安装时需自动复制的文件等信息。

另外,利用Driver Wizards生成驱动程序框架的时候,同时生成一个测试程序,经过修改可以用于接口卡的测试。驱动程序加载以后,它的许多进程处于空闲状态,实际上需要用户应用测试程序去调用激活。测试程序利用Win32 API直接调用驱动程序,实现驱动程序和应用程序的信息交互。

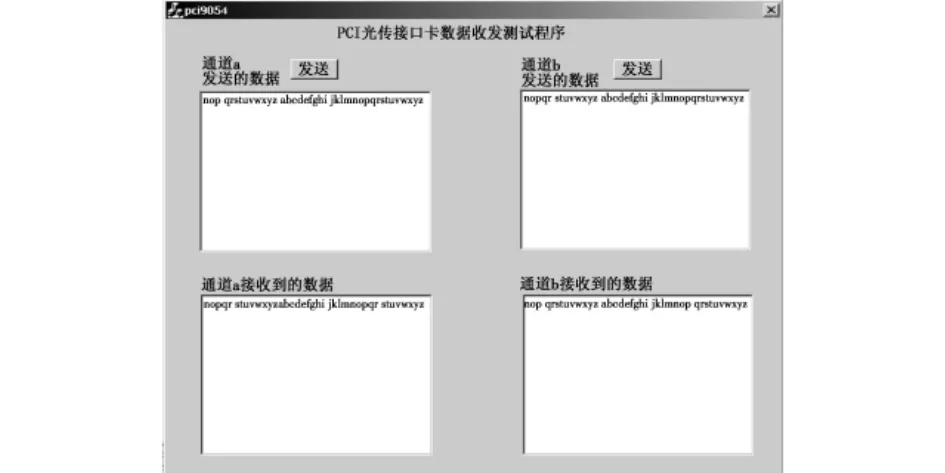

在启动操作系统后,将提示发现新硬件,在设备管理器会发现PCI卡的配置信息。系统将为其分配相关资源,然后把配套开发的驱动程序装好,就可以使用该设备了。将该光交叉通道数据链路PCI接口卡的a通道和b通道的光发送和光接收模块交叉连接,其数据传输结果如图7所示。

图7 光交叉通道数据链路接口卡数据传输测试结果Fig.7 OCCDL interface card data transmission test results

5 总结

本文从实际应用出发,给出了以PCI总线控制器PLX9054和FPGA为核心的双向高速数据传输接口卡设计的方法,实现了基于FPGA的PLX9054逻辑控制模块和串并数据转换模块的设计,研制了光电转换模块的硬件电路,最后编写了接口卡驱动程序和测试程序。经过测试,可以在4 Mbps的速率下可靠地完成数据的传输,可以满足飞控计算机之间余度数据交换的要求。该接口卡的成功开发,为后续光传三余度半物理仿真验证平台的开发奠定了基础。

[1]温瑾,杨一栋,王新华.光传飞行控制系统中WDM技术的开发研究[J].电光与控制,2004,11(2):10-14.

[2]杨一栋,刘晓里.光传飞行控制[M].北京:国防工业出版社,2006.

[3]齐劲松,王伟,吴成富,等.三余度飞控计算机交叉数据链系统设计[J].测控技术,2007,26(5):73-75.

[4]ANUMOLU P,PIRICH R.Fiber optic considerations for insertion into legacy avionics platforms[C]//IEEE Pro-ceedings of Avionics,Fiber-Optics and Photonics Technology Conference,IEEE,2007:24-25.

[5]李玉飞,苏媛.光传飞行控制系统研究[J].航空科学技术,2009(5):7-11.

[6]CORRIGAN J,SHAW B,JONES J.Demonstration results of fly-by-light flight control system architectures for tactical military aircraft[J].Proceedings of SPIE,1996,2840:77-88.

[7]TISPSUWANPOM V,SANGRAYUB A,SUESUT T,ed al.Development of PLC fiber-optic network for redundant system[C]//New York:IEEE Proceedings of ICIT,2002:303-306.

[8]王新华.分布式三余度光传综合火力/飞行控制系统研究[D].南京:南京航空航天大学,2003.

[9]TODD J R.A review of the fly-by-light optical Aileron trim flight demonstration system[C]//New York:AIAA/IEEE/SAE,Proceedings of 17th DASC,1998:D33/1-D33/3.

[10]朱家强,张京城.基于FC光传总线的分布式容错系统组通信协议[J].航空学报,2008,29(S):229-234.

[11]彭杰,汪国有,张天序.PCI9054本地总线控制可编程逻辑设计[J].计算机仿真,2003,20(9):74-76.