新型双声道音频Σ- ΔDAC小面积插值滤波器的设计实现

刘素娟 张 特 陈建新

(北京工业大学光电子技术省部共建教育部重点实验室 北京 100124)

1 引言

Σ- Δ数模转换器(DAC)采用过采样以及Σ- Δ调制技术来实现数模转换,具有转换精度高转换速率相对低的特点,适用于音频信号处理系统。过采样Σ- Δ调制目前己成为实现高精度音频数模转换的主要实现方式[1,2]。这种技术是通过数字处理技术来降低对模拟电路的要求,因此数字电路尤其是实现过采样的插值滤波器消耗的面积和功耗都比较大。为了减小插值滤波器的面积,文献[3]采用CSD编码,把定系数乘法运算转化为移位相加(减);经CSD编码后,可使加(减)法的次数大幅度降低,从而减小芯片面积;但实现高阶的FIR滤波器时仍需要大量的加法器和减法器,硬件消耗较大。文献[4,5]采用FPGA实现来减小硬件消耗。文献[6]利用改进的MDT结构,有效的减小插值滤波器的面积。文献[7]提出了系数混合基分解的多相半带滤波器的无乘法器实现方法,插值滤波器面积占用0.6 mm2。本文提出了一种提出了一种双声道复用的设计方法,设计的插值滤波器保证106 dB信噪比的同时,数字部分仅占用芯片面积 0.198 mm2,大大降低了生产成本,这对目前市场竞争激烈的消费类芯片意义重大。

2 Σ- ΔDAC 的结构

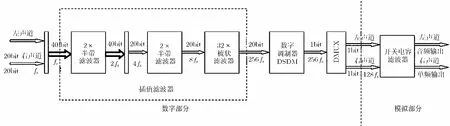

图1是本文提出的Σ- Δ DAC的结构,它由三大部分组成,插值滤波器、数字调制器和开关电容滤波器。其中开关电容滤波器为模拟电路,其余均由数字电路实现。

图1 本文中的Σ- Δ DAC的结构框图

与传统结构不同,本文Σ- ΔDAC中两个声道的20 bit PCM数字信号(采样速率为fs)进入第1级半带滤波器前,先被拼接成40 bit,以便共用一个RAM。为了使两个声道可以复用数字部分的电路,首先将两个的声道的数据按“左右”的顺序合并成一路,合并后的数据送入到插值滤波器完成128倍的插值。Σ- Δ调制器对插值后的数据进行噪声整形,同时把20 bit的数据转换为1 bit的数据流。分解器 DMUX再把左右两个声道的数据分开,同时送给两个开关电容滤波器进行低通滤波,得到模拟信号。插值滤波器和数字调制器被两个声道复用,降低了芯片面积和功耗。

3 插值滤波器的设计

3.1 第1级半带滤波器

第1级半带滤波器的设计非常关键,它的作用除了要完成2倍的插值外,同时还要对插值后带外的镜像信号给予足够的衰减。因此要求第1级半带滤波器的过渡带尽量陡峭,本设计的过渡带为0.4535fs~0.5465fs,阻带衰减大于 90 dB;采用升余弦函数设计了一个75阶的FIR滤波器,并利用了布拉克曼窗进一步抑制旁瓣。

若采用传统方法实现75阶的FIR滤波器需要大量的乘法器,耗费硬件资源较大。本设计考虑到音频信号的采样速率fs较低,2倍插值后第1级半带滤波器的工作速率也只有2fs(96 kHz),而整个芯片的主时钟mclk为256fs(12.288 MHz),每128系统主时钟周期内,第1级半带滤波器的输入数据才更新一次,因此对于75阶的滤波器,可以采用一个RAM和一个 ROM以及一个乘加单元实现。通过时序控制,每隔128个时钟周期,RAM执行一次写操作,写入一个新的数据,写入数据占用1个时钟周期;之后的127个时钟周期执行75次的读操作在时序上绰绰有余。读出的数据分别与各自的抽头系数(存储在ROM内)相乘进行FIR滤波运算。

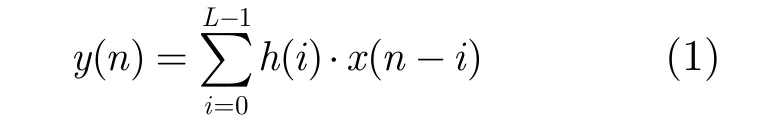

L阶FIR滤波器的输出为

其中L为滤波器的阶数,h(i)为抽头系数。对于输入x(n),需要用到x(n)x(n-1) …x(n-L-1)即x(n)经过延时后的L-1个数据,与其相对应的抽头系数h(i)相乘并求和得到滤波运算后的y(n)。

根据上述理论,得到第1级半带滤波器的结构框图如图 2所示。将x(n)及其经过延时后的数据x(n-i)写入RAM中,n为当前写地址,x(n)为当前周期向RAM中写入的数据,h(i)为与x(n-i)相对应的第i个抽头系数;n-i为RAM的读地址,读出的数据和相应的h(i)相乘得到滤波器的输出y(n)。RAM每执行一次写运算写入x(n)后,在之后的75个主时钟周期内,执行75次读运算将x(n-i)读出与ROM中的h(i)相乘,完成75次累加后得到滤波后的输出y(n)。Rst_n为复位信号,在每次写入新数据的同时对累加器进行清零。这样单声道的半带滤波器可由一个75×20 bit(每个抽头系数采用20 bit量化)的ROM、一个75×20 bit(DAC的输入数据为20 bit)的RAM和一个乘法器、一个加法器实现。

图2 用RAM和ROM实现半带滤波器

双声道实现时,由于左右两个声道的读写地址完全相同,因此可以将两个声道的数据拼成40 bit由一片RAM进行读写。两片规格为76×20 bit(75×20 bit的RAM Artisan不可生成,实际实现时采用 76×20 bit的 RAM)占用面积为 131 μm×183 μm×2;一片76×40 bit的RAM占用面积为208 μm×183 μm,与采用两片76×20 bit 的RAM相比,节省54 μm×183 μm。RAM及ROM的读写时序控制电路综合后面积为6167 μm2,两路乘加单元综合后占用面积为53954 μm2。因此第1级半带滤波器的面积为100789 μm2。

为了与传统 CSD编码实现的半带滤波器相比较,本设计采用CSD编码实现了第1级半带滤波器,并进行双声道复用,综合后的面积为 271288 μm2。利用本文提出的结构实现第 1级半带滤波器与采用CSD编码实现相比,可节省面积63%。

3.2 第2级半带滤波器

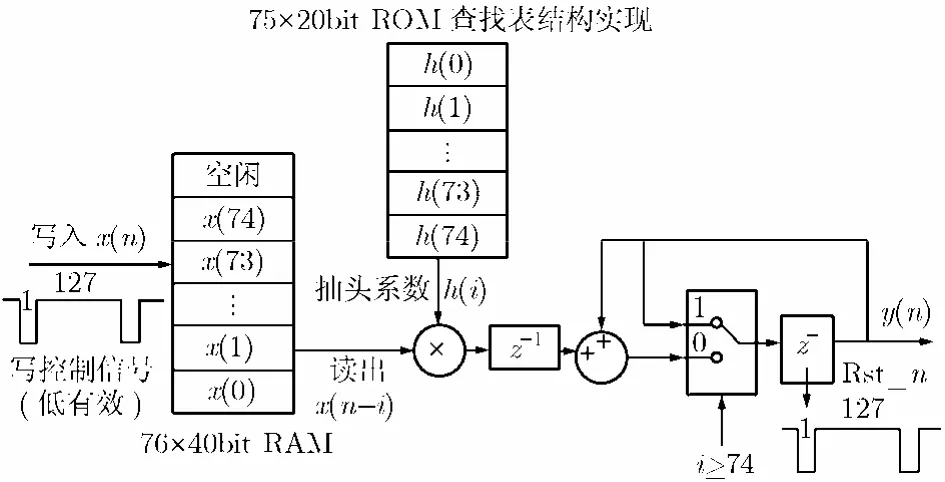

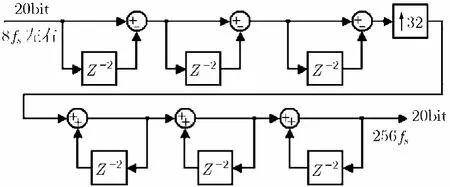

第2级半带滤波器的作用主要是完成2倍插值并滤除镜像信号,不需要有非常陡峭的过渡带和大的阻带衰减。设计中选取了19阶FIR滤波器并加hamming窗对升余弦加以改进,可以得到旁瓣更小的效果。由于滤波器的阶数较小,采用第1级半带滤波器的设计方法并不能有效的减小面积。设计中采用了 polyphase[8]的结构,并针对双声道复用对polyphase结构做了改进,如图3所示。改进后结构与传统polyphase结构相同的是:输入被分为奇偶两路,奇支路完成滤波运算,偶支路对输入进行延时来抵消奇支路的群延时,达到数据对齐的效果。不同的是:考虑到两路的输入信号完全相同,因此设计中把偶支路的延时单元去掉,通过复用奇支路的延时单元即可达到偶支路与奇支路数据对齐的效果。改进结构的延时单元与改进前相比可减少1/3,减少了芯片的面积和功耗,并且便于下一步双声道复用进一步减小面积和功耗。

在此基础上,第2级半带滤波器采用了双声道复用结构,图3中Z-2表示两个延时单元,用两个延时单元分别存储左右两个声道的数据。这样第 2级半带滤波器中除了延时单元外,其它的电路都可以被两个声道复用,由于采用了奇偶支路复用,因此要加倍的延时单元并不多。重新排序模块完成 2倍插值;滤波运算在插值之前完成,降低了芯片的功耗。重新排序模块的具体电路将在后节双声道复用中介绍。

设计中对所有的系数进行 CSD编码,把定系数乘法运算转化为移位相加(减)。编码后第2级半带滤波器需要执行11次加法和8次减法,综合后面积为57713 μm2,双声道复用即延时单元加倍后面积为72688 μm2,比未采用奇偶支路复用和左右声道复用时(综合后面积为77609×2=154138)面积节省了52.8%。

图3 第2级半带滤波器结构图

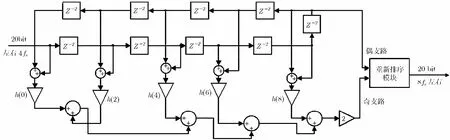

3.3 级联梳状(CIC)滤波器

第3级滤波器主要是完成32倍的插值作用,设计中采用了占用硬件资源少、效率较高的级联梳状CIC (Cascaded Integrator Comb)滤波器,如图4所示。设计中利用等效网络变换理论[9],32倍插值置于差分器和积分器之间,延时单元的消耗减为原来的1/32,同时差分器工作频率也为原来的1/32,减小了芯片的面积和功耗。3级CIC滤波器也通过延时单元加倍实现两个声道的复用,延时单元Z-1加倍为Z-2来分别存储两个声道的数据(图4中Z-2表示两个延时单元)。减法器和加法器可以被两个声道复用,进一步减小芯片的面积和功耗。32倍插值是通过高倍时钟采低速数据完成,不占用硬件资源。

图4 设计的级联梳状滤波器的结构

4 双声道复用实现

对于双声道音频系统,传统方法采用两个Σ- Δ DAC同时处理两个声道可以达到同步的要求,但系统芯片面积较大。本文采用Σ- ΔDAC数字部分的电路被左右两个声道复用来减小芯片的面积和功耗。在第1级半带滤波器中左右两个声道的数据被拼接成40 bit共用一个RAM,RAM存储深度不变,存储宽度增加一倍,读写接口电路均可共用,从而节省芯片面积。在第2、3级插值滤波器中,复用时首先将左右两个声道的数据按“左右左右…”的顺序在时间上排成一个序列,采样率同时提高一倍。电路中所有的延时单元由原来的一个变为两个,来分别存储左右两个声道的数据。这样除延时单元外,电路中的运算单元均可被复用。

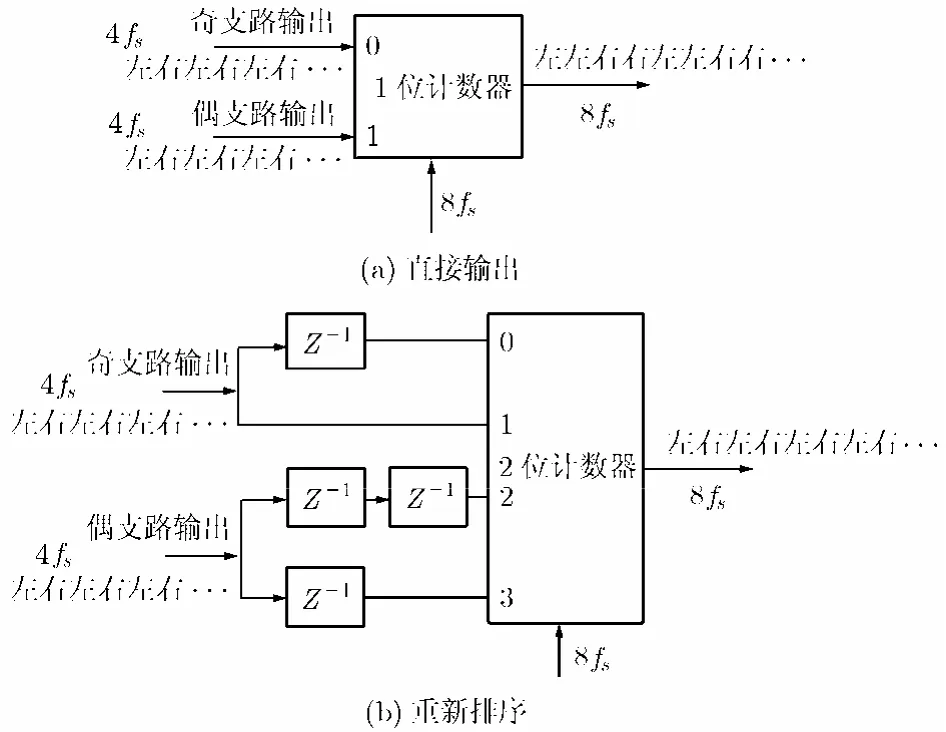

由于插值滤波器中存在2倍插值和32倍插值,插值影响复用时两个声道的同步。例如在第2级半带滤波器中,当奇、偶两个支路的输出合成一路后(完成2倍的插值),如图5(a)所示,左右两个声道的顺序被打乱,“左右左右…”的顺序变成“左左右右…”,导致两个声道不能保持同步。

图5 双声道复用实现结构

为了解决此问题,本文提出重新排序方法,如图5(b)所示。重新排序可由一个2 bit计数器构成选择器完成,当计数器输出为“0”时,选择输出奇支路输出延时一拍后的数据;当计数器输出为“1”时,选择奇支路输出的数据;当计数器输出为“2”时,选择偶支路输出延时两拍后的数据;当计数器输出为“3”时,选择偶支路输出延时一拍后的数据。这样,2倍插值后的数据又被排列成“左右左右…”的顺序,保证了两个声道的同步。

同理,在完成32倍的插值时,重新排序的结构不变,只需要把计数器改为6 bit即可,按照0~31和32~63分为两组,0~31选前两组数据,32~63时选后两组数据,即可使用最少的硬件资源完成两个声道的复用。DAC中的数字Σ- Δ调制器也采用了双声道复用结构,即芯片的整个数字部分由两个声道复用。

5 结果与分析

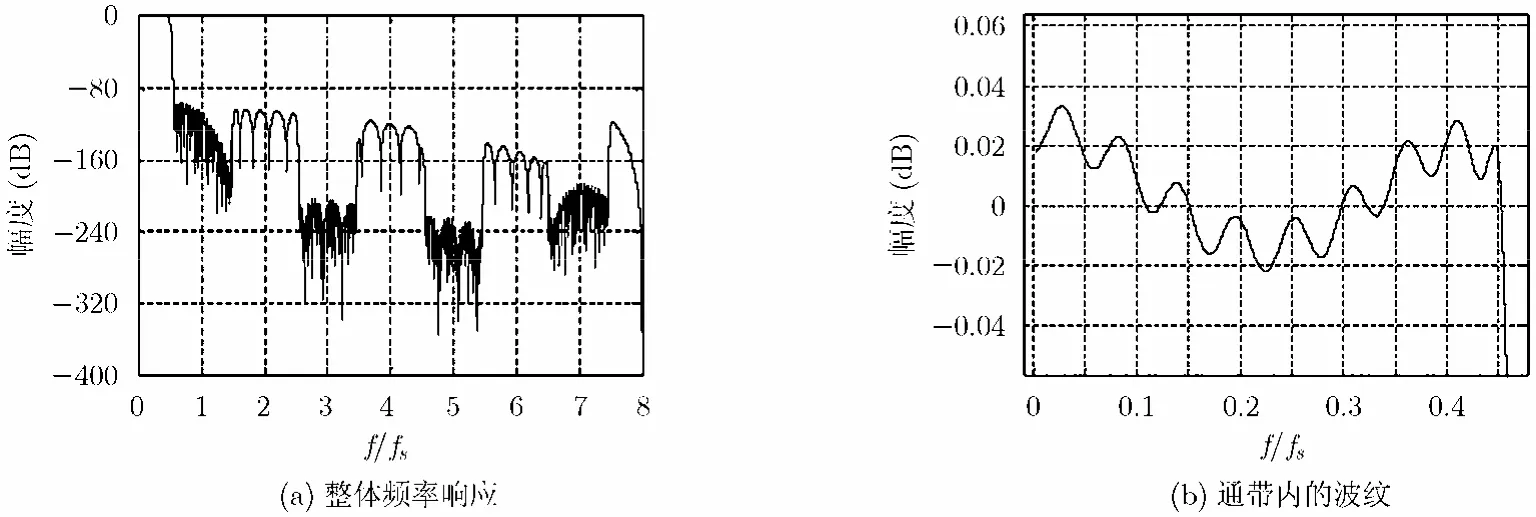

图6(a)给出了设计的3级插值滤波器的整体频率响应的仿真结果。图6(b)放大了整体频率响应的通带部分。从图6(b)的通带放大部分得到设计的插值滤波器的通带波纹在±0.04 dB内,满足音频设计需求。从图6(a)中可以看出阻带衰减低于-98 dB,给模拟开关电容滤波器留出较大裕量,降低了模拟电路的实现难度。

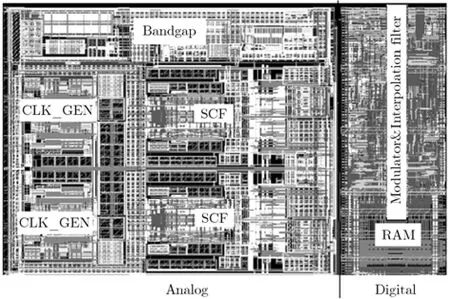

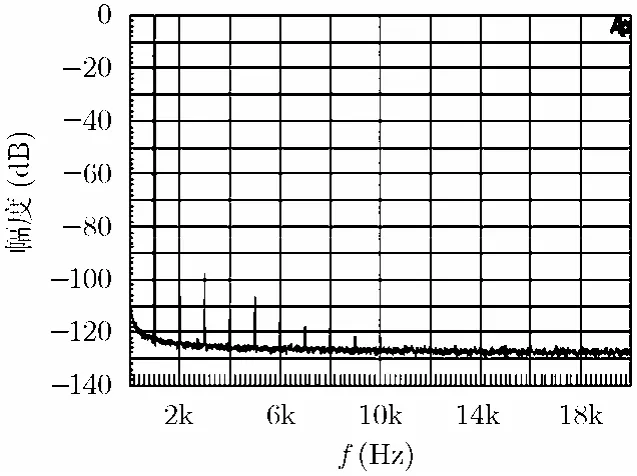

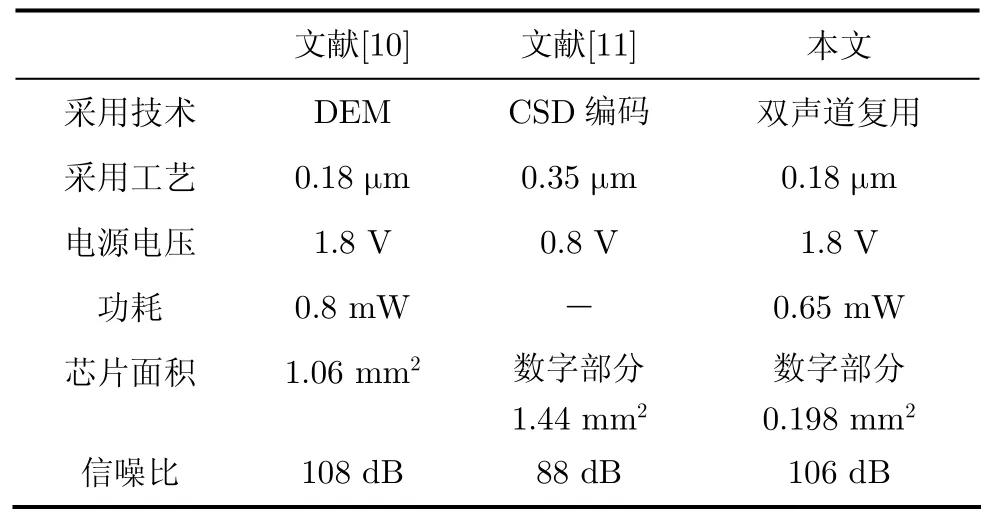

设计在 TSMC 0.18 μm 1.8 V/3.3 V 1P5M CMOS工艺上实现。版图如图7所示,其中左半部为两个声道的模拟电路,右半部分为数字电路,版图总面积为659 μm×1148 μm(0.756 mm2),数字部分面积为 659 μm×301 μm(0.198 mm2)。图 8 给出了1 kHz输入信号(0dB)FFT的测试结果,信噪比SNR为106 dB,输出动态范围为98 dB,数字部分的功耗仅为0.65 mW。数字部分的指标与文献[10,11]的对比如表1所示。在性能相当的情况下,本文设计的数字部分芯片面积与文献[10,11]相比都大大减小。

图6 插值滤波器的频率响应

图7 音频Σ- Δ DAC的版图

图8 芯片的测试结果

表1 本文与文献[10,11]中的指标对比结果

6 结论

本文给出了应用于双声道Σ- ΔDAC中新型小面积插值滤波器的设计方法。提出采用两个声道复用一个插值滤波器的方法来减小芯片的实现面积。第1级半带滤波器由一片RAM,一片ROM和一个乘加单元实现。第2级半带滤波器及第3级级联梳状滤波器采用延时单元加倍的结构,以便被两个声道复用;并给出重新排序方法来保证复用后两个声道的同步。提出的方法实现后,与性能指标相当的文献相比,数字部分芯片面积大大减小。

[1] Ben Ameur and Loulou M. Design of efficient digital interpolation filters and sigma-delta modulator for audio DAC [C]. The 3rd International Conference on Design and Technology of Integrated Systems, Nanoscale Era, March 25-27, 2008: 1-7.

[2] Coleman J. Signals and systems II: Part II: interpolation,decimation, complex signals, and Nyquist signaling [J].IEEE Potentials, 2010, 29(2): 40-45.

[3] 陈润,刘力源,李冬梅. 用于高精度Σ- Δ数模转换的多级插值滤波器的设计技术[J]. 半导体学报,2007, 28(11):1735-1740.Chen Run, Liu Li-yuan, and Li Dong-mei. A novel multi-stage interpolation filter design technique for high-resolution Σ- Δ DAC.Chinese Journal of Semiconductors, 2007, 28(11):1735-1740.

[4] Ben Ameur N, Soyah M, Masmoudi N, and Loulou M. FPGA implementation of polyphase decomposed FIR filters for interpolation used in Σ- Δ audio DAC[C]. 3rd International Conference on Signals, Circuits and Systems, Medenine,Tunisia, Nov. 6-8, 2009: 1-4.

[5] Richard A. An efficient hardware implementation for interpolating and decimating filters[C]. Conference on Signals,Systems and Computers, California, USA, Nov. 1-4, 2009:703-707.

[6] Mukhtar A, Jamal H, and Farooq U. An area efficient interpolation filter for digital audio applications [J].IEEE Transactions on Consumer Electronics, 2009, 55(2): 768-772.

[7] Luo Bin-ming, Zhao Yuan-fu, and Wang Zong-min. An area-efficient interpolator applied in audio Σ- Δ DAC[C].IEEE Conference on Signal-Image Technologies and Internet-Based System, Bali, Indonesia, Nov.30-Dec.3, 2008: 538-541.

[8] Schwingshackl D and Kubin G. Polyphase representation of multirate nonlinear filters and its applications [J].IEEE Transactions on Signal Processing, 2007, 55(5): 2145-2157.

[9] Laddomada M. Design of multistage decimation filters using cyclotomic polynomials: optimization and design issues [J].IEEE Transactions on Circuits and Systems I:Regular Papers,2008, 55(7): 1977-1987.

[10] Nguyen K, Bandyopadhyay A, and Adams B,et al.. A 108 dB SNR, 1.1 mW oversampling audio DAC with a three-level DEM technique [J].IEEE Journal of Solid-State Circuits,2008, 43(12): 2592-2600.

[11] Lee Kye-hyung, Meng Qing-dong, and SugimotoT,et al.. A 0.8 V, 2.6 mW, 88 dB dual-channel audio Delta-Sigma D/A converter with headphone driver [J].IEEE Journal of Solid-State Circuits, 2009, 44(3): 916-927.