视频图像实时采集和显示系统的FPGA设计

李兴富

LI Xing-fu

(桂林航天工业高等专科学校,桂林 541004)

0 引言

视频信息采集为视频图像处理、传输、显示等提供提供原始的数字图像数据,视频采集系统的性能是影响视频图像系统性能的关键因素之一[1]。随着人们对视频图像质量的要求越来越高,对视频采集系统的性能要求也将越来越高[2]。目前视频采集系统常用的处理器包括通用处理器、DSP和FPGA。尽管通用处理器能够处理许多任务,但是它们通常缺少执行复杂数据处理任务所需要的带宽,常因速度不够快而不能满足设计目标[3];DSP虽然内部利用专用硬件实现数字信号处理中的常用算法,运算速度很快,但其采用单指令执行系统,并且仅对某些固定的运算可以优化,因此灵活性不够; FPGA作为当今主流的大规模可编程集成电路,采用硬连线逻辑实现数据处理和运算,具有集成度高、速度快、性能稳定、开发周期短、便于改进升级等一系列优点,还能实现视频采集、图像显示的外围逻辑控制,在视频采集和图像处理方面具有独特优势。使用FPGA实现该类任务已成为很好的选择[4]。

本文采用FPGA作为视频图像实时采集和显示系统的核心控制器。首先对视频图像采集显示系统的构成、工作原理及技术现状做了简单介绍,然后叙述了各功能模块和接口电路的设计方法和过程,重点介绍了FPGA应用系统设计中一些难点问题的解决办法。

1 系统的总体结构及器件选择

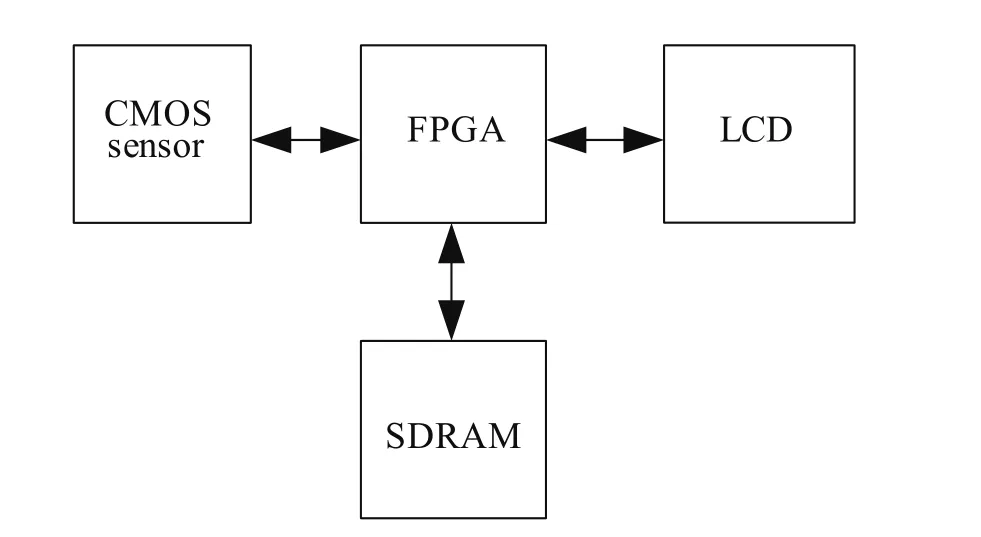

系统硬件框图如图1所示。其中,CMOS sensor为图像传感器,型号为MT9M111,用于实时接收视频信号;LCD的型号为TD036THEA3,用于实时显示视频图像; SDRAM采用ISSI公司的IS42S16400B,用于缓存视频数据;FPGA采用CycloneII EP2C35F672C8 ,作为整个系统的控制核心。

图1 系统总体结构框图

MT9M111是美光公司推出的集成CMOS传感器和图形处理器的SOC产品;130万像素分辨率(1280H×1024V),可以支持SXGA格式输出;嵌入的可编程图像处理器提供的功能包括色彩恢复和修补、自动曝光、白平衡、镜头阴影修正、增加清晰度、可编程灰度修正、黑暗电平失调修正、闪烁避免、连续调整滤光尺寸、平滑的数字变焦、快速自动曝光模式和不工作时缺陷修正等,可以通过两线串行接口对其进行配置。

EP2C35F672C8为Altera公司CycloneII系列FPGA芯片,在性能、功耗和性价比方面超越了第一代Cyclone系列。可以内嵌各种IP核,实现强大的控制处理功能;内嵌M4K存储器块,用于实现单端口RAM、双端口RAM、ROM以及同步FIFO和异步FIFO; 除了支持LVTTL、LVCMOS、SSTL等标准的单端I/O外,还支持LVDS、RSDS、mini-LVDS、LVPECL等标准的差分信号;支持四个可编程锁相环(PLL)和最多16个全局时钟线,还有对时钟管理和频率合成的能力。价格也比较适中,所以很适合作为大批量产品的解决方案。是视频处理低成本解决方案的理想选择。

IS42S16400B是ISSI公司的SDRAM产品。包含67,108,864bits,可配置为具有同步接口的四块DRAM。该SDRAM包括自动刷新模式、省电模式和掉电模式。所有信号在时钟信号上升沿保存。所有输入和输出与LVTTL兼容。内部块之间交错隐藏预充电时间,支持同步猝发数据传输方式。

TD036THEA3为3.6寸有源矩阵彩色TFT液晶显示模块,采用低温多晶矽硅TFT技术,分辨率为320×240,数据格式为RGB565,具体显示为QVGA模式,输出像素时钟为19.28MHz。

2 系统的FPGA设计

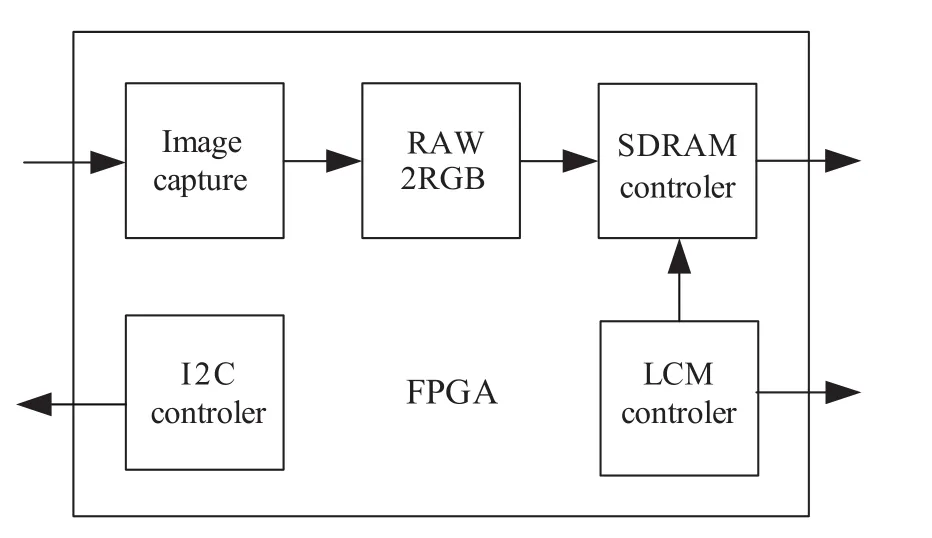

系统的FPGA设计模块图如图2所示。I2C controler模块用于通过I2C总线协议控制MT9M111的寄存器配置,使摄像头按照配置的模式工作,输出行场同步信号、像素时钟、图像数据。 Image Capture模块检测行场同步信号、生成写使能信号,在像素时钟的上升沿将视频数据采集到寄存器中。RAW2RGB模块将采集的数据转换成RGB信号,SDRAM controler模块用于控制数据的缓冲,将数据写入SDRAM。LCM Controller模块产生LCD控制信号,将SDRAM中的数据送到LCD上,这样就完成了视频图像的实时采集与显示。

设计中采用VerilogHDL进行编程,可以在抽象层对电路进行描述,而不必考虑特定的制造工艺,通过使用Altera公司QuartusII软件的逻辑综合工具能够将设计自动转换为任意一种制造工艺版图。

图2 FPGA模块图

2.1 I2C controler模块设计

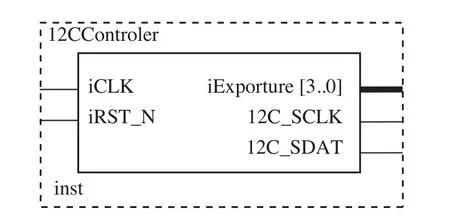

I2C controller模块是通过编写Verilog代码自定义逻辑实现的。模块图如图3所示。

图3 I2C controller模块

在该模块中,由于需要把I2C总线接口的SCL和SDA信号在系统时钟下同步,因此采用系统时钟iCLK对SCL和SDA信号进行三次缓冲,得到其上升沿和下降沿脉冲信号,便于状态机处理;状态机对I2C的读/写寄存器操作进行说明,状态包括器件地址部分、寄存器地址部分和数据部分。

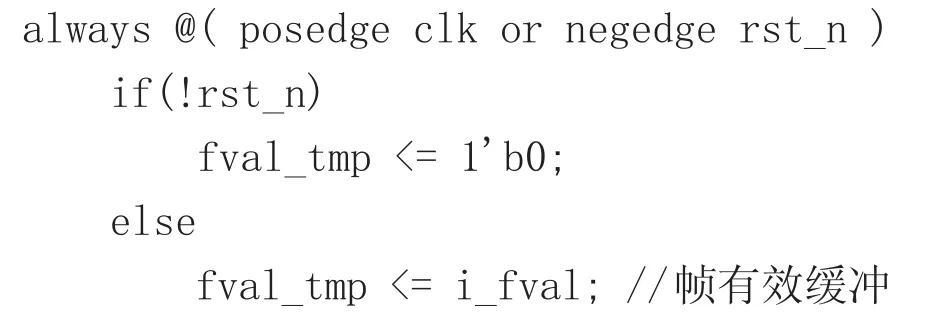

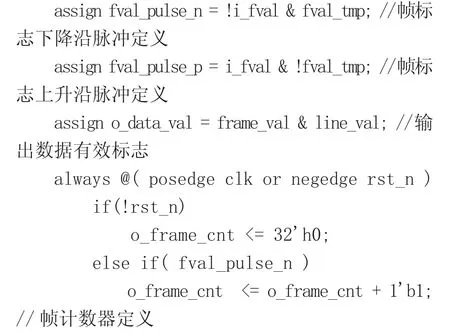

2.2 图像数据采集模块设计

在程序设计过程中,首先需要检测视频图像中帧标志的有效起始和结束,在判断到帧标志有效后,需要继续检测视频图像中行的有效起始和结束标志,在判断到行标志有效后,在像素时钟上升沿把图像的有效像素值存入存储器;同时,在帧标志的上升沿后,列计数器x_cnt清0,在行标志有效期间,对列计数器进行计数,记满1280为一行数据,行计数器加1;最后,输出数据的有效使能信号,供下一级图像格式转换模块使用。

部分源代码如下:

2.3 图像格式转换模块设计

由于在MT9M111图像传感器的配置中,采用原始的Bayer输出格式,使得其每次只产生一种颜色分量的响应值,而FPGA后续设计需要4∶4∶4的RGB颜色,因此需要对颜色分量进行处理。

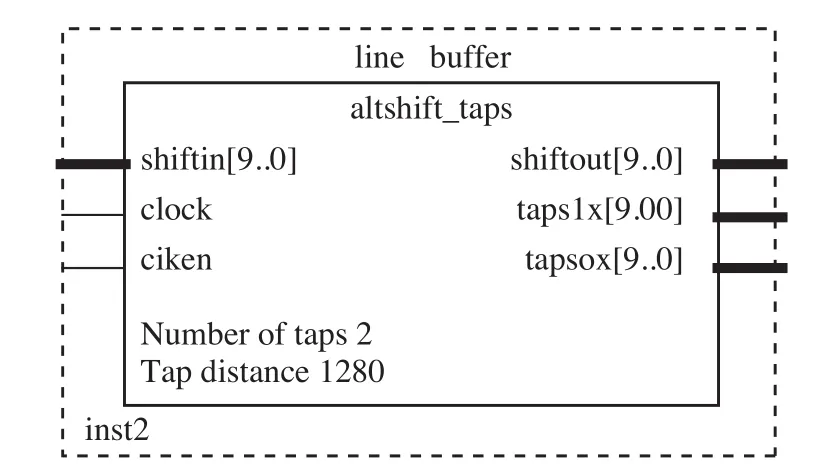

本模块设计需要大量的移位寄存器,如果全部采用FPGA内部的触发器串联构成的话,需要2560个10bit的触发器,会导致LE中的触发器资源紧张,可能会出现最终逻辑资源不够用的情况。在Altera FPGA中,内嵌的M512和M4K专用IP存储模块,可以被用来支持移位寄存器模式,不仅可以节省触发器资源,同时也减少了布线资源。通过调用Altera的IP核生成器产生移位寄存器,数据宽度为10bits,抽头数(Taps)为2,如图4所示。

图4 调用IP核生成移位寄存器

图5 存储器乒乓操作原理图

2.4 图像数据缓存控制模块设计

由 于MT9M111工作时钟为25MHZ,因此图像数据的接收、格式转换是在25MHZ时钟频率下进行的。而FPGA板上输入时钟频率为50MHZ,因此会产生异步时钟域问题。设计中采用异步FIFO进行数据缓冲。同理,由于液晶屏输出像素时钟频率为19.28MHZ,SDRAM控制器使用的时钟为输入时钟经过FPGA内部的PLL两倍频后的100MHZ,因此在SDRAM控制器与液晶屏显示控制模块之间也通过异步FIFO进行数据缓冲。

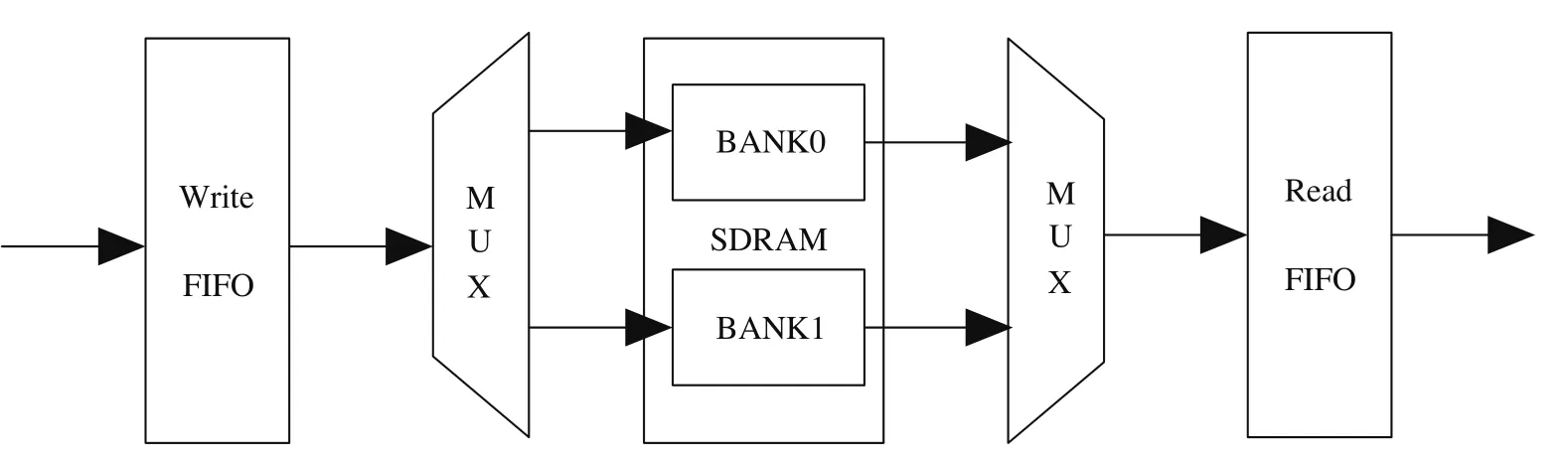

为了满足视频图像实时采集和显示的需要,视频数据的接收和显示需同时进行。而SDRAM作为单端口器件,不能同时进行数据的写入和读出。要实现同时读写,必须采用乒乓操作来完成,原理如图5所示。具体方法是通过设计SDRAM控制器接口和FIFO缓冲接口,轮流对一片SDRAM中的两块BANK进行操作,当传感器发送数据至SDRAM时,写入BANK0,此时显示控制可以从BANK1取数据,并且传感器发送一帧数据的时间与显示器取出一帧数据的时间相同;当传感器继续发送数据时,写入BANK1,同时显示控制可以从BANK0取数据,如此不断循环。这样就可以有效地利用和节省存储器资源,并实现视频图像的实时采集和显示。

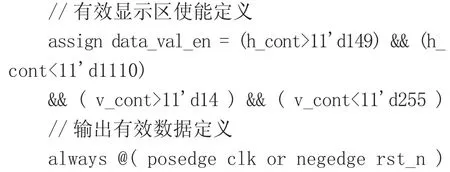

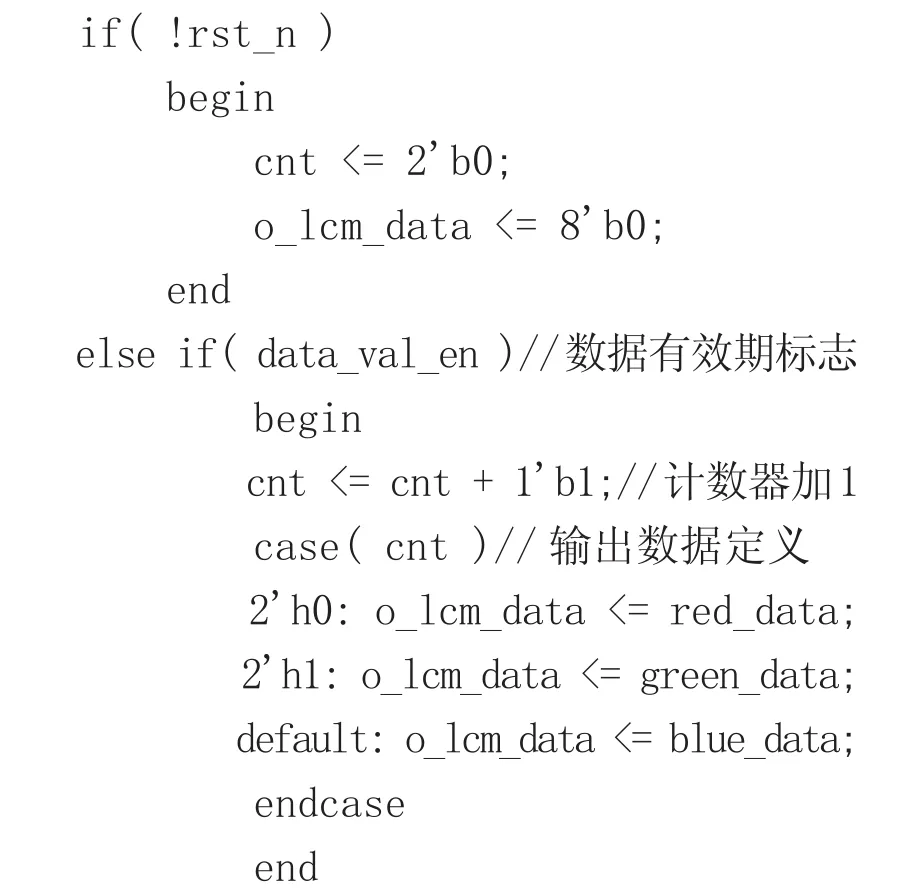

2.5 显示控制模块设计

显示控制模块LCM Controller用于按照TD036THEA3液晶屏的时序要求,产生输出帧和行控制信号,通过读取FIFO中的数据,输出RGB数据,完成液晶屏的显示控制。其时钟频率为19.28MHZ,是通过对系统时钟分频得到的。

部分实现代码如下:

图6 Image capture模块仿真测试时序图

3 系统的测试

通过编写测试代码,采用Modelsim仿真工具对整个FPGA中的各个模块进行仿真测试。图6为Image capture模块的仿真测试时序图,其他模块的仿真测试方法类似,不再赘述。

Image capture模块是系统中的关键部分,它根据MT9M111图像传感器输入的行有效信号、帧有效信号,采集像素数据,提供给后续模块进行格式转换、显示输出等。

如图中所示,输入时钟频率为25MHZ,在系统复位为高的情况下,当帧有效标志和行有效标志均为高时,对输入数据进行采样,同时x_cont计数器不断加一;当一行结束的时候,y_cont计数器加1,完成有效图像数据的采样。

通过对整个系统的实际测试,在50MHZ频率下,达到的指标如下:实时性:25帧/秒;最大功耗:3.5W。连续采集和显示视频图像的质量和稳定性也很高。

4 结论

本文介绍了一种采用FPGA作为核心控制器同时实现外围部件接口控制逻辑的视频图像实时采集和显示系统实例。叙述了各功能模块和接口电路的设计方法、测试方法。给出了异步时钟处理、调用IP核生成移位寄存器、SDRAM存储器乒乓式操作等FPGA应用设计中的一些难点问题的处理方法。通过仿真测试和实际验证,该系统在快速性、稳定性及体积、功耗、成本等方面均具有较优越的性能。表明,利用FPGA进行视频图像信息采集和显示系统设计,是降低产品体积、功耗,提高快速性、稳定性的有效途径。

[1]肖文才, 樊丰.视频实时采集系统的FPGA设计[J].中国有线电视, 2006(2l)∶ 2104-2108.

[2]韩相军, 关永, 王万森.嵌入式视频采集系统的设计与实现[J].微计算机信息, 2006, 22(1-2)∶ 26-28.

[3]Chris Roven.IP重用和嵌入式SOC开发的逻辑方法[J].电子产品世界, 2005(8)∶ 115-116.

[4]陈朗, 王瑞.MPEG-4系统中基于FPGA实现数据采集及预处理[J].微计算机信息, 2005, 2l(9-3)∶ 109-111.

[5]科夫曼.基于Verilog语言的实用FPGA设计[M].北京∶ 科学出版社, 2000.

[6]孙恺, 程世恒.NiosⅡ系统开发设计与应用实例[M].北京∶ 北京航空航天大学出版社, 2007.

[7]高韬, 赵建涛.视频压缩理论及其技术发展.电子技术应用[J], 2007 (11)∶ 3-6.

[8]尹德安, 李欣.基于FPGA的视频采集控制设计[J].微计算机信息, 2006, 22(9-2)∶ 159-160.