基于FPGA的TFT-LCD液晶显示模块设计

张超建,王厚军

(电子科技大学自动化工程学院,四川 成都 611731)

1 引 言

随着液晶技术的日益成熟,液晶显示屏(Liquid Crystal Display,简称LCD)在测试领域中得到了越来越广泛的应用,如今大部分新型示波器都采用了液晶显示屏。在各种LCD的产品中,薄膜晶体管液晶显示器TFT(Thin Film Transistor)LCD因其体积薄、重量轻、画面质量优异、功耗低、寿命长、数字化和无辐射等优点,已被广泛应用于各类图形显示系统。一般LCD显示都采用专用的液晶显示控制模块,实现屏幕分割、屏幕逻辑运算等复杂的图形功能。但这样必须要由DSP来控制显示模块,而且其刷新频率受到一定限制。而示波器的实时性要求非常高,对刷新率要求也就很高,并且液晶显示界面基本上只是显示框架和实时波形等简单的图形,所以设计中,LCD显示没有采用专用控制芯片控制显示,而是采用外部硬件现场可编程门阵列(Field Programmable Gate Array,FPGA)产生LCD所需要的各种显示控制时序。显示数据的读取也是由FPGA产生地址计数器,直接从显存SRAM中读取。

2 SRAM显存和TFT液晶简介

设计方案中SRAM选用ISSI公司的高速静态存储器IS63LV1024L,为能更好、更有效地设计其与FPGA的接口实现,首先必须要了解IS63LV1024L的性能特点。它是128K×8的高速静态存储器,性能特点主要包括:工作电压为3.3 V,高速接入时间一般分为 8ns、10ns、和 12ns,高性能,低功耗,输入和输出都与TTL相兼容,不需要时钟和更新的全静态工作过程以及通过选择CE和OE的状态可以比较简单地实现存储等。

为了正确地传输数据,在了解其性能特点的基础上,还须了解IS63LV1024L的读写状态的时序和使能的要求。其读写时序状态如图1所示。

TFT-LCD选用深圳市佳昀科技有限公司型号为YXM070TLW03的彩色显示屏,分辨率为800×480,是 18位数字彩色屏,26万色(262144),其中 R、G、B3色各占6位。内部集成了驱动芯片和背光单元,芯片供电电压3.3V,背光供电电压-10V。它的信号接口有电源、地、数据信号、数据使能信号和点时钟信号。电源接口和地接口在PCB制作阶段固定连接。液晶显示的时序信号(点时钟、行同步信号、场同步信号以及数据使能信号)都由FPGA送出。

图1 IS63LV1024L读写时序状态

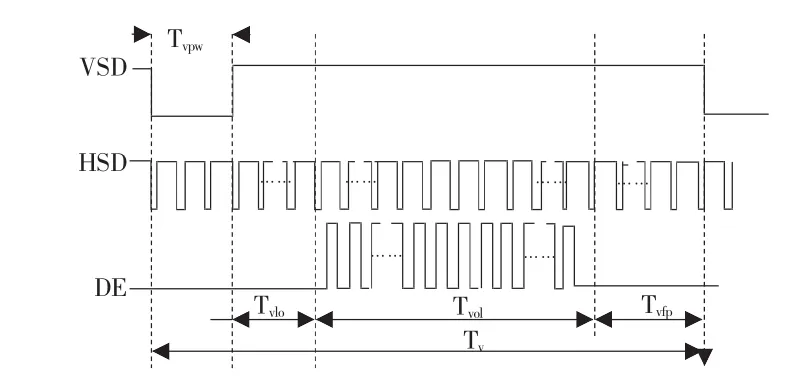

YXM070TLW03的点时钟典型值为30 MHz,占空比50%。场扫描时序以HSD为时钟基准,其中,VSD为场同步信号(帧同步),低电平有效。每扫描完一帧(480行),控制器将驱动VSD有效(低电平),有效宽度Tvpw为3个HSD。在VSD有效之前插入Tvfp(VSD Front Porch)场消隐前肩为13个HSD,有效之后插入Tvb(VSD Back Porch)场消隐后肩为29个HSD,这样场扫描信号就相当于对HSD进行525分频,其时序如图2所示。行扫描时序以DCLK(点时钟)为时钟基准,HSD为行同步信号。类似地,行扫描信号就相当于对DCLK进行928分频。由上述分析可知LCD的每场包括525行,其中480行为有效显示行。每显示行共包括928个点,其中800点为有效显示区。

图2 YXM070TLW03时序图

3 液晶显示控制方案

液晶显示驱动模块设计中,其硬件电路的搭建方案是基于电路连接、液晶时序控制和显示数据传输控制3个方面来考虑确定的。

电路连接:所选择的液晶3种颜色均由6位数据线组成,即液晶的数据线一共有18根,将它们与FPGA的I/O口相连。而此设计中采用的SRAM的容量为128K×8bit,受其约束实际上只用到其中的8根。采取数据线低位固定成无效电平的方式,只采用高几位数据来表示颜色信息。例如R(red)需要6位输入,只用到其中的3位,那么将LCD的R0、R1和R2接为高电平(无效状态),而R3-R5这3位数据和相应的数据线相连接,同样,G3-G5和相应的数据线连接表示G(green),B4-B5和相应的数据线连接表示B(blue),这样便将8位数据扩展成18位数据,此时LCD的色彩度为256,虽然整体显示效果会有影响,但其用作示波器的液晶显示已经足以满足实际需要。

液晶时序控制:液晶显示的时序图如图2所示,行同步信号周期应该为928个点时钟周期,场同步信号周期为525个行同步信号周期,液晶的刷新率为30 MHz/(928×525)=61 Hz,液晶时序模块通过对点时钟进行计数来实现行同步信号、场同步信号以及数据使能信号,从而实现液晶的时序控制。

显示数据传输控制:被测信号的信息经DSP进行相应的运算处理后,其数据最终要送去LCD以显示给用户。控制显存SRAM如何有序地写入数据和读出数据是关键,在这部分有两种方案可供选择,即系统的显示采用两片SRAM分时复用的方式驱动LCD显示或采用单片SRAM驱动LCD显示,下面对这两种方案做一简单的叙述比较。

方案1:系统的显示采用两片SRAM分时复用的方式。当显示SRAM1中所存数据时,下一次将要显示的数据可以事先存入SRAM2中,当前显示完成后,SRAM2中的数据就可以送去继续显示,而SRAM1将为下一次显示数据做准备。实际控制中,DSP处理器发出一选择信号,选择控制显示哪一片SRAM的数据,根据这个选择信号来控制两片SRAM的读写使能以及地址线。例如显示SRAM1中数据,SRAM2负责存入数据时,SRAM1设置成读使能有效,写使能无效,地址线指向显示数据区的首地址;SRAM2设置为读使能无效,写使能有效,地址线指着将要写入SRAM2那块数据区的首地址。

方案2:系统的显示采用单片SRAM驱动LCD的方式。被测信号的采样数据由DSP处理后经过硬件电路送到SRAM中暂存或LCD从SRAM中读出已存数据用来显示,显存写入数据和读出数据交替进行,由DSP发出的一控制信号对单片SRAM采取分时读写的方式。由图1所示的SRAM的读写时序状态图可知,CE为低电平时,片选使能输入有效。同时若WE为低电平,则写使能有效,读使能无效,地址线指着将要写入SRAM那块数据区的首地址,把将要用于显示的数据存入SRAM中。CE为低,同时WE为高、OE为低时读使能有效,写使能无效,地址线指向显示数据区的首地址,LCD读取SRAM中相应地址的数据送去显示。

方案1这一设计思路较为成熟,在实验室以往研发的其他型号示波器都是沿用此方案。而在该设计中,结合课题为某民用项目这一实际情况,在充分确保其高性能指标的前提下,综合考虑产品的成本、主板PCB的尺寸空间以及总体设计方案,最终选择了方案2这一新的设计思路。

这样不仅降低了控制的复杂度,同时也减小了硬件布板难度,节约了FPGA的I/O口资源,控制了芯片成本等,具有良好的社会效益和经济效益。

4 设计方案的实现

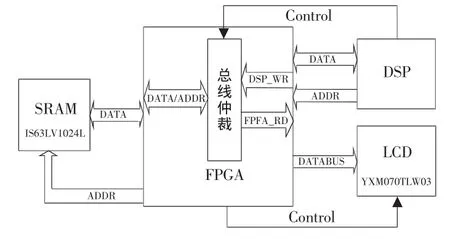

液晶显示控制电路由硬件电路来搭建,依据上述方案2,其硬件电路的结构框图如图3所示。其中,FPGA核心处理系统采用Xilinx公司的Spartan-3A系列,DSP(Digital Signal Processor)作为可编程数字信号处理专用芯片,选用ADI公司的ADSP-BF531。SRAM片选使能输入始终有效,解决SRAM分时读写切换控制问题的关键是由DSP发出的Flush控制信号和FPGA产生TFT-LCD所需的控制时序并完成总线仲裁逻辑。当Flush的值为低电平时,SRAM的写使能有效,DSP接管SRAM的控制权,DSP发出地址DSP_Sram_a[16∶0]经地址总线传送,并把处理过的新的显示数据内容Adsp_Databus_wr[7∶0]经数据总线由FPGA处理后写入SRAM的相应地址sram1_a[16∶0]中;当 Flush 的值为高电平时,SRAM切换为读使能有效,此时DSP释放SRAM的控制权,不再写入新的数据,使其处于等待状态。FPGA发送地址Lcd_Sram_a[16∶0]到SRAM,读出SRAM中相应地址的8位数据Sram_lcd_d[7∶0]送到FPGA做显示处理,然后通过FPGA与LCD之间的数据总线加载到液晶点阵显示数据,参考图4。

图3 液晶显示模块结构框图

图4 液晶显示控制仿真图

为了进一步验证所提出的这一液晶显示方案的可行性,对其进行了仿真,由图4的仿真结果可以看出符合设想,达到了预期目的。

5 在示波器中的实现

将该设计方案应用于实验室某系列款的数字存储示波器上,最终实现单片SRAM驱动液晶显示,如图5所示,正确稳定显示所需数据,可以满足设计预期的数据显示需求。7英寸显示屏,800×480像素使得其具有良好的显示效果和较高的性价比。

图5 液晶显示方案在示波器中的实现

6 结束语

该文提出了一种单片SRAM驱动LCD液晶显示的新方法,并在一款示波器中得到实现和应用。基于其节约了成本并有效降低了显示控制的复杂度,减小了电路板的尺寸,增强了系统的可靠性和设计的灵活性,使得此方案同样优先适用于以后的示波器开发和应用中。

[1]舒胜坤,王文慧,林 树.基于FPGA的TFT-LCD数字显示控制器设计[J].电视技术,2008,48(6):52-55.

[2]苏 兢,杨志义,韩芝侠.基于FPGA的数控系统LCD控制器设计与实现[J].科学技术与工程,2007,7(5):765-768.

[3]谢 敏.双口RAM在大屏幕LED显示系统中的应用开发[J].电子工程师,2005,31(6):43-45.

[4]李 卫,王 杉,魏急波.FPGA与外部存储设备的接口实现[J].世界电子元器件,2004(2):67-69.

[5]朱耀东,张焕春,经亚枝.基于FPGA的一种高速图形帧存设计[J].电子技术应用,2003(2):72-74

[6]朱耀东,张焕春,经亚枝.基于FPGA的LCD&VGA控制器设计[J].电子技术应用,2002(11):44-46.

[7]田 耕,徐文波,胡 彬.ISE Design 10.x FPGA开发指南[M].北京:人民邮电出版社,2008.

[8]李维諟,郭 强.最新液晶显示应用技术[M].北京:电子工业出版社,2006.

[9]陈 峰.Blackfin系列DSP原理与系统设计[M].北京:电子工业出版社,2004.

[10]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.