CMMB标准中RS编码的FPGA实现

栗芬环

(华南理工大学 电子与信息学院,广东 广州 510640)

1 概述

广电局颁布的移动电视传输标准CMMB中,信道传输协议是重要的组成部分[1]。其中,前向纠错码(FEC)在信道传输中尤其重要。RS纠错码是FEC的重要组成部分。RS编码是多元BCH码的一种[2-3],在线性分组码中,它的纠错能力和编码效率都是最高的。在短码和中等码长的条件下性能接近Shannon限。本文着重介绍标准中RS的特点、编码的FPGA实现。

2 CMMB标准中RS编码的特点

根据标准描述,RS编码和字节交织是列输入和列输出,按行编码的方式进行。RS码长为240 byte的RS(240,k)截短码。 该码由原始的 RS(255,M)系统码通过截短产生,其中M=k+15。k为一个码字中信息序列的字节数,校验字节数为(240-k)。 RS(240,k)码有 4 种模式,分别为 k=240,k=224,k=192,k=176。RS 码的每个码元取自域GF(256),标准选择的生成多项式为

产生截短码的过程为:

1) 在 k 个输入信息字节(m0,m1,…,mk-1)前添加 15个全“0”字节,构造为原始的 RS(255,m)。 系统码的输入序列为(0,0,…,0,m0,m1,…,mk-1)。

2) 编码后生成的码字为(0,0,…,0,m0,m1,…,mk-1,p0,p1,…,p255-M-1)。

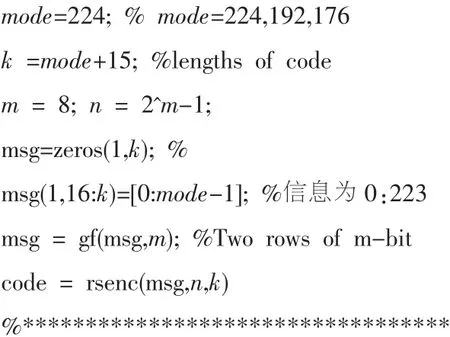

从码字中删去添加的字节,得到240 byte的RS截短码。为验证标准中的系数与设计实现是否一致,编写Matlab验证代码为FPGA提供验证数据源。对mode=224,设计信息为从0~223,共224个信息字节。编码所采用的Matlab程序如下:

余项结果如下:

Columns 225 through 240246 90 157 163 59 74 124 45 229 106 182 124 69 49 50 11

3 RS编码电路

对于RS编码,存在软件编码和硬件编码方法。软件编码可以采用信息字节m(x)和生成矩阵G(x)相乘得到码字[4]。硬件编码常采用线性移位寄存器(LFSR)电路实现。

图1给出了标准中RS(240,176)的硬件编码电路,实现了多项式的乘法和除法运算[5]。采用该电路组成的编码器在初始化时,需要对寄存器清零。信息字节的高位先进先出,通过开关A和B进行选择。编码开始时,开关打到A。当k个信息字节全部进入编码器后,开关打到B处。此时,LFSR把0不断地从左边的r0移进编码寄存器。这一过程完成了两项操作:余项从B开关处读出的同时进行了寄存器的清零。经过N个周期(标准为240)即可完成对k个信息字节的编码。此后对后k个信息字节进行编码的时候就不需要重新对寄存器清零。

上述电路都采用了有限域的乘法器,其系数由生成多项式产生,标准中产生系数的办法如下

不同于标准DVB-C/T的生成多项式[4]为

设计符合k=224,k=192及k=176三种模式的编码模块。为了提高综合效率,只须针对k=176设计,节约编码成本。对于k=224及k=192模式,只须加载不同的乘法系数即可。例如,对于k=192模式,系数g0~g15为0,系数g16~g63加载k=192时对应的有限域乘法系数。对于k=224 模式,系数 g0~g47为 0,系数 g48~g63加载 k=224 模式下对应的有限域乘法系数。

图2为编码器硬件模块结构。控制模块发出协调信号,控制字节交织(采用RAM实现)和编码通路选择,以达到编码流水线操作。

控制模块发送有效数据至LDPC编码模块之间的时序关系如图3所示。

RS模块与LDPC模块之间数据通信通过ldpcen信号、ldpcz信号与data信号。当ldpcen信号拉高,告知LDPC模块开始复位,准备接受RS编码模块发送的数据。当ldpcz信号拉高一个周期,意味着RS模块发送的数据有效,直至ldpcen信号拉低。

对设计模块进行FPGA综合验证,综合工具为QuartusII6.0;功能仿真工具为Modelsim6.1。器件选择EP2S30F484C3。综合结果为:Total ALUTs为1 572,占用6%;Total Memory bits为 1 049 600,占用 77%。

综合结果符合标准的字节交织深度最大为432,则432×240×8=829 440。 使用了 FPGA 内部 2 片 65 536×8 bit的RAM组成,从而占用了大量的内存。

功耗分析结果如下:设置device power characteristics为typical,工作温度为25°。静态功耗为367.5 mW,动态功耗为71.33 mW,I/O热功率为27.78 mW,分析结果可信程度显示为高。

可见,为降低功耗以及成本,经过FPGA验证后,有必要采用ASIC流程进行芯片设计。给出其中k=224编码模块的经QuartusII综合布线后仿真波形(见图4):设置时钟频率为 85 MHz; 余项数据为 246,90,157,163,59 74,124,45,229,106,182,124,69,49,50,11,与 Matlab 编码结果数据一致。

4 FPGA验证

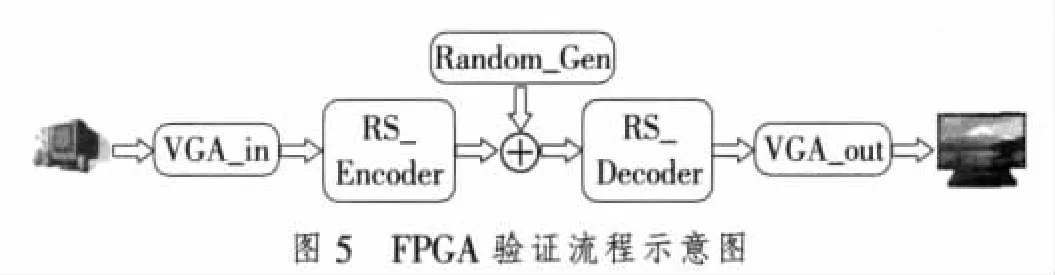

CMMB RS编码器的验证由随机验证和FPGA上板测试组成,随机验证通过Matlab平台产生随机函数,通过Modelsim验证平台读入随机数据,并灌入所设计的Verilog模块,输出写成txt文本,由Matlab平台读入校验[5]。实时编码硬件验证需要把Quartus生成的bitfile下载到Altera EP2S30F484C3中。为方便验证,直接使用了计算机VGA输出作为动态编码数据源,通过对数据流“编码-解码-重现”的过程,验证信道编码的正确性。FPGA验证流程如图5所示。

图5中,ERC为error rate calculate模块。经过 “编码-解码-重现”,当随机错误产生器产生的加性误码干扰在信道RS编码纠错范围外,显示图像存在杂点(误码干扰)。当随机错误产生器产生的加性误码干扰在信道RS编码纠错范围内,显示图像无杂点(无误码干扰),如图6所示。

5 小结

笔者对移动多媒体新标准RS码特点进行了分析,采用Verilog语言实现编码的FPGA验证与实现。结合标准中FEC特点,编码硬件模块在字节交织的同时进行数据发送,实现流水线操作,以此减少相应的等待延时。结合CMMB编码特点,结合RS编码原理,只须设计k=176编码器,通过加载不同信息长度的编码系数,实现k=224,k=192模式下的RS编码。并通过“编码-解码-重现”验证了RS编码器的实际工作效果。

:

[1]国家广播电影电视总局.GY/T 220.1-2006中华人民共和国广播电影电视行业标准[S].2006.

[2]梁炜新,王群生,牟刚.基于FPGA的通用RS编解码器的VHDL设计方法[J].电视技术,2004,28(3):16-20.

[3]王新梅,肖国镇.纠错码原理与方法[M].西安:西安电子科技大学出版社,2001.

[4]马红学,刘青.RS编码器的CPLD实现[J].电视技术,2002,26(10):52-54.

[5]栗芬环.Matlab和Modelsim数字前端设计、仿真验证平台[EB/OL].[2010-02-10].http://www.leaderstudio.cn/meeting/qth/14th/other1.html.