核级控制系统主控制器高速通讯总线技术的研究

姜群兴,胡立生

0 引言

核级(安全级)数字化控制系统是核电数字化仪控系统的重要组成部分。当非安全级控制系统失效时,它用于保护核反应堆的安全屏障的完整性,当反应堆安全重要参数超过安全极限时,它触发反应堆紧急停堆系统和/或专设安全设施,因此,核级控制系统的可靠性成为了核电数字化仪控系统的关键,而其在很大程度上决定于主控制器的可靠性。类似于常规工业的数字化控制系统(DCS),为提高主控制器的可靠性,核级控制系统采用各种冗余机制来实现主控制器的可靠性。以目前主流的核级控制系统为例,AREVA核级控制系统(Teleperm XS)采用输出仲裁的方法来实现主从控制器的冗余,而西屋的Common Q和三菱的核级控制系统,都采用从机备份主机寄存器及输出仲裁的方法,来实现多主控制器的冗余方式。采用备份主机寄存器的冗余方式,可以实现主从机之间的无扰切换,从而大大提高系统的实时性及可靠性[1]。

主从控制器之间寄存器备份的关键,是需要提供 CPU之间、CPU与北桥之间的高速数据通道。由 Intel公司和AMD公司推出的第三代高速串行通讯总线Hyper transport总线和PCI Express技术,为主控制器CPU与北桥的通讯提供了高速通道。本论文以第三代核级控制系统主控制器技术为参考,并结合自主研发的核级控制系统主控制器的特点,研究基于寄存器数据备份的新一代核级控制系统主控制器的通讯技术。

1 Hypertransport和PCI Express总线的技术特点分析及其优势

新一代核级控制系统主控制器采用了Hypertransport和PCI Express通讯总线技术,首先我们来介绍下这两种通讯总线的技术特点和它们相比普通通讯总线所具有的优势。

1.1 Hypertransport和PCI Express总线的技术特点

Hypertransport总线设备包括端接口和用户接口,端接口连接的是点对点的单向传输的Hypertransport链路。数据链路有两条,分别负责接收和发送。每条链路由数据路径、控制信号线和时钟信号线组成。每条链路的数据路径可由2到32的数据线组成,但是标准的数据线数量是 2、4、8、16、32。数据信息、命令信息和控制信息共用数据路径传输[2]。Hypertransport总线的一般工作在400MHZ时钟频率下,但是 HyperTransport采用类似 DDR的工作方式,所以在400MHz工作频率下,相当于800MHz的传输频率。又由于Hypertransport采用双向传输,在400MHZ的工作频率下,32位带宽的数据路径可达到6.4G的传输速度,计算方法为:400MHz×2×2×32bit÷8=6.4GB/sec[3]。

PCI Express总线也采用了点对点串行连接的方式,每个设备都有自己的专用连接,不需要向整个总线请求带宽,这样就可以把数据传输率提高到一个很高的频率。相对于传统 PCI总线在单一时间周期内只能实现单向传输,PCI Express的双单工连接能提供更高的传输速率和质量[4]。PCI Express采用串行数据包方式传递数据,这样PCI Express接口每个针脚可以获得比传统I/O标准更多的带宽。由于这些优点,PCI Express技术的传输速度可达到5G/s。在兼容性方面,PCI Express在软件层面上兼容目前的PCI技术和设备,支持 PCI设备和内存模组的初始化,也就是说采用了PCI Express技术后目前的驱动程序、操作系统无需推倒重来[5]。

Hypertransport和PCI Express通讯总线技术的数据传输采用的是差分传输的方式,跟USB等数据传输类似。传输过程使用1.2伏的电压,传输时,当A线高于B线电压时我们认为是逻辑‘1’,如果B线电压高于A线电压时我们认为是逻辑‘0’。采用差分方式传输可以提高抗共模噪音能力。

1.2 Hypertransport和PCI Express总线的优势

HyperTransport和PCI Express是高速、高性能的通讯总线。它们相比普通的通讯总线(如PCI,PCI_X等)有着更高的传输速度,HyperTransport通讯总线的速度可达到6.4G/s,PCI Express通讯总线也可达到5G/s左右的速度。有了高速的通讯总线我们才有条件实现主从CPU之间的寄存器备份,实现基于寄存器备份的主从热冗余机制,通讯总线速度的提高可以提高CPU读写内存和外设的速度,可以提高整个控制器的运行速度和响应速度,这样就可以从根本上提高整个核级控制系统的响应速度。

Hypertransport通讯总线技术具有故障安全性。Hypertransport通讯总线采用二线制多通道通讯,当CPU检测到任何一个通道的故障,都可以通过自动配置通道数,来实现原有的通讯功能。Hypertransport的通讯速度远远高于主控制器冗余对数据交互带宽的需求,那么任何一个通道的故障,剩下的通道仍然能满足主控制器数据交互的需求。

第三代通讯总线是串行传输数据的,相比普通的通讯总线减少了高速线,降低了PCB布线的难度和硬件设计的成本。第三代通讯总线采用了差分传输方式,提高了抗共模噪音能力。第三代通讯总线还采用了点对点单向传输的方式,提高了抗干扰的能力和传输的稳定性。而且在软件层面上,它们还兼容普通通讯总线的设备与技术。

总之,第三代通讯技术符合核级控制系统主控制器设计的要求,是国家实现自主研发核级主控制器的关键之一。

2 核级主控制器的高速通讯总线总体结构

核级控制系统主控制器根据冗余机制的需要来选择通讯技术和总线机构,因为通讯总线技术很大程度上决定了核级控制系统的冗余机制,下面我们介绍几种冗余机制。

常规的工业控制系统通常采用基于输出仲裁的主从热冗余机制,当仲裁设备检测到主控制器输出数据出现异常时,把通讯总线切换到从控制器上。常规工业控制系统采用这种方式主要是由于普通通讯总线速度的瓶颈。西门子的冗余机制就是冗余的从控制器不断备份主控制器的数据,并监视主控制器的输出,当从控制器发现主控制器输出数据出现问题时,从控制器把主控制器与整个控制系统隔离,并取代主控制器开始工作。而随着通讯总线速度和性能的提高,基于寄存器备份的主从热冗余机制已经成为核级数字化控制系统主控制器技术的发展趋势。新一代的核级控制系统控制器是采用寄存器备份的方式,我们在主从控制器的CPU之间建立一个高速的通讯通道,从控制器不断备份主控制器的寄存器的内容,一旦发现主控制器出现问题,从控制器把主控制器与整个控制系统隔离,并取代主控制器开始工作。

因为新一代的核级控制系统控制器采用寄存器备份的方式,所以我们在设计控制器时,围绕CPU构建的通讯总线结构如图1所示,CPU与内存、CPU与北桥之间的通讯可采用Hypertransport通讯总线技术,北桥与南桥之间的通讯可采用PCI Express通讯总线技术。因为南桥与外设之间的通讯不需要很高的通讯速度,南桥与外设之间的通讯可采用普通的并行总线。主从控制器的CPU之间有一条高速通讯通道,用于备份数据,采用Hypertransport通讯总线技术实现。北桥芯片和南桥芯片我们都用 FPGA芯片设计,用FPGA来实现Hypertransport通讯接口设备和PCI Express通讯接口设备,并在北桥的FPGA内部实现Hypertransport通讯接口设备和PCI Express通讯接口设备的连接,使它们之间能进行信息的传输[6]。

图1 核级控制系统主控制器总体架构

3 Hypertransport和PCI Express总线接口的设计

上面介绍了通讯总线的结构,通讯总线接口是实现通讯总线功能的关键。现在我们介绍在 FPGA中实现Hypertransport总线接口和PCI Express总线接口的方案。

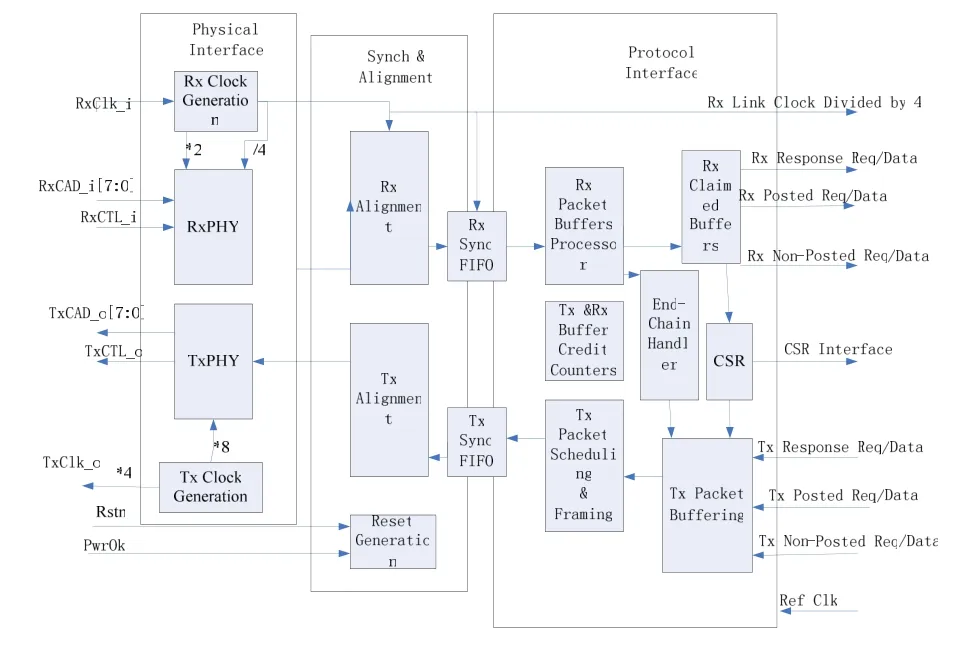

3.1 Hypertransport总线接口的FPGA结构

Hypertransport体系结构包括三部分:物理接口层(Physical Interface),同步对齐层(Synchronization and Alignment)和协议接口层(Protocol Interface)。如图2所示:

图2 Hypertransport总线设备的体系结构

物理接口层的功能是把 Hypertransport数据链路和Hypertransport核连接起来。它包括接收和发送两部分。接收模块从RxCTL_i、RxCAD_i数据线上接收串行的数据,然后把数据转换成并行数据并传输给同步对齐模块。Rx时钟产生器产生一个两倍于 RxClk的时钟信号。接收模块在该时钟信号的控制下读取RxCTL_i、RxCAD_i数据。

发送模块从同步对齐层得到并行数据,然后把并行数据转换成串行数据,再把串行数据发送到Hypertransport数据链路上。数据进入这个模块时已经被分到了不同的通道上。Tx时钟产生器产生一个两倍于同步对齐层的时钟信号。发送模块在该信号的控制下发送串行信号 TxCTL_i、TxCAD_i。

同步对齐层负责完成链路时钟域与用户接口时钟域间的同步,以及实现数据边界对齐、CRC生成和检测等处理过程。同步和对齐层采用CRC编码来确保传输数据的可靠性。

协议层的功能是调度数据边界对齐后的数据流,维护虚通道缓冲区,与用户接口进行交互。协议层有三个全双工的虚拟通道来与用户进行交互。分别为:Non_posted Requests(要求回复的请求,包括读请求和部分写请求),Posted Requests(不要求回复的请求),以及Response(对Non_posted Requests的回复)。Hypertransport协议层接口,与PCI Express设备接口配置兼容,这使我们能把Hypertransport接口和PCI Express接口连接起来。

3.2 PCI Express总线接口的FPGA结构

PCI Express体系结构包括四部分:应用接口层、传输层、数据链路层和物理层。如图3所示:

图3 PCI Express总线的体系结构

物理层的功能是把数据打包并发送到总线上或者从总线上接收并解析收到的包。

数据链接层采用按序的方式交换信息包,信息包是由传输层生成,按CRC校验进行数据保护的包。这些信息包的内容以及校验信息存储在数据链接层的缓存内。这样可以确保信息的传输不受电子噪音干扰。

传输层位于数据链路层和应用层之间,从应用层接收读写请求并创建请求包给数据链路层,所有采用封包形式的请求都会被分别处理。同时,传输层也接收来自数据链路层的响应包,并与应用层中的原始请求进行匹配。所有的包都有唯一的标志来匹配相应的请求和响应,这些包中也含有如优先级、松散排序等属性选项,系统根据这些属性在I/O系统中为这些包找到最佳传输路径。

应用层主要用来产生对外设的读写请求。与其他设备之间的链接,例如我们核电控制器中,与Hypertransport设备连接。

3.3 Hypertransport和PCI Express 通讯总线接口的设计

我们选用Altera公司提供的Stratix II GX芯片。它是Altera公司设计的大规模高端 FPGA,适合高端设计的应用。该芯片为设计工程师提供了完善的Hypertransport和PCI Express的开发平台。并且使用它的开发平台得到的总线接口与业界标准相一致。

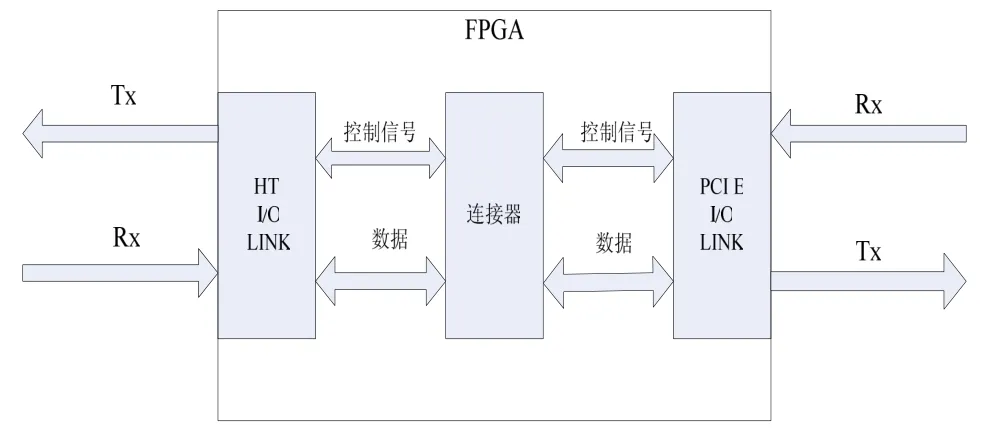

FPGA内部主要由三部分组成:Hypertransport总线接口,PCI Express总线接口和连接器。如图4所示:

图4 FPGA内部的结构

Quartus II 8.1软件的Magafunction中提供了Hypertransport总线接口和PCI Express总线接口的模块,而且Magafunction提供的模块一般在速度和面积上都比我们设计的模块好很多,所以我们只要会使用它提供的Hypertransport总线接口和PCI Express总线接口的模块就可以了。我们设计的方案是首先建立一个顶层文件,把Magafunction提供的Hypertransport接口模块和PCI Express接口模块嵌入到我们的顶层模块中来,然后我们再自己写一个连接器,把Hypertransport总线接口和PCI Express总线接口的控制总线和数据总线连接起来。

Hypertransport总线接口从Hypertransport链路上接收串行的信号,然后转换成并行的信号,并对信号进行解析,如果是需要传给PCI Express接口的就把信号通过连接器送给PCI Express总线接口,同时Hypertransport总线接口还可以通过连接器接收PCI Express总线接口传来的数据,再把数据发送到Hypertransport总线上去。同样,PCI Express总线接口既可把Hypertransport接口传来的数据输出到PCI Express总线上,也可以接收外部PCI Express总线上的数据,并把它传给Hypertransport总线接口。

4 结语

本文对第三代通讯总线Hypertransport和PCI Expres在核级控制系统主控器中的应用进行了初步的研究,并给出了我们的设计方案。Hypertransport和PCI Express通讯总线的应用是未来核电保护系统通讯总线的发展方向,但是我们对于这些第三代通讯总线的研究使用还处于初步的研究阶段,在未来研究的道路上,我们还需要付出更多的努力。

[1]IEC 60880-2006:Nuclear Power Plants-Instrumentation and Control Systems Important to Safety-Software Aspects for Computer-Based Systems Performing Category A Functions[S],International Electro Technical Commission.May-2006.

[2]Anderson Don, Trodden Jay.Hyper Transport system arthitecture[M].Mindshare InK,Addison Wesley,2003.

[3]裘嵘,郭御风,江泓,等.新型高性能互连技术Hyper Transport研究[J].计算机应用研究,2004,21(5):258-260.

[4]David Mayhew and Venkata Krishnan,PCI Experss and Advanced Switching:Evolutionary Path to Building Next Generation Interconnects,StarGen,In c,2 003.

[5]胡鹏,李琼,郭御风,徐炜遐,新一代IO互连PCI Express体系结构研究,第九届全国计算机工程与工艺学术年会论文集,2005.

[6]Detail Stage 4 of the Process Engineering Description for Safety Instrumentation and Control (Concept Report Level 4).TIANWAN NPP Requirement Specification,PG L52/LYG/2001/48f.July-2005.