基于PC104Plus的超短波监测系统数据采集平台设计

康 凯,钟子发,叶春逢,胡 磊

(电子工程学院,安徽 合肥 230037)

0 引言

超短波电磁环境的复杂性和现场环境的多样性,对超短波频谱监测接收机中数据采集系统的硬件和软件设计提出了更高的要求:小型化与便携,较高抗振动冲击的能力,兼容性和散热性好,高可靠性和可维护性等。PC104Plus总线以针孔堆叠方式组成,具有结构紧凑、抗震性好等优点,可以工作在恶劣的工作环境下,与PCI标准兼容,数据传输速率高(132Mb/s),可满足大部分高速数据传输应用需求。本文介绍了基于CPLD芯片和PCI总线控制芯片搭建的高速数据采集系统的硬件设计和软件设计[1],该系统的数据采集部分采用模块化设计,可灵活配置具有不同采样速率和采样位数的采集卡。

1 系统硬件设计

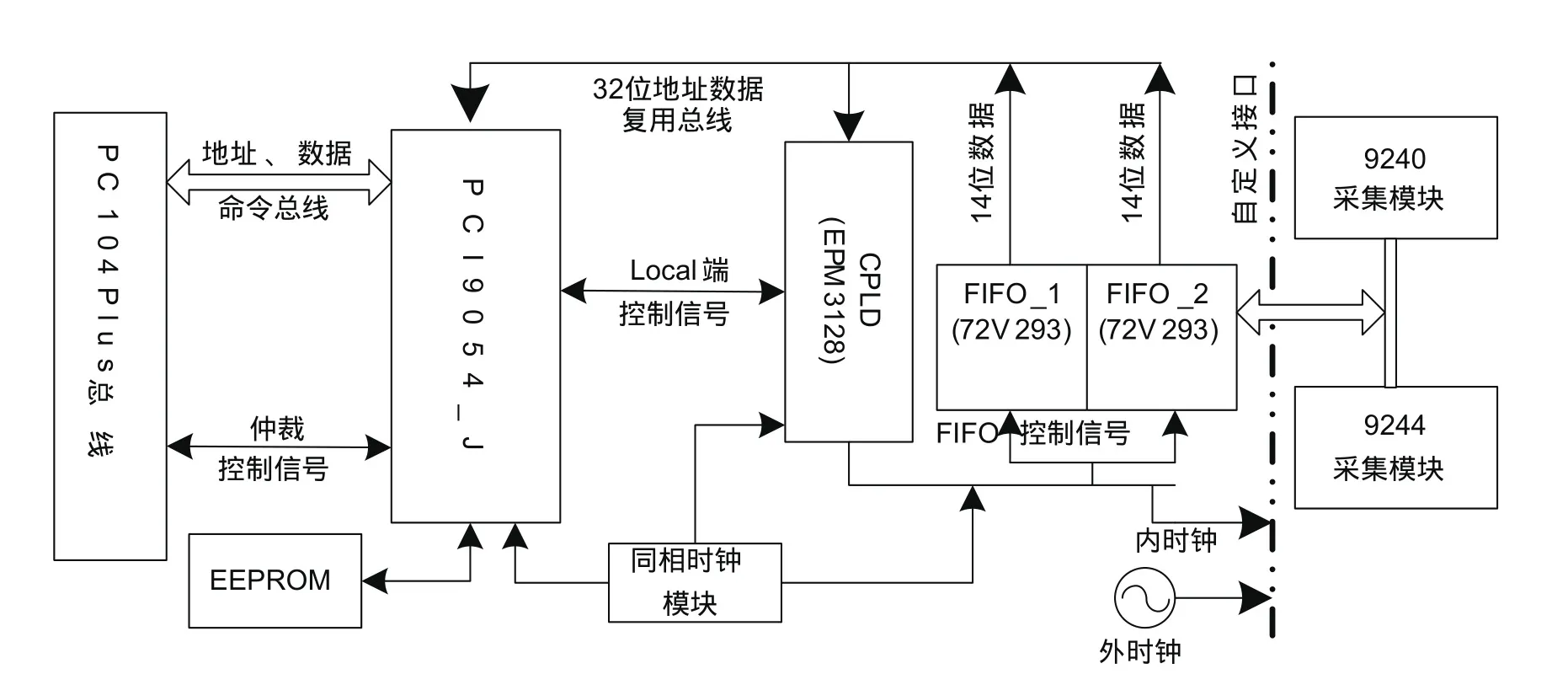

基于PC104Plus的双通道数据采集系统由PCI接口模块和数据采集模块组成[2],其多速率不仅体现在上位机程序可以方便地以软件方式设置采样率,同时由于采用了模块化设计,本系统的采集部分可灵活根据实际应用选配,如以AD9240(10MHz、14Bits)为核心的采集模块、以AD9244(65MHz、14Bits)为核心的采集模块等,各模块与PCI接口模块以自定义接口互连。

本系统的主要工作原理是:首先,用户发起采集命令,双AD通道开始采集数据,CPLD根据上位机程序的设置来控制数据采集的长度、采样频率等参数。采集的数据由FIFO(IDT72V293)缓冲,当采集的数据达到用户设置的要求时触发PCI9054的#LINT从而产生一个Local中断,告诉CPU数据已经准备好,驱动程序处理此中断并利用事件通知和测试程序通信,测试程序开始以IO方式读FIFO;或者,启动DMA传输,数据以DMA方式从FIFO传至内存。当采用DMA方式转移数据时,驱动程序需处理DMA完成中断并利用事件通知测试程序进而完成指定数据搬移和处理。值得注意的是,在硬件设计过程中,PCI9054的Local端时钟与CPLD逻辑控制时钟以及FIFO的读时钟三者的同步问题需要妥善处理。本系统中通过零延迟高速时钟分路器(CY2308)完成了这一工作(见图2)。

2 逻辑控制设计

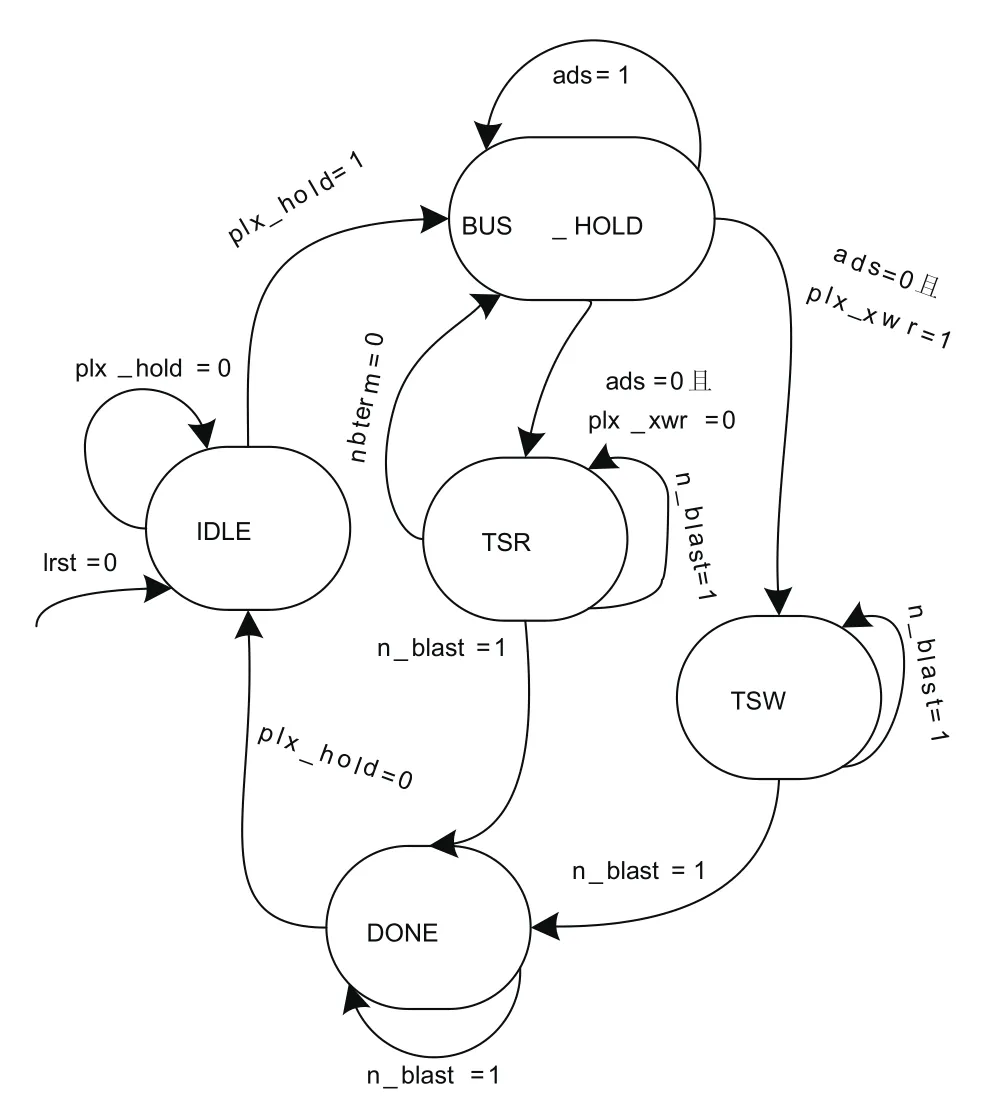

CPLD芯片是FIFO和PC104Plus总线之间能够正常进行数据传输的枢纽。为了配合本地总线接口电路实现与PC104Plus总线的高速数据传输,一个稳定性好、效率高的时序逻辑设计是很重要的。本系统基于EPM3128,采用Verilog HDL语言设计时序逻辑实现了FIFO和采集模块的控制以及FIFO和PCI总线桥接器PCI9054之间的普通传输和高速DMA传输[3]。为了保证输入在确定的状态下有效,并保证在输入稳定时使用信号进行逻辑判断,从而避免综合器在编译形成电路后状态机在实际运行过程中产生误动作。本设计给主要的输入信号加上了门控使能(该门控信号由状态向量译码得到),这样便只有在使能信号有效时才会有可用输入,而不会出现不确定情况。本文基于开发环境Quartus II 4.2设计的时序逻辑主要包括Local端状态机与FIFO和采集模块的控制[4](见图3)。

图1 系统硬结结构

图2 同相时钟分发电路

图3 PCI9054的本地端逻辑状态转换图

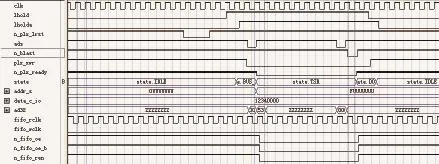

图3 所示的状态机经实际检验,可以满足PCI9054从模式单周期读写、从模式突发读、从模式DMA读三种时序要求(见图4、图5、图6),运行稳定[5]。其中,单周期读写适合少量数据传输,通过PCI接口发命令读写CPLD内的数据采集传输控制寄存器是通过从模式下单周期读写实现的;从模式突发读和从模式DMA读适合大量数据传输,将FIFO内数据搬移至主机内存是通过从模式下突发读和DMA读实现的。

另外,配合CPLD内的时序逻辑,PCI9054的配置芯片(93LC56)内必须进行合理的设置才能完整地实现系统功能,同时这也是驱动程序设计和应用程序设计的重要参考。本文利用PLX公司提供的专用在线烧写软件PLXMon完成了这一工作。其中所包含的空间映射信息见表1。

图4 从模式单周期读时序仿真图

图5 从模式单周期写时序仿真图

图6 从模式DMA读时序及FIFO控制逻辑仿真图

表1 PCI9054的本地端空间映射

3 WDM设备驱动程序设计

PC104Plus数据采集处理系统的一个关键问题是设备驱动程序的开发。设备驱动程序提供连接到PC104Plus板卡的软件接口文件扩展名为.SYS的动态链接库。Win2000是32位的多任务非实时操作系统,对整个系统底层的操作和用户与硬件打交道的权力被屏蔽,必须通过操作系统统一管理设备驱动程序和其他内核访问来实现应用软件对硬件的访问[6]。 在Win2000中,设备驱动程序必须根据Windows驱动程序模型(WDM)设计,它不是单独存在的,而是相关操作系统的一部分。因此定制与实际硬件相匹配的设备驱动程序是本系统能够正常工作的前提。选用Numega公司的DriverWorks来开发运行在Win2000下的WDM模式PCI设备驱动程序。该开发环境将WDM驱动程序编写所需的对内核及对硬件的访问封装成类,结合DriverWizard极大地简化了驱动程序开发的难度。本设计中主要涉及3个方面的问题:中断处理、普通读写和DMA传输[7]。

⑴中断处理。中断处理需要声明并在PnP启动例程中初始化KInterrupt和KDeferredCall类实例,还需要声明中断服务例程和延迟过程调用例程。当创建驱动程序框架时,若有中断资源,这些都是自动生成的。需要更改的地方是:在中断服务例程中判断是否是自己的设备产生的中断并设置相应的中断标志,在延迟过程调用例程中根据中断标志触发不同的事件,实现与应用程序的通信。

⑵普通读写。普通读写过程的关键是驱动程序如何获得应用程序的缓冲区。Win2000为驱动程序访问用户模式数据缓冲区提供了三种方法:Buffered方式、Direct方式和Neither方式。在此次开发中,我们使用的是Direct方式,I/O管理器把用户输入缓冲区数据复制到一个系统缓冲区,驱动程序可以用KIrp::IoctlBUffer访问这个缓冲区。输出缓冲区被类KMemory对象映射,驱动程序可以用KIrp::Mdl访问这个缓冲区。设计过程中要注意硬件对应的存储空间映射情况,处理好PCI配置空间大小和偏移量的问题。

⑶DMA传输。本文开发使用的是BlockDMA方式,本地端中断导致应用程序调用驱动程序开始DMA传输,应用程序无限等待事件的触发,在驱动程序中读完数据后触发事件。事件触发后,应用程序开始从驱动程序中读取DMA传输的结果。驱动设计的关键有:DMA适配器、内存空间等资源的添加和申请,DMA寄存器的设置和DMA启动。

本采集系统的驱动程序在PC104平台上的安装结果如图7所示。

图7 采集系统的设备驱动程序安装结果

4 性能验证

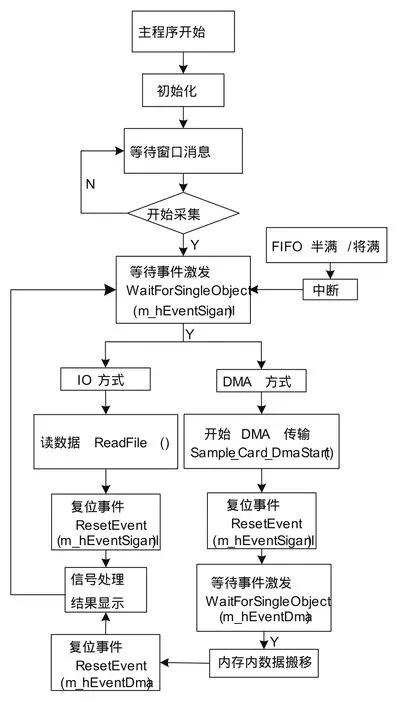

为评估本平台性能,本文构建了基于对话框的测试主程序,该程序运用多线程技术,用户界面线程通过消息泵机制处理用户输入及Windows的消息和事件,工作者线程用于完成采集数据的搬移和运算,其主流程见图8。由于该测试平台是一个基于PC的非实时的同步系统,不像可编程逻辑器件适合于对序列有严格定时的采样数据实时处理,只能通过中断来保持一定的同步。当采样率很高时,要对采样序列做逐样点运算,并保持严格同步是很困难的。因而,我们只能在中断的基本同步下进行高效率的数据成块处理,从而保证较好的信号统计特性。这就要求测试程序、驱动、可编程逻辑之间必须有一个好的时序匹配,主要是控制好中断的开关与采样数据读写的关系。如,采用IO方式读数据时,驱动程序在中断服务例程中要禁止中断/*m_MemoryRange0_ForBase0.outd(INTCSR,0x0);*/,m_hEventSiganl事件激发且测试程序完成了数据搬移和处理后则应打开PCI中断和LINT#中断/*g_pPCI9054AppDlg->writeBar0(0x68,0x900); */; 采用DMA方式读数据时,则应交替地打开LINT#中断和DMA完成中断以保证一帧数据的完整。DMA方式读数据时中断交替打开的具体过程为:m_hEventSiganl事件激发后允许PCI中断和DMA通道中断并启动DMA传输/*g_pPCI9054AppDlg->writeBar0(0x68,0x40100); */,m_hEventDma事 件激发且测试程序完成了数据搬移和处理后对应地打开中断PCI中断和LINT#中断,如此往复。

图8 主程序流程图

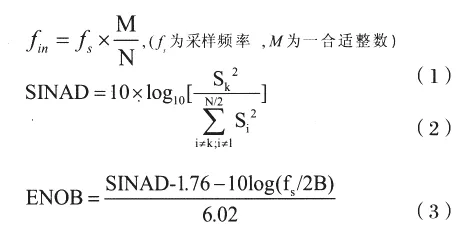

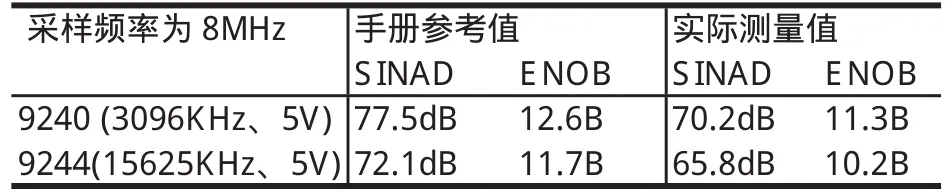

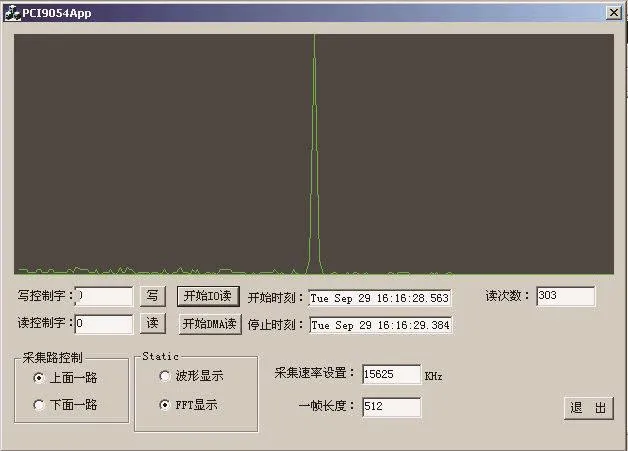

工程上,SINAD和ENOB是反映采集系统性能的主要指标,为了评价采集系统的性能,我们基于Agilent E4438c产生输入频率满足公式1(为了避免频谱泄漏)的满量程高纯度信号,依据FFT法按照公式2和公式3得出了本文所计论的两种采集卡的主要性能指标[8],指标计算结果与器件手册给出的参考值之间的比较见表2。实测波形见图9和图10。

表2 采集模块测试结果

图9 3906KHz、2048点FFT时频谱(9240采集模块)

图10 15625KHz、512点FFT时频谱(9244采集模块)

5 结束语

基于以上分析,并以此双信道多速率采集平台为基础,我们构建了30~3000MHz超短波频谱监测接收机,用于对超短波信号进行实时快速的全景搜索和分析测量,以掌握整个超短波信号的状态分布与动态变化情况。实测系统的等效扫频速率为700MHz/s,其宽带信号处理通道可以达到3.2kHz的频谱分辩率,窄带信号数据处理通道, 以25kHz带宽为例, 可以达到1.6kHz的频率分辨率,对于需要监测并进行高分辨率谱分析的信号,经过进一步抽取压缩窄带信号带宽并配合相关数字信号处理算法,可以达到最小0.9kHz的频率分辨率。实测系统同时还可在数据库的支持下进行实时的信号识别,性能良好。作为一种通用的数据采集系统,本系统也适用于其他需要多速率中频数据采集的应用。

[1]王帅,邓思颖,刘钊.变参差工作雷达数据采集系统[J].电子技术应用, 2007(10): 49-51.

[2]王伟.基于PCI总线的中频数字化接收机实现研究[D].哈尔滨:哈尔滨工业大学, 2006.

[3]康凯.基于总线的DSP高速数据采集处理系统[D].哈尔滨:哈尔滨工程大学, 2006.

[4]薛林.高速PCI数据采集卡的设计与实现[D].南京:南京理工大学, 2006.

[5]刘乐光,王升辉,李进.基于SOPC的1553B-PCI桥接通信模块设计[J].电子技术应用, 2009(7): 20-23.

[6]武安河,邰铭,于洪涛.WDM设备驱动程序开发[M].北京:电子工业出版社, 2003.

[7]陈妮,全英汇,邢孟道.基于FPGA的FLASH存储板的CPCI接口设计[J].火控雷达技术, 2008, 37(1):108-111.

[8]田坤,龚晓峰,任占民.ADC 的动态性能对软件无线电接收机性能的影响[J].现代电子技术, 2008(15):71-73.