一种SoC片上调试与可测性的整合设计

虞致国,魏敬和

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

在开发复杂SoC应用时,芯片的调试手段直接关系到开发的效率和进度,决定了应用的质量。没有调试硬件支持的调试已经不能胜任复杂SoC的应用,SoC必须提供高效、可靠、强大的调试支持[1~3]。另一方面,测试是集成电路生产流程中必不可少的一个环节,在设计时一般要采用可测性设计。

然而,可测性设计与调试结构设计一般是分别进行的。由于测试逻辑和调试逻辑都具有相当的逻辑量,约占系统逻辑的5%~25%[4]。因此,所需额外硬件资源都较大。目前,芯片的调试接口一般是基于JTAG标准而设计的。基于JTAG的可测性设计与片上调试设计相互独立又相互联系,二者可通过JTAG接口进行部分整合[5]。

本文基于已有的SoC提出了一种片上调试与可测性设计的一体化设计,有效整合了调试与可测性的接口。它既具有完整的片上调试能力,又能满足可测性要求,提供了SRAM内建自测试和边界扫描测试的能力。

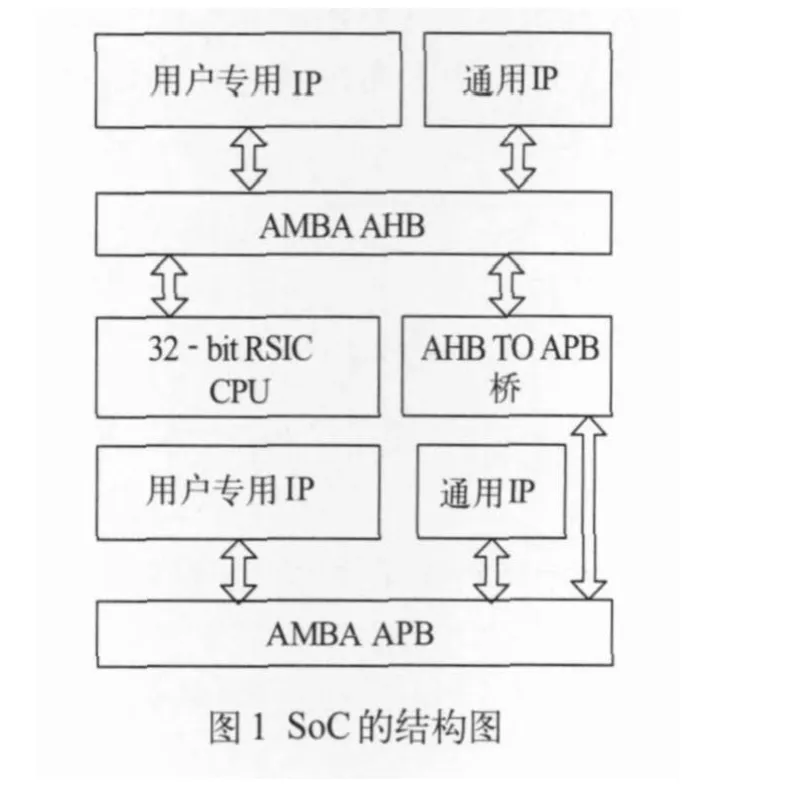

2 32-bit SoC的结构

该款SoC结构可以简单的用图1所示的结构表示,主要包括CPU核、SRAM、通用接口IP和用户专用IP。SoC片上总线采用AMBA总线(包括AHB总线和APB总线),CPU为32位硬核,具备从JTAG接口进行片上调试的能力,能够实现单步、断点、观察点等调试特征。

3 SoC片上调试与可测性的一体化设计

3.1 总体设计

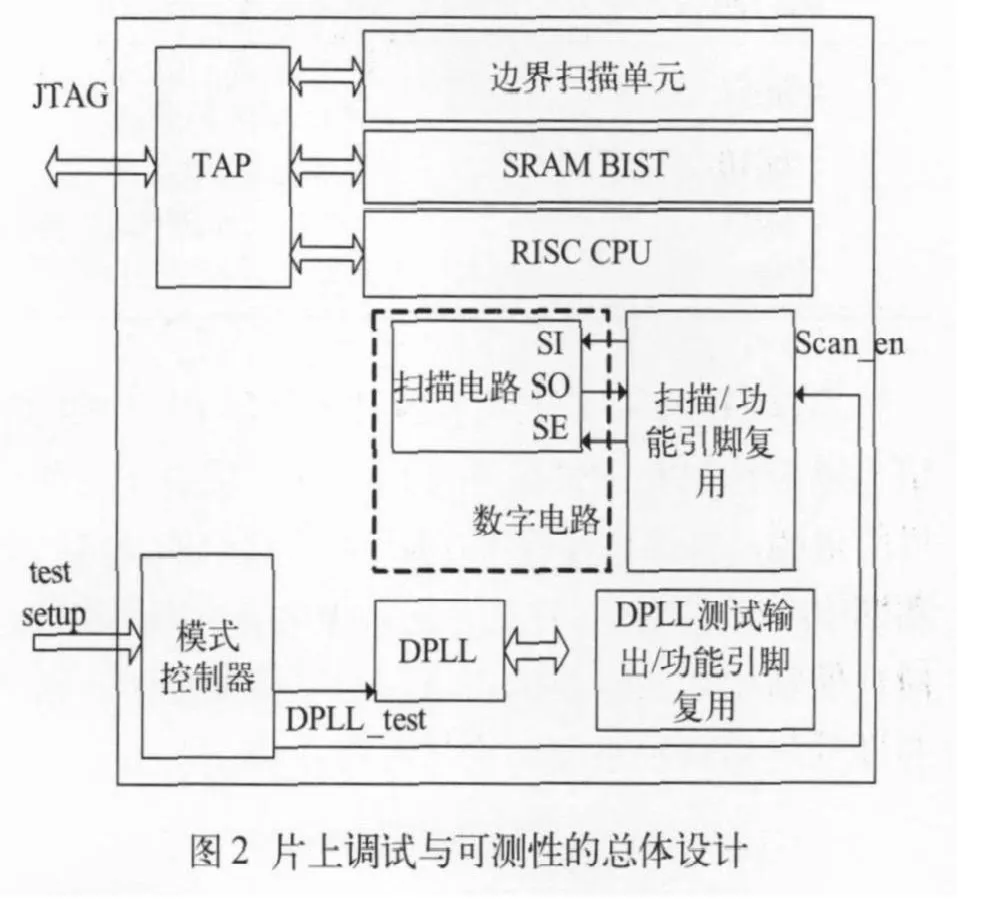

调试系统的设计目标是充分利用CPU核原有的调试结构,并通过JTAG进行有效的调试。可测性的设计目标是在利用较低的测试时间和较小的测试面积实现较高的测试覆盖率和故障覆盖率。因此,总体的设计思路是尽可能地利用JTAG复用相关调试与测试入口,并针对不同的模块利用不同的测试策略。针对测试来说,通过JTAG接口可以集成边界扫描测试、存储器内建自测试等。测试策略实现了在测试覆盖率和测试代价之间的一个有效折衷。测试代价包括芯片面积、芯片引脚数、功耗和芯片工作频率、测试时间长度等。总体的设计结构如图2所示。主要的设计思路如下:

(1)构建了一个芯片级别的调试与测试模式控制器;

(2)基于JTAG集成了边界扫描测试(BSD)、存储器内建自测试(SRAM BIST)和CPU片上调试等接口;

(3)对数字IP和用户自定义逻辑采用扫描测试;

(4)复用第三方提供的CPU测试向量;

(5)对于嵌入式SRAM实现内建自测试;

(6)对于DPLL实现功能测试。

3.2 调试与测试模式控制器

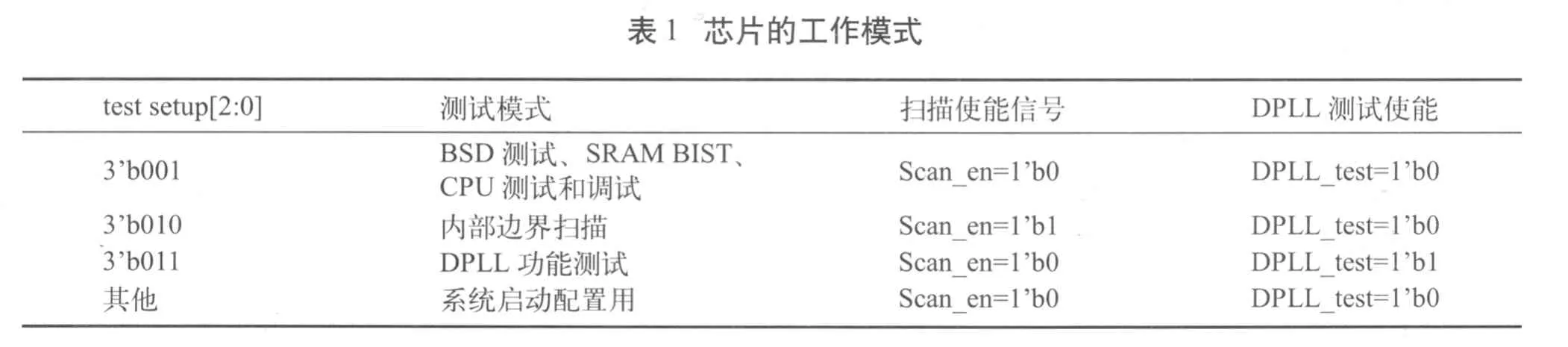

除了正常的工作模式外,SoC还有完备的调试与测试模式。芯片的模式控制由引脚testsetup[2:0]所控制。测试模式的描述见表1所示。

芯片内部有多个时钟域,主要包括TCK、内部系统时钟、扫描时钟。调试模式使用的是边界扫描时钟TCK;正常工作模式使用的是经锁相环倍频的时钟,其他扫描模式使用的是系统外部时钟。

在扫描链的插入过程中,为了避免因可测性设计带来引脚的大量增加,采用了测试引脚和功能引脚复用的结构。为了能有效在工作模式与测试模式间进行切换,增加了扫描使能信号scan_en。当处于测试模式时,scan_en有效,引脚处于扫描模式。为了在对DPLL功能测试时能输出相关状态,增加了DPLL测试输出使能信号DPLL_test。

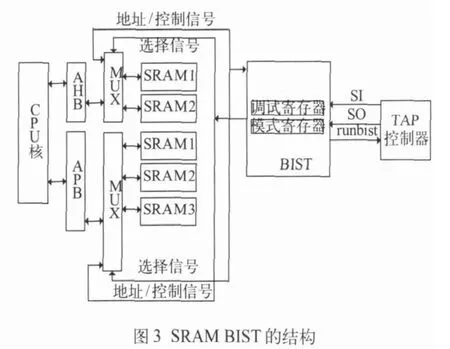

3.3 SRAM BIST

对于高密度嵌入式SRAM来说,BIST是一种有效的测试方法,它能够全速实现高覆盖率的测试。SRAM BIST电路是由EDA工具自动生成的。

在设计的某SoC设计中,有多片SRAM,分别在ABH总线和APB总线上。SoC中采用的SRAM BIST的结构如图3所示。CPU核和BIST电路通过MUX开关与SRAM相连。在正常工作模式下,CPU核可以通过AHB或APB来访问SRAM。在测试模式下,SRAM的选择信号、地址、数据及控制信号由SRAM BIST电路根据MBIST算法产生。MBIST算法包括March LR、March C-、MATS++ and Retention等,算法由模式寄存器的值来选择。

通过JTAG的TAP控制器对SRAM BIST的测试信号进行控制和测试结果进行查询,摆脱了对测试机的依赖。自测试过程中,BIST将获得的测试结果和期望的结果将进行比较,比较结果pass/fail将被返回存储到模式寄存器中。当一个错误发生时,错误的详细信息将被跟踪到调试寄存器中。

3.4 DPLL功能测试

DPLL是一个全定制宏模块。DPLL功能测试结构如图4所示。当外部信号DPLL_test置于1时,SoC进入DPLL功能测试模式。功能测试模式时,测试引脚输入/输出来自于外部引脚。

4 实现与结果

该SoC采用SMIC 0.18μm 1P6M逻辑电路工艺。芯片总共有管脚391个,包括PAD在内,芯片的面积为7.76mm×7.76mm,测试面积占芯片面积的6.89%。芯片的设计结果如下:

(1)总共有10条内部扫描链,每条扫描链的长度约为3000;

(2)数字IP和用户自定义逻辑的覆盖率是97.2%;

(3)SRAM的测试覆盖率为100%;

(4)CPU核和DPLL采用功能测试的方法;

(5)全芯片的测试面积占芯片面积的6.89%。

5 结论

片上调试与可测性设计是嵌入式系统和SoC设计中的重要环节。本文提出了一种可测性设计与调试系统一体化的结构设计策略,其重点在于将现有的测试方法与系统的调试结构整合到一个结构中。被整合的测试方法包括扫描链插入、SRAM BIST、功能测试等,同时有效地降低了测试逻辑规模。本文提出的结构对其他SoC设计具有一定的参考价值。

[1]赵岩,张果,张春,等.一种扩展的片上实时调试系统设计[J].计算机工程,2006,32(8):283-285.

[2]金辉,华斯亮,张铁军,等.基于JTAG标准的处理器片上调试的分析与实现[J].微电子学与计算机,2007,24(6):116-121.

[3]成杏梅,刘鹏,钟耿.嵌入式MPSoC的调试功能实现[J].计算机辅助设计与图形学学报,2008,20(4):438-444.

[4]李少青,邓勤学.故障测试结构与调试结构的一体化设计[J].计算机工程与科学,2006,28(8):99-100.

[5]严明.嵌入式微处理器可测性设计与片上调试技术的研究与实现[D].硕士论文,国防科学技术大学,2005,11.

[6]刘洋、吴王华,周晓方.一种基于JTAG的软硬件协同SoC调试接口[J].微电子学与计算机,2007,24(11):34-37.

[7]IEEE Standard Test Access Port and Boundary Scan Architecture. IEEE Std 1149.1-2001(Revision of IEEEStd 1149.1-1990).