基于SCCB通信的FPGA视频采集模块

褚红娟 隋国荣

(南通醋酸纤维有限公司1,江苏 南通 226008;上海理工大学光电信息与计算机工程学院2,上海 200093)

0 引言

传统图像获取技术以CCD传感器为主,但随着CMOS技术的成熟以及各方面性能的提高,尤其鉴于CMOS图像传感器在功耗、成本、抗辐射性能等方面的优势,使其日益受到人们的重视,它正逐步取代CCD图像传感器[1-2]。

视频监控系统的后台数据处理系统常采用ARM或DSP芯片进行并行算法运算。本模块利用FPGA的强大并行处理能力,在完成CMOS传感器并行控制的同时,实现后期的数据和图像处理,为系统提供更好的抗干扰、容错和低成本等性能[3-4]。

1 设计总体要求

目前,视频监控系统应用对视频信号的获取和处理都提出了更高的要求。针对企业的实际生产需求,希望设计一个微小的视频采集模块,使其在一个狭小的空间对现场的信息进行实时获取并送至后台进行处理,最后将处理结果的信息流通过现有网络传送到服务器,从而减小系统的整体负荷。因此,一个微型、低功耗且低成本的实时视频采集模块将是整个视频监控系统设计的首要环节。在模块的设计过程中,需要考虑图像传感器的各项性能指标(如体积、成本和功耗)、图像传感器的控制与通信方式、模块的整体功耗与实时性,以及数据传输的方式等问题。

2 模块设计

针对设计要求,确定模块整体设计方案,并根据整体设计方案完成了模块的软硬件设计和调试,整体模块框图如图1所示。

图1 整体模块框图Fig.1 Block diagram of the overall module

2.1 硬件设计

从信息获取的角度分析,CCD摄像器件具有光照灵敏度高、噪声低、像元尺寸小等优点。但随着CMOS技术的成熟,CMOS图像传感器在信噪比和动态范围等方面的性能已经与CCD图像传感器接近。如美国豪威科技等公司制造的CMOS图像传感器,它们在系统功耗、体积、重量、成本、抗辐射性能以及可靠性等方面都具有超越CCD传感器的优势。因此,我们选取了豪威科技生产的微型CMOS摄像头OV7620作为图像获取传感器。OV7620具有CMOS彩色/黑白图像传感器功能,支持连续和隔行两种扫描模式,并具有VGA与QVGA两种图像格式,帧速率可达30帧/s,数据格式包括YUV、YCrCb、RGB三种,能够满足一般视频信息获取系统的要求。OV7620包含有:664×492的图像矩阵、模拟信号处理器、双10 bit A/D转换、模拟视频合成接口、数字数据格式化接口和视频输出端口、SCCB端口及其寄存器、数字控制模块(包括时序发生器)、自动曝光模块和白平衡控制等模块[5]。

在传感器的驱动和控制方面,我们首先对OV7620进行窗口大小的设置,芯片允许在4×4到664×492之间调节,且能在664×492边界内放置到任何地方。在实际设计过程中,我们通过HREF值的设定最终确定640×480的输出窗口。另外,OV7620支持软硬件复位功能,当Reset为高时,整个芯片(包括所有寄存器)都复位。硬件睡眠模式是指当PWDN为高时,芯片时钟停止,除了SCCB寄存器以外的所有内部电路都将复位。寄存器12的bit7起到软件复位功能,功能同硬件复位,硬件复位的最短时间为1 ms。同时,OV7620支持软硬件省电模式。当PWDN为高时,整个芯片处于睡眠模式,没有任何电流消耗。软件睡眠模式是指所有的电流为零,除了晶振电路。在睡眠模式下,SCCB寄存器的值保持不变。芯片的这些详细、灵活的控制模式使我们可以很好地完成对CMOS的驱动和控制,从而实现视频信号的获取。

从芯片的驱动和控制角度考虑,我们抛开了传统的高级别单片机、DSP或者ARM的控制方法,为满足后台对数据传送的需求以及后期对整体图像处理模块的集成,我们采用了 Altera公司的 FPGA芯片对OV7620芯片进行实时驱动和控制,并通过该芯片进行数据输出。FPGA是基于查找表LUT(look-up-table)结构的PLD(可编程逻辑器件)芯片。查找表本质上就是一个RAM。目前,FPGA中大多使用四输入的LUT,所以每一个LUT可以看成是一个有四位地址线的16×1的RAM。当用户通过原理图或硬件描述语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能结果,并把结果事先写入RAM。这样,每输入一个信号进行逻辑计算就等于输入一个地址进行查表,找出与地址对应的内容,然后输出即可[6]。

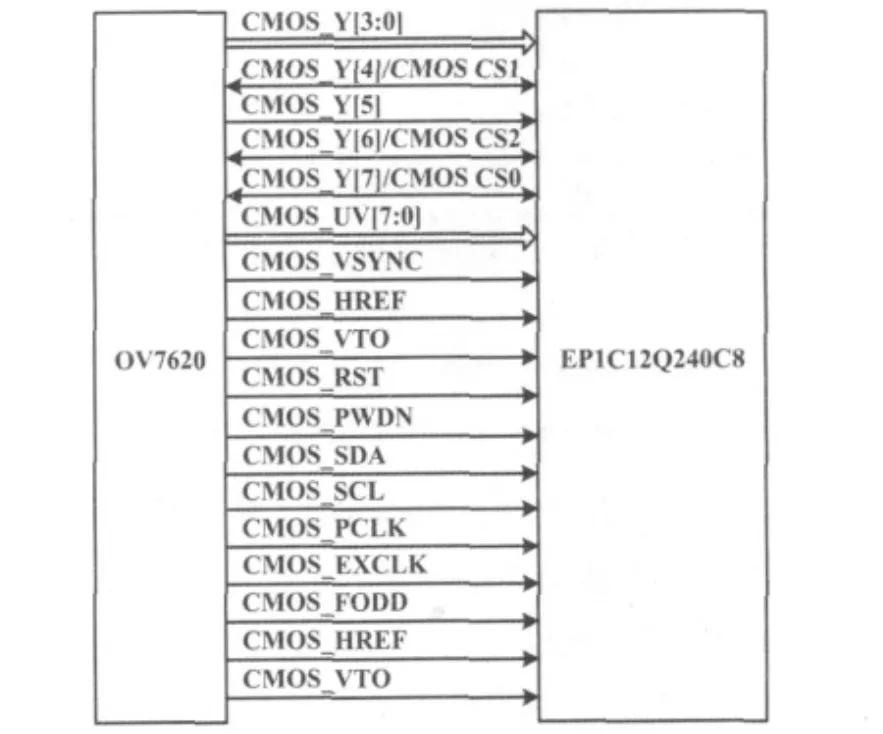

本文选用了Altera公司的Cyclone系列器件,它是性价比较高的一个产品系列,具有多达20060个逻辑单元和288 kB的RAM,能够集成各种所需的复杂逻辑功能。设计过程中建立了以EP1C12Q240C8为核心芯片的硬件开发平台,其核心板包括一片EP1C12Q240C8、16×4 MB的SDRAM以及64 MB的Flash。利用FPGA实现OV7620控制的硬件原理图如图2所示。

图2 硬件原理图Fig.2 Principle of the hardware

2.2 软件设计

2.2.1 SCCB 通信协议

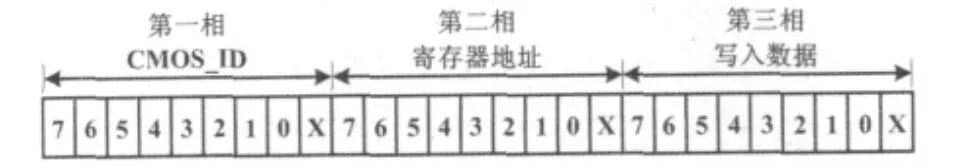

OV7620内部可编程功能寄存器的设置分为上电模式和SCCB编程模式。本文采用的是SCCB编程模式。SCCB通信是一种简化的I2C通信,它只要求两条总线线路,其中一条为串行数据线(SCCB_SDA),另一条为串行时钟线(SCCB_SCL)。每个连接到总线的从器件都有一个唯一的地址,主器件通过这个地址对它进行读写,实现通信[7-9]。FPGA通过 SCCB通信设定OV7620的功能寄存器数值,OV7620功能寄存器的地址为0x00~0x7C。通过设置相应的寄存器,可以使OV7620工作于不同的模式,如数据输出方式、黑白和彩色模式以及扫描方式等功能控制。SCCB通信协议数据格式如图3所示。

图3 SCCB通信协议数据格式Fig.3 The data format of SCCB communication protocol

图3中:第一相为CMOS的ID号;第二相为寄存器的地址;第三相为具体写入数据;X位为数据无关位。

写寄存器的过程为简单的三相写数据的方式,即在写寄存器的过程中先发送OV7620的ID地址(ID Address),然后发送写数据的目地寄存器地址(Sub_address),最后发送要写入的数据(Write Data)。如果给连续的寄存器写数据,写完一个寄存器后,OV7620会自动将寄存器地址加1,程序可继续向下写,而不需要再次输入ID地址,因此,后面数据只需写入两相数据即可。利用SCCB通信协议进行数据传输时的软件仿真时序图如图4所示。

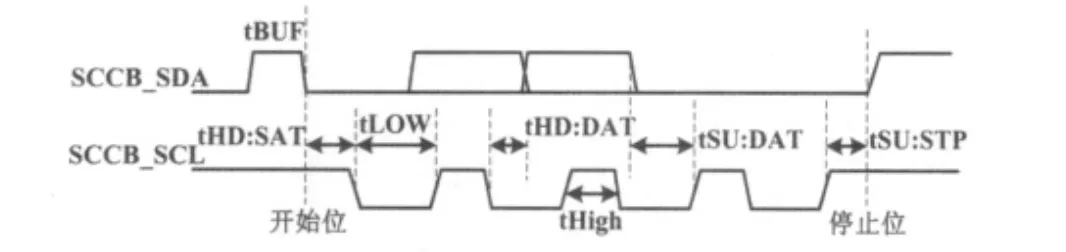

图4 软件仿真时序图Fig.4 Timing chart of software emulation

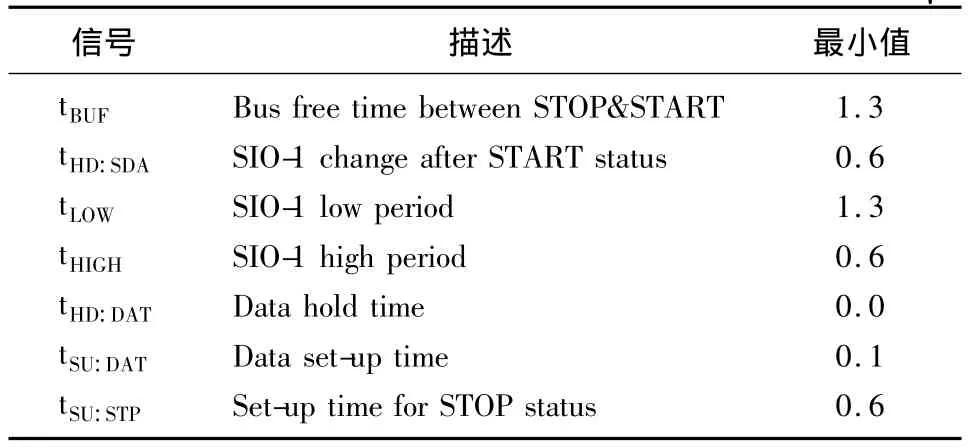

SCCB控制总线功能的实现完全是依靠SCCB_SCL、SCCB_SDA线上电平的状态以及两者之间的相互配合实现的。当SCCB_SCL为低电平时,SCCB_SDA出现一个下降沿,此时传输启动。在启动条件满足后,SCCB_SDA为稳定数据状态,SCCB_SCL产生一个正脉冲,将传送一位数据;当SCCB_SCL为高电平时,SCCB_SDA出现一个上升沿,传输停止。SCCB通信协议参数如表1所示。

表1 SCCB通信协议参数Tab.1 Parameters of SCCB communication protocol μs

2.2.2 视频信息获取与处理

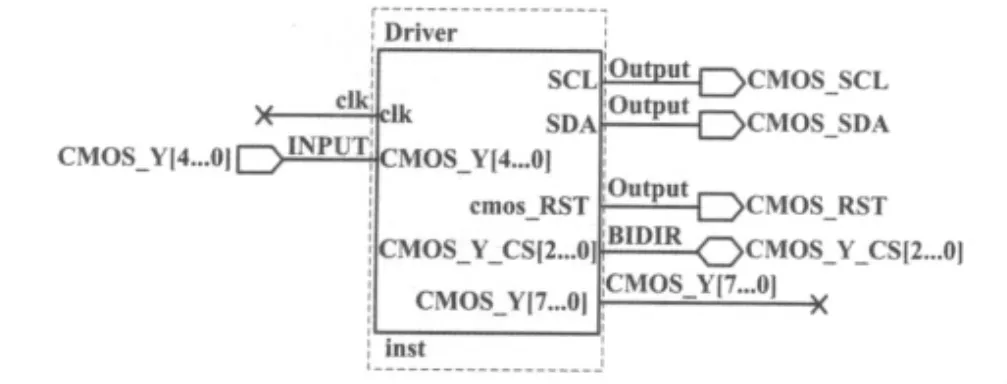

使用Verilog HDL编程语言在Quartus中进行编程,可生成视频信息获取模块图[10-11]。该模块如图5所示,其主要作用是通过FPGA设置OV7620的寄存器值等参数以驱动OV7620,并采集视频信息数据。

图5 系统模块图Fig.5 The module diagram of system

图6为视频信息获取系统流程图。OV7620上电后,先对其进行复位操作,使整个芯片处于复位状态,即置COMS_RST为高电平,此时所有寄存器也被复位。在此过程中,通过 CMOS_Y_CS[2…0]设置OV7620在SCCB通信中的地址。

图6 系统流程图Fig.6 Flowchart of the system

复位结束后,FPGA通过 SCCB通信协议设置OV7620的地址slaveID、SCCB寄存器的地址subaddr和需要发送的寄存器数值dataN。在SCCB通信过程中,由于每次发送的字节数较多,所以把要发送的数据先存储在寄存器data内,然后再从该寄存器取数值。假设需要设置n个寄存器,则数据宽度是WIDTH=(n+2)×(8位数据+1位无关位)。对于不同的需求,可以重新进行寄存器值和数据宽度的设定,而且只需要修改程序最开始的参数设置,这样大大提高了系统的灵活性。

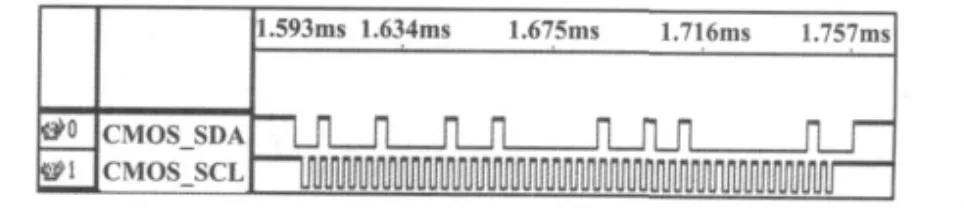

当以上数据传输成功以后,即OV7620的寄存器值被成功设置后,OV7620被驱动,并按照设置情况进行工作,获取视频信息。系统时序仿真波形如图7所示。

图7 时序仿真波形图Fig.7 Timming emulation curves

SCCB通信的传输开始位和传输停止位等时序均与图4相同,说明本系统满足在SCCB通信时的时序要求。系统硬件和软件设计完成之后,在Quartus环境下,将程序下载至FPGA中。下载完成后,通过示波器测试输出,验证了系统的正确性。

3 系统测试结果

系统通过OV7620的控制,实现了在不同模式下的工作,满足用户的需求。通过具有硬件逻辑分析仪功能的数字式示波器进行关键信号的采样,并利用GPIB通信接口将示波器管脚的信号传输至计算机。

4 结束语

本文设计了一个基于SCCB通信的FPGA视频采集系统,通过VHDL编程解决了SCCB通信的问题,保证了系统的准确性与灵活性。实验结果显示OV7620的输出很好地保持了视频信号原始特性,增加了后续图像处理的可操作性和灵活性。系统实现简单,且可以自由扩展到多个视频信号同时输入并行处理的情况。系统优化设计提高了系统效率,降低了功耗,适合应用在特殊场合和工业视频监控等领域,能提供稳定可靠的信号获取源,后期将考虑在图像高清处理方面进行更为深入的研究。

[1]范红,陈桂林.CMOSAPS图像传感器的相质分析[J].光电工程,2006,33(5).

[2]尤政.CMOS图像传感器在空间技术中的应用[J].光学技术,2002,28(1):31 -35.

[3]刘杰,牛燕雄.基于FPGA的视频信号发生器设计与应用研究[J].仪器仪表学报,2001,29(3).

[4]刘杰,牛燕雄.基于FPGA设计的图像增强预处理器[J].光电工程,2001,28(3).

[5]芦薇,徐磊.基于FPGA的OV7620视频信息获取系统[J].光学与光电技术,2010(3):49-53.

[6]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2007.

[7]苑玮琦,汤永华.OmniVision图像传感器的SCCB总线协议在DSP 中的实现[J].仪器仪表学报,2006,27(S1).

[8]陈国柱.基于FPGA的图像采集与存储系统设计[J].机械工程与自动化,2007(143).

[9]付斌,张晓雷.CMOS图像传感器时序分析研究[J].传感器与微系统,2007,26(12).

[10]何斌.FPGA的 EDA 设计方法[J].光学精密工程,1995(6).

[11]蔡怀宇.基于EPP接口的CMOS图像采集系统设计[J].仪器仪表学报,2003,24(S1).