USB多路数据采集器

狄旭明,吴建平

(成都理工大学核技术与自动化工程学院,四川 成都 610059)

1 引 言

数据采集系统是将传感器采集的模拟电压信号转换成计算机能识别的数字信号,通过各种接口送入计算机,使工作人员能对被监测的物理量进行分析。一个数据采样系统性能的参数是它的采样精度与速度,随着电子技术的发展,对这两项性能提出了越来越高的要求。传统设计方法是采用单一MCU控制采样。这种结构方式的缺点是MCU的片上资源有限,难以实现多路信号的同时采样;另一方面在进行高速采样的时候,MCU将进行频繁的中断,加重了MCU运行负荷,设计者只有选择成本更高的高级MCU。该文采用FPGA+ARM的设计方案,让FPGA完成对A/D的控制功能以及数据的缓存功能,实现了多路信号的采集,最大限度地提高了系统的信号采集精度和处理能力。

2 系统硬件设计

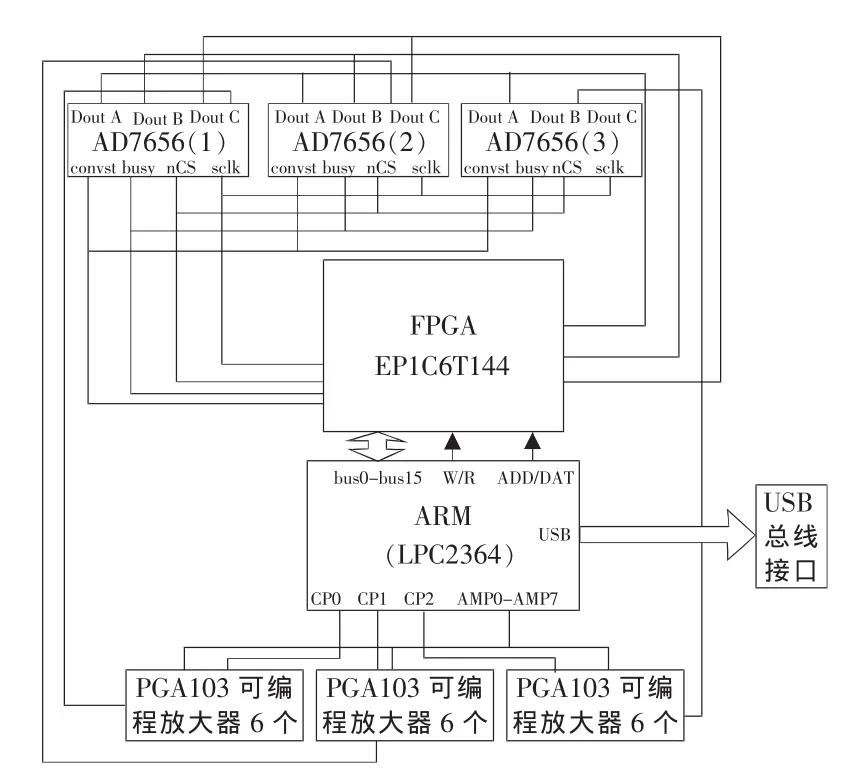

系统硬件电路设计原理如图1所示,共分为3个主要部分:A/D转换电路、FPGA接口电路和基于ARM的核心控制电路。

2.1 系统的性能指标

同时对16路信号进行采样;

被采样信号电压变化范围为-10~+10V;

采样精度为16位;

采样速度≥200kS/s。

2.2 硬件电路设计

该系统实现对16路电压信号采样,每一路输入信号经过PGA103可编程运放可实现1倍,10倍,100倍的信号放大送入A/D转换器,放大倍数由ARM直接控制。系统中的采集单元共用了3块AD7656,每块A/D转换器实现6路信号的并行采样。由FPGA实现采样过程的控制及采样逻辑时序的产生,FPGA采集得到的数据通过与ARM的自定义总线送入ARM,并最终由ARM控制的USB接口送入上位机,显示出波形结果。

图1 总体硬件设计结构

2.3 A/D转换电路

根据系统的性能要求,A/D转换器选用美国ADI公司的基于iCOMS工艺6通道16位双极性逐次逼近(SAR)型ADC器件——AD7656。AD7656可以同时对6路模拟输入进行同时采样,最高可达250kS/s的数据吞吐能力,能够满足高分辨率、多通道、高转换速率和低功耗的要求。

要实现16路的信号采集一共要用3片AD7656,系统采用串行数据输出模式。Dout A,Dout B,Dout C是AD7656的数据串行输出口,每个一次转换传出32位数据,代表两路通道采样结果。SER/nPAP接高电平表示采用串行输出方式。SCLK是串行输出时钟,由FPGA提供。nCS,Busy为控制引脚,接到FPGA上,由硬件时序控制。

2.4 FPGA控制电路设计

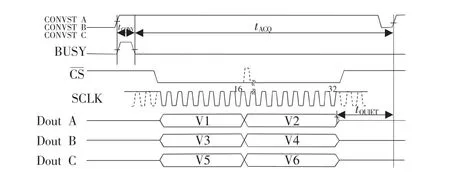

系统选用了Altera公司的 PGA芯片,型号为Cyclone系列的EP1CT6144,工作电压3.3V,内核电压1.5 V。芯片设计采用0.13 μm工艺技术全铜SRAM工艺,其密度为5980个逻辑单元和20个128×36位RAM块(M4K模块),片内总的RAM空间达到92160位,内嵌2个锁相环电路,1个于连接SDRAM特定双数据率接口,工作频率高达200MHz。采用了专用配置芯片EPCS1对FPGA进行串行配置。FPGA对A/D信号转换过程进行控制的时序如图2所示。

由于是16通道同时采样,因此在设计过程中将3个转换控制信号A、B、C接到一起。当CONVST转换信号上升沿时,采集开始,Busy信号线返回高电平,表明信号正在转换中。当系统检测到Busy信号线产生下降沿,表示信号转换结束,系统可以开始读取数据,这时将nCS信号置低,6路通道的转换数据将通过3个串行输出口Dout A,Dout B,Dout C伴随串行时钟SCLK输出到FPGA中暂存起来。

图2 AD7656采样数据串行输出时序

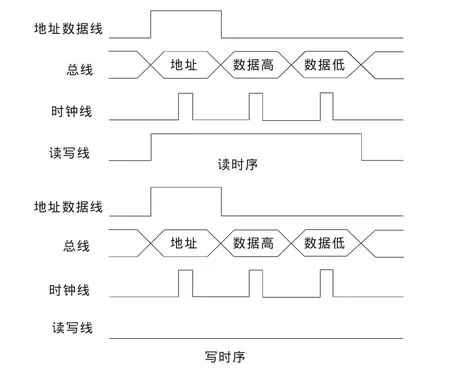

FPGA还要实现与ARM的数据通信,通讯方式是采用的自定义16位总线模式。定义的信号线有:16位数据地址总线,1根地址/数据选择线,1根读写信号线,1根同步时钟线,1根I/O中断标准线。具体时序如图3所示。

图3 自定义FPGA与ARM总线时序

2.5 基于ARM的核心控制部分

系统采用NXP的LPC2364作为核心控制器。LPC2364微控制器基于16位/32位ARM7TDMI-S的CPU,并带有512KB嵌入的高速Flash存储器。它集成了10/100以太网媒体访问控制器、带4KB终端RAM的USB全速设备、4个UART、2路CAN通道、1个SPI接口、2个同步串行端口(SSP)、3个I2C接口以及1个I2S接口等。LPC2364主要可实现的功能为:通过USB口与PC机的数据通信;对FPGA的读写控制;对输入模拟信号放大倍数的设定。

3 系统软件设计

3.1 FPGA内部逻辑设计

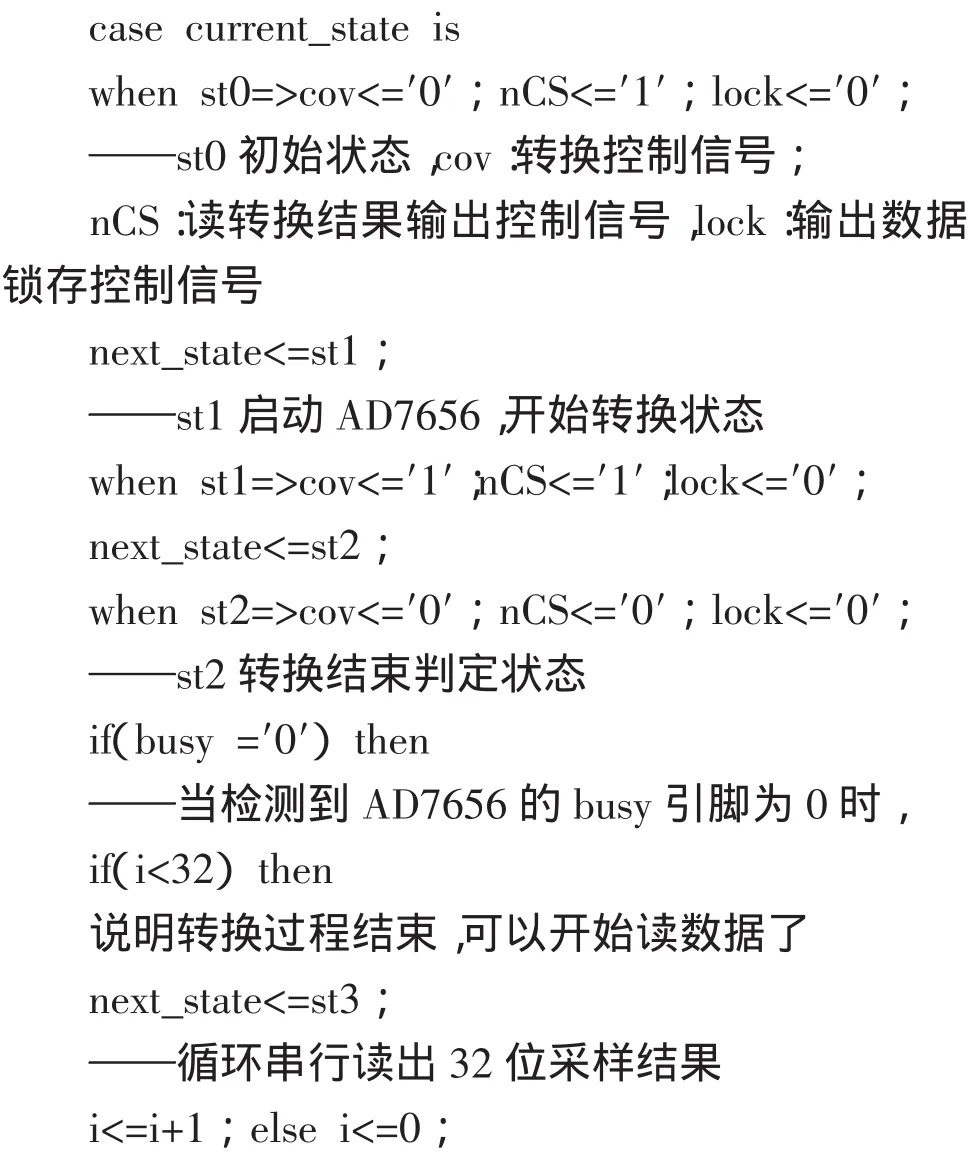

对FPGA的逻辑设计分为与LPC2364的接口模块、时钟分频模块、内部寄存器模块、采样控制模块、串并转换模块和FIFO数据缓冲模块,共6个部分。工作过程为:LPC2364向FPGA写入控制命令,设定采集过程的主要参数(采样频率,采样深度等),FPGA通过逻辑时序电路启动A/D转换,收集到转换数据后,通过串并转换模块转换为16位并行数据,存入FIFO中,等待LPC2364取出数据。采样控制模块的状态机部分程序如下:

3.2 ARM驱动程序设计

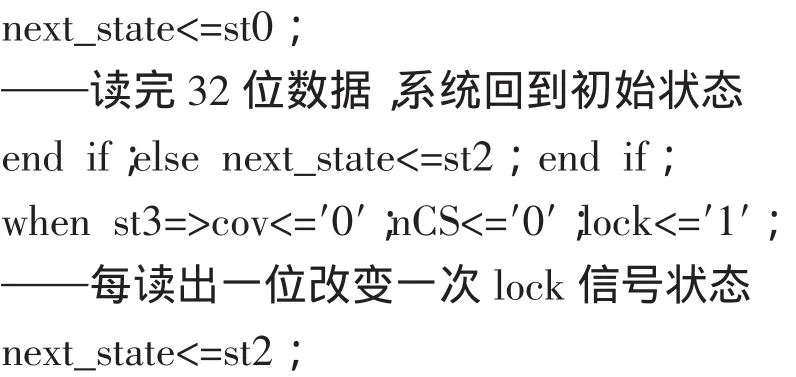

为了提高采集速度和实时性,ARM主程序在uCOS II实时操作系统下运行。根据系统功能共设置5个任务:起始任务(TaskStart),读系统寄存器任务(TaskRead),设置系统寄存器任务(TaskSet),数据采样任务(TaskSam),放大倍数设置任务(TaskAmp)。

运行过程为在起始任务中初始化USB接口,等待上位机发送控制命令数组,根据数组发送相应信号量,其他四个任务接收到信号量进入运行态,执行对应操作。具体的程序流程如图4所示。

3.3 上位测试软件

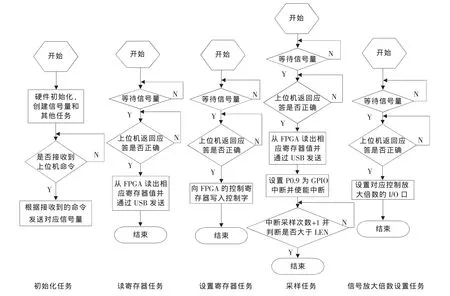

硬件采集到的信号通过USB总线传到上位机,由上位机运行的软件处理显示。由于时间关系现只完成一个简单的测试程序,由PC机发送采集起始命令11,返回采集到的外加4V恒压信号值,如图5所示。

图4 ARM控制程序流程

图5 信号采集测试程序

4 结束语

基于USB的多路数据采集系统利用ARM+FPGA的设计模式对AD7656模/数转换器进行控制,实现了同时完成对16路-10~+10 V的模拟信号进行采集转换。经试验测试,设计完全满足系统要求,并且提高了数字信号处理的速度和精度。此外该设计的外围电路配置简单、便于携带、成本低、使用灵活,有较好的应用前景,应用领域也会越来越广泛。

[1] 刘书明,刘 斌.高性能模数与数模转换器件[M].西安:西安电子科技大学出版社,2000.

[2] 陈茹梅,郭建硕.AD7656型模/数转换器在信号采集系统中的应用[J].国外电子元器件,2006(2):67-71.

[3] 常铁原,王 欣,卢冬冬.AD7656与LPC2210的并行采集接口设计 [J].单片机与嵌入式系统应用,2008(12):10-11.

[4] 朱维钧,周有庆,王忧忧.AD7656及其在电力系统测控中的应用[J].电工材料,2007(2):47-50.

[5] 党瑞荣,汤小松,王成莉.基于AD7656的高性能输电线监测系统设计[J].计量与测试技术,2008(9):8-10.

[6] 陈乃阔,李 萌.基于CAN总线的条码扫描器管理系统[J].中国测试技术,2008,34(6):73-76.

[7] 刘小林,范育兵.基于FPGA的多通道数据采集系统设计[J].电子技术与应用,2009.