基于FPGA的QAM信号发生器设计

郝小江,缪志农,黄 昆

(攀枝花学院电气信息工程学院,四川 攀枝花 617000)

1 引 言

为了满足现代通信系统对传输速率和带宽提出的新要求,人们不断地推出一些新的数字调制解调技术。正交幅度调制解调(Quadrature Amplitude Modulation and Demodulation)就是一种高效的数字调制解调方式。与其他调制技术相比,这种调制解调技术能充分利用带宽,具有很高的频率利用率,且抗噪声能力强。因而在中、大容量数字微波通信系统、有线电视网络高速数据传输、卫星通信等领域得到广泛应用。该文根据直接数字频率合成技术(DDS),利用Altera公司的FPGA开发工具DSP Builder对正交幅度调制信号进行建设计,并进行功能仿真和时序仿真,设计表明该系统设计的正确性和实用性。

FPGA(Field Programmable Gate Array)是目前广泛采用的一种可编程器件,随着微电子技术的发展,现场可编程门阵列(FPGA)得到了飞速发展。FPGA的时钟延迟可达到纳秒级,结合其并行工作方式,在超高速、实时测控方面有非常广阔的应用前景,具有工作速度快、集成度高和现场可编程的优点。它的应用不仅使得数字电路系统的设计非常方便,并且还大大缩短了系统研制的周期,缩小了数字电路系统的体积和所用芯片的品种。而且它的时钟频率已可达到几百兆赫兹,加上它的灵活性和高可靠性,几乎可将整个设计系统下载于同一芯片中,实现片上系统(SOC),非常适合用于实现调制信号发生器的数字电路。

2 DDS的基本原理

直接数字频率合成(Direct Digital Synthesizer-DDS)是一种新型的频率合成技术,基本原理是用全数字技术从相位概念直接合成波形。具有较高的频率分辨率,可以实现快速的频率切换,并且在频率改变时能够保持相位的连续,很容易实现频率、相位及幅度的数控调制。DDS的基本结构如图1所示,主要由相位累加器、相位调制器、正弦ROM查找表和D/A构成,相位累加器是整个DDS核心,完成相位累加运算。图1中的相位累加器、相位调制器、正弦ROM查找表是DDS结构中的数字部分。

图1 基本DDS结构

3 正交幅度调制建模设计

正交幅度调制信号发生器电路框图如图2所示,图 2 中 a(t)和 b(t)为两路相互独立的待传送的调制信号(通常为基带信号),载频信号源由基于DDS的正交信号发生器产生,它输出两路正交的正弦信号(sinω0t、cosω0t),经过两个乘法器可以获得互为正交的平衡调幅波,其中一路为同相信号I(t),另一路为正交信号Q(t),I(t)、Q(t)表达式为:

两路信号经过加法器后产生互为正交的调幅信号,表达式为:

X(t)是I(t)、Q(t)两信号相加而得,所以X(t)的频带宽度等于 I(t)、Q(t)信号中带宽最宽者(或等于 a(t)或 b(t)最宽带宽的 2倍),如此可压缩已调信号的带宽,增加信道容量。

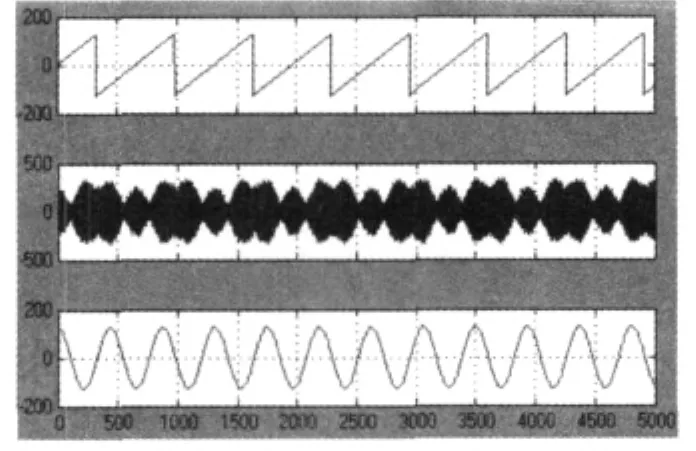

图2 正交幅度调制原理图

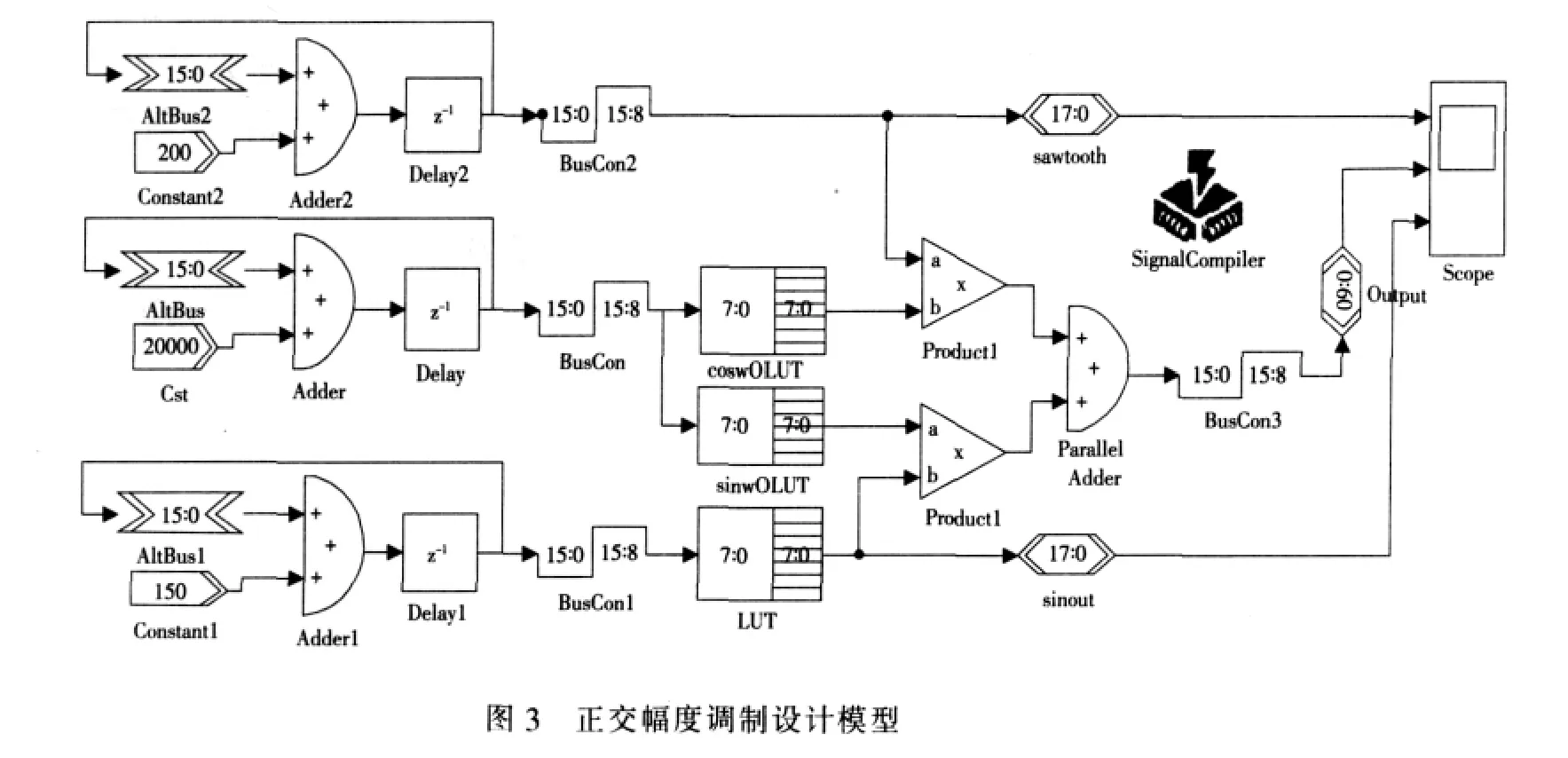

根据正交幅度调制原理,利用FPGA开发工具DSP Builder对正交幅度调制信号发生器进行建模设计,如图3所示。图中用高频余弦信号(cosω0t)对锯齿波a(t)和高频正信号sinω0t对低频正弦信号b(t)进行调制,获得正交的平衡调幅波,通过相加后就可获得正度幅度调制信号。其算法仿真结果如图4所示。

4 仿真分析与硬件实现

建模算法仿真完成后,需要对所设计的模型进行功能仿真和时序仿真,以验证设计符合硬件特性。打开模型中的SignalComplier模块,设置好参数,把模型转换为VHDL代码、综合及QuartusII适配。经过分析转换后的VHDL程序并将其转换为ATOM netlist,最后编译ATOM netlist。生成VHDL描述的是RTL级的,是针对具体的硬件结构的,需要对生成的VHDL代码进行功能仿真。采用ModelSim基本单内核的Verilog/VHDL混合仿真器,得到如图5所示的模拟信号仿真图和功能仿真图。其模拟信号仿真结果与在MATLAB中算法仿真结果完全一致。

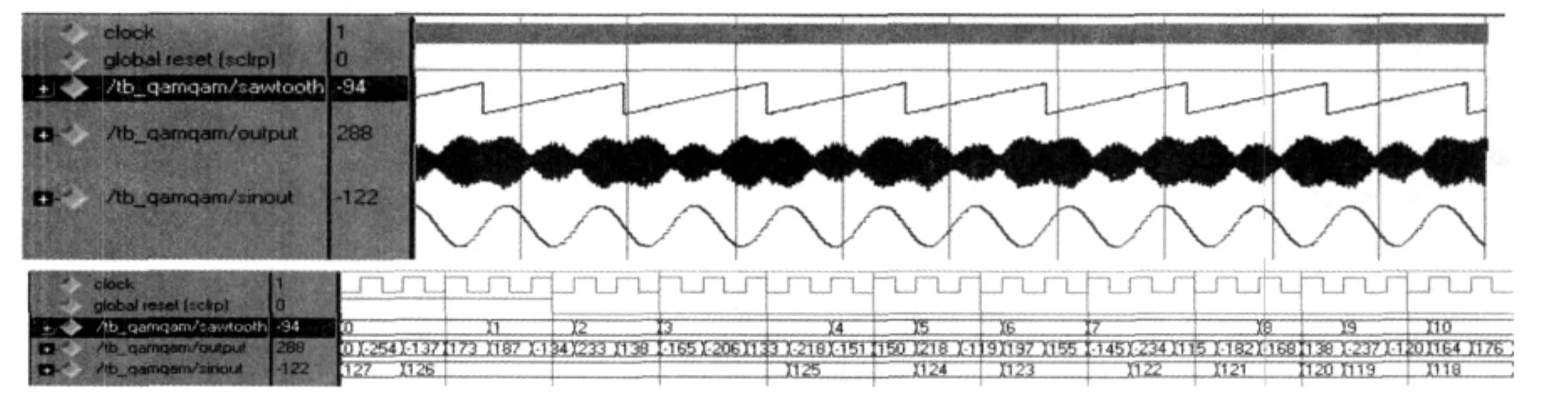

ModelSim完成的RTL级仿真只是功能仿真,其仿真结果并不能精确反映电路的全部硬件特性,进行门级的时序仿真仍然十分重要,确保设计的QAM信号发生器的时序特性,以保证硬件器件的功能与设计一致。在QuartusII下打开项目文件,设置器件为EP1C6Q240C8,编译后进行时序仿真,其门级时序仿真波形如图6所示。

图4 正交幅度调制信号输出波形

图5 ModelSim模拟信号仿真和功能仿真结果

由图6可以看出,与图5功能仿真结果相比较,其功能仿真与时序仿真结果完全一致,产生输出QAM信号,表明设计的正确性。

QuartusII对ATOM网表文件进行适配,产生FPGA目标器件的编程与配置文件。最后锁定引脚,把.sof文件下载到目标器件,输出信号分别接入示波器,可以产生QAM信号输出,与仿真结果完全一致,达到设计要求。

5 结束语

基于DSP Builder的正交幅度调制信号实现方案,避免了VHDL编程的复杂性,而且又便于修改和扩充其功能,对实现正交幅度调制信号具有很好的借鉴意义。因此采用DSP Builder设计正交幅度调制信号简单快捷且方便可调,其输出特性和调制特性很好,使设计正交幅度调制信号变得非常简单和快捷,并且信号的参数可灵活调整。

[1] 董国伟,李秋明,赵 强,等.基于FPGA的直接数字频率合成器的设计[J].仪器仪表学报,2006(Z1):877-879.

[2]刘 晨,王森章.直接数字频率合成器的设计及FPGA实现[J].微电子学与计算机,2004,9(5):63-65.

[3] 樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2008.

[4] 潘 松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2004.

[5] 潘 松,黄继业,曾 毓.SOPC技术实用教程[M].北京:清华大学出版社,2005.

[6] 余晶晶,陶 成,贾怀义.基于FPGA与DDS技术的通用调制平台的研究[J].电测与仪表,2007(5):47-50.

[7] 赖昭胜,管立新.基于Dsp Builder的DDS实现及其应用[J].微计算机信息,2006,11(2):186-188.

[8]李志鹏,郭 勇,沈 军.基于DDS技术实现信号发生器[J].微计算机信息,2007,19(2):175-177.

[9] 周 媛,贾怀义.基于FPGA的全数字64QAM调制解调器设计[J].电视技术,2007(1):40-42.

[10]张 骞.基于ADL5385的128QAM发送器设计 [J].电子设计工程,2009,17(3):111-113.

[11]梁海丽,段吉海,游路路.1024QAM调制解调系统的FPGA 实现[J].电视技术,2007(4):31-32,35.