基于温备份技术的高可靠嵌入式控制器设计

陈敏涛,席 隆

(中国科学院光电研究院,北京100190)

随着航天技术的进步,空间科学实验的需求日益增多。我国已经发射了实践系列科学试验卫星[1],在神舟飞船上也进行了大量的空间科学实验。为了保证实验的成功,航天科技人员采用了多种可靠性技术以提高航天计算机系统的可靠性,如冷热备份技术、多数选举技术等。在我国的萤火一号探测器设计上,载荷配电器采用了热备份方式[2],而美国的 SERVIS-2卫星也使用了类似多数选举系统的容错技术实现高可靠的数据管理系统[3]。

然而,采用此类热备份技术保障系统可靠性的同时也带来了功耗过大等问题;而冷备份在切换后主系统中的关键数据和状态将会丢失,无法完成控制进程的继承。温备份技术可以使个别公用部件处于加电工作状态,定期地保存主系统运行中的关键数据和状态,当主系统发生故障并切换至备份系统后,备份系统即可迅速自主地完成恢复运行,是对热备份和冷备份冗余的改进[4],系统设计实现的关键在于采用高可靠存储器来保存关键数据。本文提出的新型温备份方案不但减少了高可靠存储器的使用,而且与标准温备份系统相比具有更高的可靠性。

1 系统功能和性能

空间科学实验控制器可提供以下4种功能[5-6]:

(1)对实验设备的控制功能。可对电机、继电器等进行控制,包括8路数字开关量输出、4路PWM输出。

(2)遥测功能,可对电压、电流、温度、压力、开关状态、数字量等提供实时遥测服务,包括8路12位采样率为200 KS/s的模拟采样、8路数字开关量的输入。

(3)数传和复接能力。能够为需要下传的大量数据(如视频图像等)提供数传和复接服务,包括2路LVDS信号的复接、2路UART和2路 SPI接口。

(4)控制科学实验进程的程序上载功能。空间科学实验控制器的程序可以在轨期间通过串行接口进行更新。

在保证控制器以上4种功能的基础上,本控制器还具有以下特性:(1)高可靠性。选用EP等级器件以减小器件故障率,采用新型温备份技术提高系统可靠性。(2)低功耗。选用低功耗器件并采用低功耗技术降低系统功耗,系统运行时最大功耗为0.4 W。(3)小体积。(4)可扩展性。FPGA内部使用ARM Coretex-M1处理器IP核可以使协处理器提升整个控制器的性能,使用以太网IP核扩展以太网接口等。

2 硬件设计

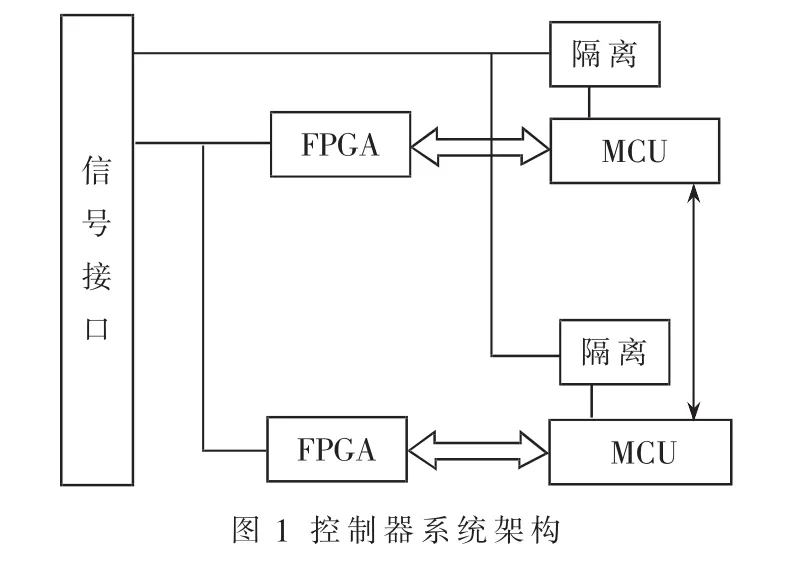

2.1 基于MCU与FPGA的控制器核心

控制器的核心采用了基于MCU与FPGA的系统架构,如图1所示。MCU负责实验进程的控制和数据的采集,包括串行通信、模拟信号(温度、压力等)的采集、数字开关信号的输入输出、PWM输出 (用于温度控制或电机驱动等实验执行设备);FPGA负责高速数字信号的复接与传输,其中使用了低压差分信号传输技术来传输信号。

MCU选用德州仪器公司的MSP430F249-EP,它具有4种低功耗模式,在最低功耗模式下只需0.1 μA的电流即可维持RAM中的内容,从低功耗模式切换回工作模式不超过1 μs。即便在工作模式下,MCU消耗的电流也仅为250 μA/MIPS。另外,该MCU具有存储器和丰富的外设,通用输入输出引脚可以配置为 UART、I2C、SPI串行通信接口,PWM输出和模数转换器的输入;同时,MCU可以通过JTAG和BSL两种方式进行程序下载,其中BSL方式采用了UART串行接口,适合于MCU在轨期间的程序上载。MCU选用了相对廉价的EP等级的器件,EP器件已通过AQEC标准(ANSI/GEIA STD-0002-1),该标准保证了EP器件达到了在军事、航空航天等严酷环境下的使用要求。在实践八号科学试验卫星的池沸腾实验中,MSP430F249-EP作为实验控制器成功地完成了预期的实验任务。

FPGA选用Actel公司基于Flash技术的超低功耗IGLOO系列M1AGL600V2。基于Flash技术的FPGA与基于SRAM技术的FPGA相比除了具有较高的可靠性 (如具有较高的对抗单粒子效应的特性)之外,在同等资源的情况下电池续航时间是基于SRAM技术的FPGA的8倍[7]。IGLOO系列FPGA独特的超低功耗Flash*Freeze模式可以将器件功耗降至5 μW。在该模式下,所有的时钟和FPGA内核的输入处于关闭状态,仅保持寄存器及SRAM中的内容,所有的引脚均处于高阻态。从Flash*Freeze模式切换回工作模式只需 1 μs。

MCU除通过1路SPI通道与FPGA进行通信之外,还通过通用输出引脚控制FPGA的超低功耗使能引脚使得FPGA进入或者退出超低功耗模式,从而控制FPGA进入工作状态或休眠状态。另外,两个MCU之间的通信使用增强并行口EPP协议,完成实验关键数据和进程信息的备份。该协议具有500 KB/s~2 MB/s的数据传输率和编程方便灵活等特点[8],可以满足备份的速率要求。

由于主系统与备份系统的接口信号都连在一条总线上,为了保证处于休眠和掉电状态的备份系统的引脚信号不影响总线上的信号,要求主备份系统的FPGA与MCU连在总线上的引脚必须处于高阻态。IGLOO系列FPGA所有的引脚在休眠和掉电状态下处于高阻态,而MSP430所有的引脚在休眠状态下则保持不变,因而在MCU与总线的连接中间需插入隔离电路,以保证备份系统的MCU不会影响总线信号。

2.2 可靠性设计

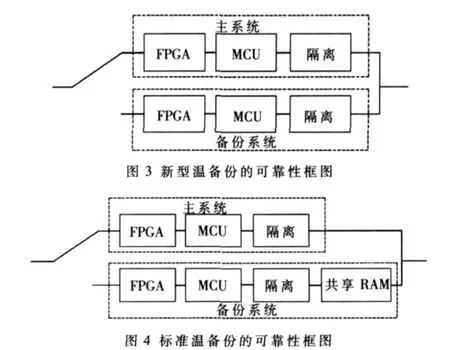

本文采用的新型温备份技术与标准的温备份技术不同,它没有使用共享RAM来定时存储实验关键数据,而是采用加电的备份系统MCU来进行存储。标准温备份系统架构如图2所示。备份系统在空闲状态下处于休眠状态,消耗极少的功耗。

新型温备份系统比标准温备份系统有更高的可靠性。使用旁联模型对两者进行任务可靠性建模,模型如图 3、图 4所示[9]。

假设转换装置可靠度为1,且系统各单元的寿命服从指数分布时,标准温备份可靠度其 中 λ1、λ2、λ3、λ4分 别 为 FPGA、MCU、隔离芯片和共享RAM的故障率。新型温备份的可靠 度 R2(t)=e-λ′t(1+λ′t),其 中 λ′=λ′1+λ′2+λ′3,λ′1、λ′2、λ′3分别是FPGA、MCU和隔离芯片的故障率。假设MCU与FPGA的故障率在休眠与掉电状态下相同、隔离芯片的故障率在加电与掉电状态下也相同,对基于两种不同温备份技术的系统可靠度进行比较后发现,基于新型温备份技术的系统可靠度随时间下降得较慢,即可靠性更高。

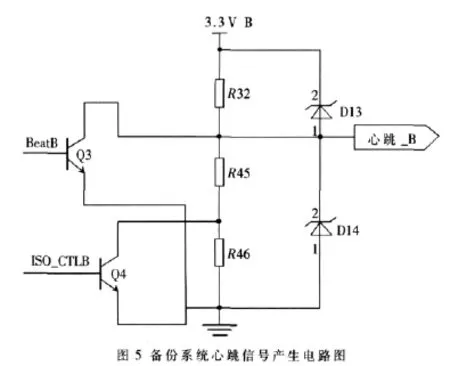

尽管旁联模型可以大大提高系统的可靠度,但是增加了故障检测与转换装置而加大了系统的复杂度,而且要求故障检测与转换装置的可靠度非常高,否则冗余带来的好处会被严重削弱。针对这一问题,本设计的故障检测采用的方法是检测两套系统的心跳信号及工作系统的下行数据的正确性。备份系统心跳信号的硬件电路如图5所示,BeatB信号是MCU的通用输出引脚产生的心跳信号,ISO_CTLB信号指示了MCU是处于备份状态或工作状态,根据三个电阻不同的电阻比值可以设定输出心跳信号的高低电平值,其中两个二极管的作用是保护内部电路。

转换装置通过对失效系统的断电来实现其功能;备份系统对主系统的电源进行监测。当备份系统发现主系统的供电电压降至逻辑低电平时,备份系统被激活进入工作状态,从Flash中读取实验关键数据和实验进程相关信息并接替实验控制任务。

2.3 供电系统设计

供电系统采用双通道的冗余设计,支持7~40 V的宽范围电压输入,为控制器提供了3.3 V、2.5 V和1.5 V的供电电压,系统框图如图6所示。为了保证高效率和小体积的平衡,第一级采用DC/DC电压转换器实现宽范围电压输入并保证较高的效率,第二级采用低压差线性稳压器进一步降压。主备份系统的通断电通过磁保持继电器进行控制。

3 软件设计

3.1 FPGA逻辑设计

FPGA实现的是数据复接功能,完成两路串行输入数据的复接并通过串行接口输出。复接器在FPGA中实现分为3个模块:串行输入模块、复接模块和串行输出模块,如图7所示。两路LVDS数据通过串行输入模块存储在相应的FIFO中,复接模块中的控制逻辑同步地取出1个或2个FIFO中的数据并通过复接单元复接后存入FIFO3,串行输出模块将FIFO3中的数据取出并发送。

3.2 MCU软件

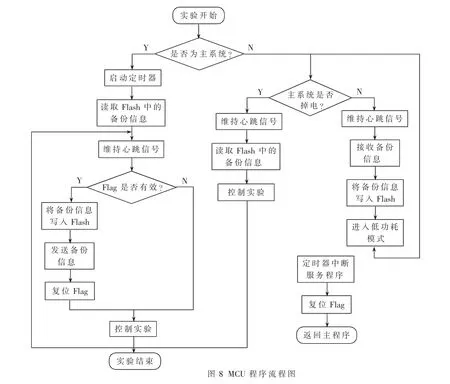

主系统的MCU与备份系统的MCU的软件功能有所不同:主MCU完成实验的控制、数据的采集处理以及向备份MCU定时备份实验关键数据及实验进程信息;备份MCU除定时接收主MCU发送的备份数据外,其余时间处于休眠状态。主备份MCU采用统一的程序设计,程序流程图如图8所示。主备份MCU按照特定输入引脚的电平值确定本系统是主系统或备份系统,从而运行不同的程序。

若主MCU出现暂时性故障,则主MCU内置的看门狗电路会重启主MCU,读入故障前的最后一次备份信息,继续实验。若主MCU出现永久性故障,则主系统进入掉电状态,而备份MCU读取Flash中的备份信息并接替主系统进行实验控制。

随着空间技术的进步,空间科学实验的需求必然会提升到一个新的高度,同时对科学实验设备的研发也提出了更高的要求。作为实验控制核心部件,高可靠控制器的设计仍将是十分重要的课题。本文利用MSP430与IGLOO系列FPGA的低功耗特性完成的新型温备份设计,在提高可靠性的同时保证了系统的低功耗,适用于未来空间科学实验的高可靠控制。

[1]蔡金荣,张立荣,周晓东.实践系列卫星空间环境探测的回顾[C].中国空间科学学会空间探测专业委员会第十九次学术会议,2006:423-427.

[2]安军社,陈晓敏,石俊峰,等.萤火一号探测器有效载荷数据管理器设计[J].空间科学学报,2009,29(5):486-489.

[3]HIHARA H,YMADA K,ADACHI M.CRAFT:an experimental fault tolerant computer system for SERVIS-2 satellite[EB/OL].http://pdf.aiaa.org/preview/CDReadyMIC SSC03_723/PV2003_2291.pdf.2003.

[4]王建峰,蒋轩祥.一种基于温备份的容错计算机的设计与实现[J].微电子学与计算机,2002(9):36-39.

[5]TANTIPHANWADI S.Spacecraft computers on the seastar satellite[EB/OL].http://microsat.sm.bmstu.ru/e-library/ccdh/Hard/ts-xii-6.pdf,1999.

[6]李春华,倪润立.中国返回式卫星与空间科学实验[J].空间科学学报,2009,29(1):124-129.

[7]Actel Corporation.Competitive programmable logic power comparison white paper[S].2008.

[8]符冬阳,贺贵明.增强并行口EPP协议及其应用[J].计算机应用,2001,21(10):62-63.

[9]曾声奎,赵廷弟,张建国,等.系统可靠性设计分析教程[M].北京:北京航空航天大学出版社,2000:32-36.